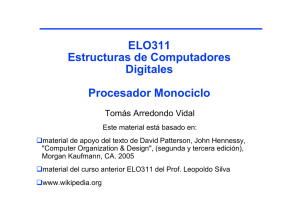

Diseño Procesador Monociclo

Anuncio

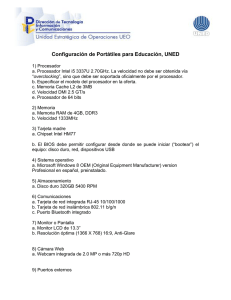

Diseño Procesador Monociclo 1 Procesador Monociclo Especificación de la arquitectura del repertorio de instrucciones y de las instrucciones que podrá ejecutar el procesador. Modelo Carga-Almacenamiento. 1 Procesador Monociclo Se implementará el procesador considerando las instrucciones: Suma, resta y slt (R) add rd, rs, rt sub rd, rs, rt slt rd, rs, rt Or inmediato (I) ori rt, rs, inm16 1 Procesador Monociclo Se implementará el procesador considerando las instrucciones: Carga lw sw y Almacenamiento (I). rt, inm16(rs) rt, inm16(rs) Bifurcación beq rs, rt, rótulo Salto (I). j incondicional. (J) rótulo 1 Procesador Monociclo Manual de Programación MIPS reducido. 1 Procesador Monociclo Trasferencias Lógicas add sub slt ori lw sw beq j R[rd] = R[rs] + R[rt]; PC = PC + 4 R[rd] = R[rs] – R[rt]; PC = PC + 4 R[rd] = R[rs] < R[rt] ? 1: 0 ; PC = PC + 4 R[rt] = R[rs] or zero_ext(Inm16); PC = PC + 4 R[rt] = MEM[ R[rs] + sign_ext(Inm16)]; PC = PC + 4 MEM[ R[rs] + sign_ext(Inm16) ] = R[rt]; PC = PC + 4 if ( R[rs] = = R[rt] ) PC = (PC +4)+[sign_ext(Inm16)]*4; else PC = PC + 4 PC = (PC +4)&0xF0000000 + add_26*4 6 Procesador Monociclo Recursos Combinacionales Unidad Aritmético Lógica AluCtr[2..0] Resultado Función ALU Binvert Operación 0 00 OpA & OpB and 0 01 OpA | OpB or 0 10 OpA + OpB add 1 10 OpA - OpB sub 1 11 OpA < OpB ? 1: 0 slt AluCtr OpA Resultado OpB 7 Procesador Monociclo Recursos Combinacionales Sumador que permita calcular PC+4 Suma PC PC+4 4 8 Procesador Monociclo Recursos Combinacionales Unidad Extensora ExtOp ExtOp Op. de 32 0 zero_ext(Inm16) 1 sign_ext(Inm16) Extensor Inm16 Op32 Operando de 32 bits 9 Procesador Monociclo Recursos Combinacionales Diseño Extensor lógico y aritmético ExtOp tierra bit 15 de Inm16 <15..0> Inm16 0 1 <31..16> de Op32 <31..0> de Op32 10 Procesador Monociclo Recursos Combinacionales Multiplexores CtrMux Out 00 S0 01 S1 10 S2 CtrMux S0 S1 S2 0 1 Out 2 11 Procesador Monociclo Recursos Combinacionales Multiplexores. Implementación. Di C1 0 0 1 1 C0 Out_i 0 Ai 1 Bi 0 Ci 1 Di Ci Out_i Bi Ai C1 C0 12 Procesador Monociclo Recursos Combinacionales Detector OpA OpB Igualdad Detector de Igualdad Equal B2 A2 B1 A1 A=B B0 A0 13 Procesador Monociclo Recursos Almacenamiento. Memorias Una memoria para almacenar las instrucciones (ROM). Una memoria para leer y escribir datos (RAM). Diseño inicial se elige tener recursos separados aunque podría ocuparse una sola memoria para datos e instrucciones. 14 Procesador Monociclo Recursos Almacenamiento. Memorias MemWr MemRd Inactivo MemRd Dirección Inactivo WrEn Rd AddrI Memoria Instrucciones Dout Dirección Din WrEn Rd AddrD Memoria Datos Dout 15 Procesador Monociclo Recursos Almacenamiento. Registros. Arreglo Registros RegWr R[Rw] = busW Rs 5 Rt 5 Rw 5 busW 32 Ra WE Rb Rw 32 Registros 32-bit busA = R[ Ra ] busA 32 busB = R[ Rb ] busB 32 16 Procesador Monociclo Diseño del arreglo de Registros. 17 Procesador Monociclo Recursos Registros. Almacenamiento. Contador de Programa WE RIn PC ROut 18 Procesador Monociclo Camino Datos. Determinación del próximo valor del PC. PC = PC + 4 WEPC Suma PC PC+4 PC 4 19 Procesador Monociclo Camino Datos. Determinación del próximo valor del PC. nPC_sel[1..0] Bifurcaciones y salto. 1 4 Inm16 nPCsel 00 PC = PC +4 01 PC = PC +4 + [Sign_ext(Inm16)]*4 10 PC = (PC +4)&0xF0000000+(addr_26*4) SigExt PC 0 2 << 2 (PC+4)[31..28] Addr26 0..1 20 Procesador Monociclo Camino de datos entre PC y Memoria de Programa. <31..26> COp WEPC "1" PC AddrI Rd busIR Memoria Instrucciones <5..0> Funct <15..0> Inm16 <15..11> Rd <20..16> Rt <25..21> Rs <25..0> add_26 21 Procesador Monociclo Unidad que determina la próxima instrucción a ejecutar, con la memoria de instrucciones. nPC_sel WEPC COp Funct <31..26> busIR 4 SigExt <<2 Inm16 (PC+4)[31..28] add_26 0..1 0 "1" 1 Rd AddrI 2 PC Memoria Instrucciones <5..0 > <25..21> rs <20..16> <15..11> rt rd <15..0> <25..0> add_26 Inm16 Rs 22 Procesador Monociclo Abstracción del diagrama anterior en un bloque que determina y decodifica la instrucción a ejecutar, y que además calcula la dirección de la próxima instrucción a realizar. nPC_sel Unidad de Instrucción <31..26> COp <15..0> Inm16 busIR <15..11> rd <20..16> rt <25..21> rs 23 Procesador Monociclo Camino de Datos para operaciones de tipo R. Arreglo de registros y la unidad aritmético lógica, para poder realizar las transferencias físicas que implementan las operaciones de suma y resta. AluCtr RegWr rs 5 rt 5 RW = rd 5 busW 32 Ra WE busA Rb 32 RW 32 Registros busB 32-bits W AluOut 32 24 Procesador Monociclo Modificaciones al camino de datos para poder procesar instrucciones inmediatas. RegDst RegWr 5 rd 0 rs rt 5 5 RW rt 1 busW Inm16 32 ExtOp AluSrc AluCtr busA WE Ra Rb Rw 32 Registros 32-bit 32 AluOut busB Extensor 32 Op32 0 1 25 Procesador Monociclo Camino de datos para acceder la memoria de datos. RegDst rd rt Inm16 RegWr ExtOp busA Ra WE 32 Rb 32 Registros RW 32-bits 32 RW busB 0 1 rs 55 0 rt 5 busW MemWr MemtoReg MemRd AluSrc AluCtr AluOut Addr 32 Op32 Extensor 1 WrEn Rd Dout Din Memoria Datos 0 1 26 Procesador Monociclo Detector de igualdad de busA y busB RegDst rd rt Inm16 0 1 RegWr rs 55 rt 5 WE Equal ExtOp 32 Ra Rb 32 Registros 32-bits 32 RW RW AluOut Igual busW Extensor MemWr MemtoReg MemRd busA busB 32 AluSrc AluCtr Op32 0 1 0 AddrD WrEn Rd Dout 1 Memoria Din Datos 27 Procesador Monociclo Simplificación Considerando unidades Unidad Instrucción nPC_sel WEPC COp Funct <31..26> busIR 4 SigExt <<2 Inm16 (PC+4)[31..28] add_26 0..1 0 "1" 1 Rd AddrI 2 PC Memoria Instrucciones <5..0 > <25..21> rs <20..16> <15..11> rt rd <15..0> <25..0> add_26 Inm16 Rs 28 Procesador Monociclo Simplificación Considerando unidades Unidad Registros RegWr RegDst rs 5 5 rt 1 rd 0 5 RW 32 Ra WE Rb 32 busA Rw 32 Registros 32 32-bit busB busW 29 Procesador Monociclo Simplificación Considerando unidades Unidad Operaciones Equal AluSrc AluCtr ExtOp busA Igual 0 busB Extensor Op32 1 AluOut busB Inm16 30 Procesador Monociclo Simplificación Considerando unidades Unidad Memoria MemWr MemRd MemtoR eg 0 AddrD Dout Memoria Datos 1 busW Din 31 Procesador Monociclo Esquema General WEPC nPC_sel COp Funct RegDst RegWr ExtOp Equal AluSrc AluCtr MemWr MemRd MemtoReg <31..26> <5..0 > 1 Inm16 4 (PC+4)[31..28] 2 Rd AddrI Memoria Instrucciones <25..21> 5 <20..16> rt <15..11> rd 1 5 R WE a Rb 32 busA RW 32 Registros 0 32-bit 0 Memoria Datos 1 Extensor add_26 Inm16 busW AddrD 32 busW 0..1 0 32 busB <15..0> <25..0> add_26 5 rs Igual SigExt*4 P C 4 busIR Alu Out "1" 0 Inm16 Dout Op32 Din 1 bus B 32 Procesador Monociclo Esquema General por unidad Unidad de Control AluSrc RegDst RegWr ExtOp AluCtr nPC_sel WEPC COp+ Funct Unidad de Instrucción rs rt rd MemWr MemRd MemtoReg Equal 32 busA 5 5 Unidad Registros 5 busW 32 Unidad AluOut de busB Operaciones 32 0 AddrD 1 Din Memoria Datos Dout Inm16 Reloj 33 Procesador Monociclo Transferencias físicas de datos. Cada transferencia lógica se implementa como un conjunto de transferencias físicas. Transferencia física es la descripción de un movimiento de datos entre los recursos del camino de datos. Muestra lo que sucede en el camino de datos. 34 Procesador Monociclo Transferencias físicas de datos. Movimientos son debidos a: Conexiones permanentes entre recursos Señales de control. Para cada instrucción: Se hace referencia a través de un mnemónico. Se anota la transferencia lógica. Y luego el conjunto de transferencias físicas que la desarrollan. 35 Procesador Monociclo Transferencias físicas de datos. Las transferencias físicas se agrupan de acuerdo a la unidad en que se realizan. Se muestran por líneas, pero toda la electrónica que las representa está funcionando en paralelo, y la información fluye en serie a través de los recursos. 36 Procesador Monociclo Transferencias físicas de datos. ADD: R[rd] ⇐ R[rs] + R[rt]; PC ⇐ PC + 4 AddrI=PC, busIR=MemInst[AddrI], PC=PC+4, Ra=rs, Rb=rt, RW=rd, busA=R[Ra], busB=R[Rb], AluOut=add(busA, busB), busW=AluOut, R[RW]=busW. SUB: Unidad Instrucción. Unidad Registros. Lectura. Unidad Operaciones. Unidad Registros. Escritura. R[rd] ⇐ R[rs] – R[rt]; PC ⇐ PC + 4 AddrI=PC, busIR=MemInst[AddrI], PC=PC+4, Ra=rs, Rb=rt, RW=rd, busA=R[Ra], busB=R[Rb], AluOut= sub(busA, busB), busW=AluOut, R[RW]=busW. Unidad Instrucción. Unidad Registros. Lectura. Unidad Operaciones. Unidad Registros. Escritura. 37 Procesador Monociclo Transferencias físicas de datos. SLT: R[rd] ⇐ R[rs] < R[rt] ? 1: 0 ; PC ⇐ PC + 4 AddrI=PC, busIR=MemInst[AddrI], PC=PC+4, Ra=rs, Rb=rt, RW=rd, busA=R[Ra], busB=R[Rb], AluOut=slt(busA, busB), busW=AluOut, R[RW]=busW. ORI: Unidad Instrucción. Unidad Registros. Lectura. Unidad Operaciones. Unidad Registros. Escritura. R[rt] ⇐ R[rs] | zero_ext(Inm16); PC ⇐ PC + 4 AddrI=PC, busIR=MemInst[AddrI], PC=PC+4, Unidad Instrucción. Ra=rs, RW=rt, busA=R[Ra], Unidad Registros. Lectura. Op32 = zero_ext(Inm16), AluOut=or(busA, Op32), Unidad Operaciones. busW=AluOut, R[RW]=busW. Unidad Registros. Escritura. 38 Procesador Monociclo Transferencias físicas de datos. LOAD: R[rt] ⇐ MEM[ R[rs] + sign_ext(Inm16)]; PC ⇐ PC + 4 AddrI=PC, busIR=MemInst[AddrI], PC=PC+4, Unidad Instrucción. Ra=rs, RW=rt, busA=R[Ra], Unidad Registros. Lectura. Op32 = signext(Inm16), AluOut=add(busA , Op32), Unidad Operaciones. AddrD=AluOut, Dout = MemDat[AddrD], Unidad Memoria Datos. busW=Dout, R[RW]=busW. Unidad Registros. Escritura. STORE: MEM[ R[rs] + sign_ext(Inm16)] AddrI=PC, busIR=MemInst[AddrI], PC=PC+4, Ra=rs, Rb=rt, busA=R[Ra], busB=R[Rb], Op32 = signext(Inm16), AluOut= add(busA , Op32), AddrD=AluOut, Din = busB, MemDat[AddrD]=Din. ⇐ R[rt]; PC ⇐ PC + 4 Unidad Instrucción. Unidad Registros. Lectura. Unidad Operaciones. Unidad Memoria Datos. 39 Procesador Monociclo Transferencias físicas de datos. BEQ: if ( R[rs] == R[rt] ) PC ⇐ (PC +4)+ sign_ext(Inm16)] *4 else PC ⇐ PC + 4 AddrI=PC, busIR=MemInst[AddrI], Ra=rs, Rb=rt, busA=R[Ra], busB=R[Rb], if (Equal) PC = (PC +4)+ sign_ext(Inm16)] *4 else PC=PC+4. Unidad Instrucción. Unidad Registros. Lectura. Unidad Operaciones. Unidad Instrucción. J UMP: PC ⇐ (PC +4)&0xF0000000+ add_26 *4 AddrI=PC, busIR=MemInst[AddrI], PC = (PC +4)&0xF0000000+ add_26 *4. Unidad Instrucción. Unidad Instrucción 40 Procesador Monociclo Transferencias físicas de datos. Valores Control Conceptuales que toman las Señales de nPC_sel: "+4","Branch","Jump" Unidad Instrucción. WEPC: "1" Escribe en registro PC. Unidad Instrucción. RegDst: “rt”, “rd” Unidad Registros. Lectura. ExtOp: “zero”, “sign” Unidad Operaciones. AluSrc: "busB","Op32" Unidad Operaciones. AluCtr: “add”, “sub”, “or”, “slt” Unidad Operaciones. MemWr: "1" Escribe en la memoria. Unidad Memoria Datos. MemRd: "1" Lee desde la memoria de datos. Unidad Memoria Datos. MemtoReg:"alu","mem" Unidad Registros. Escritura. RegWr: "1" escribe busW en el registro Unidad Registros. Escritura. especificado en RW. 41 Procesador Monociclo Valores de las señales de control para activar las transferencias lógicas. Valores que toman las señales de control para desarrollar las diferentes transferencias lógicas necesarias para cada instrucción. 42 Procesador Monociclo Valores de las señales de control para activar las transferencias lógicas. ADD: R[rd] ⇐ R[rs] + R[rt]; PC ⇐ PC + 4 nPC_sel = “+4”, WEPC =1, RegDst = "rd", AluSrc = "busB", AluCtr = “add”, ExtOp=∅, MemWr=0, MemRd=∅, Memtoreg="alu", RegWr=1. SUB: Unidad Instrucción. Unidad Registros. Lectura. Unidad Operaciones. Unidad Memoria Datos. Unidad Registros. Escritura. R[rd] ⇐ R[rs] – R[rt]; PC ⇐ PC + 4 nPC_sel = “+4”, WEPC=1 , RegDst = "rd", AluSrc = "busB", AluCtr = “sub”, ExtOp=∅, MemWr=0, MemRd=∅, Memtoreg="alu", RegWr=1. Unidad Instrucción. Unidad Registros. Lectura. Unidad Operaciones. Unidad Memoria Datos. Unidad Registros. Escritura. 43 Procesador Monociclo Valores de las señales de control para activar las transferencias lógicas. SLT: R[rd] ⇐ R[rs] nPC_sel = “+4”, WEPC=1 , RegDst = "rd", AluSrc = "busB", AluCtr = “slt”, ExtOp=∅, MemWr=0, MemRd=∅, Memtoreg="alu", RegWr=1. < R[rt] ? 1: 0 ; PC ⇐ PC + 4 Unidad Instrucción. Unidad Registros. Lectura. Unidad Operaciones. Unidad Memoria Datos. Unidad Registros. Escritura. ORI: R[rt] ⇐ R[rs] + zero_ext(Inm16); PC ⇐ PC + 4 nPC_sel = “+4”, WEPC =1, Unidad Instrucción. RegDst = "rt", Unidad Registros. Lectura. AluSrc = "Op32", ExtOp = “zero”, AluCtr = “or”, Unidad Operaciones. MemWr=0, MemRd=∅, Unidad Memoria Datos. Memtoreg="alu", RegWr=1. Unidad Registros. Escritura. 44 Procesador Monociclo Valores de las señales de control para activar las transferencias lógicas. LOAD: R[rt] ⇐ MEM[ R[rs] + sign_ext(Inm16)]; PC ⇐ PC nPC_sel = “+4”, WEPC=1 , Unidad Instrucción. RegDst = "rt", Unidad Registros. Lectura. AluSrc = "Op32", ExtOp = “sign”, AluCtr = “add”, Unidad Operaciones. MemRd=1, MemWr=0, Unidad Memoria Datos. Memtoreg="mem", RegWr=1. Unidad Registros. Escritura. +4 STORE: MEM[ R[rs] + sign_ext(Inm16)] ⇐ R[rt]; PC ⇐ PC + 4 nPC_sel = “+4”, WEPC =1, Unidad Instrucción. RegDst = ∅, Unidad Registros. Lectura. AluSrc = "Op32", ExtOp = “sign”, AluCtr = “add”, Unidad Operaciones. MemWr=1, MemRd=0, Unidad Memoria Datos. Memtoreg=∅, RegWr=0. Unidad Registros. Escritura 45 Procesador Monociclo Valores de las señales de control para activar las transferencias lógicas. BEQ: if ( R[rs] == R[rt] ) PC ⇐ (PC +4) + sign_ext(Inm16)] *4; else PC ⇐ PC + 4 if (Equal) nPC_sel=”Br”; else nPC_sel=”+4”; WEPC =1. RegDst = ∅, AluSrc = ∅, ExtOp = ∅ , AluCtr = ∅ , MemWr=0, MemRd=∅, Memtoreg=∅, RegWr=0. Unidad Instrucción. Unidad Registros. Lectura. Unidad Operaciones. Unidad Memoria Datos. Unidad Registros. Escritura J: PC ⇐ (PC nPC_sel = “Jmp”, WEPC=1 . RegDst = ∅, AluSrc = ∅, ExtOp = ∅ , AluCtr = ∅ , MemWr=0, MemRd=∅. Memtoreg=∅, RegWr=0. Unidad Instrucción. Unidad Registros. Lectura. Unidad Operaciones. Unidad Memoria Datos. Unidad Registros. Escritura +4)&0xF0000000+ add_26 *4 46 Procesador Monociclo Clk Retardo Registro Diagrama de tiempos para todas las instruccion es del procesador Valor anterior PC Nuevo valor PC Tiempo Acceso Memoria Instrucciones Valor anterior IR Nuevo valor IR Rs, Rt, Rd, Op, Inm16, add26 Tiempo Propagación Sumador Unidad de Instrucción Valor anterior PC+4 Nuevo valor PC+4 Retardo de Propagación en Unidad de Control Valores anteriores Señales de control Nuevos valores RegWr, RW, WEpc, AluCtr,.... Tiempo Acceso Arreglo Registros Valores anteriores busA, busB Nuevos valores busA, busB Propagación ALU Nuevos valores de AluOut y busW en ADD, SUB, ORI Valores anteriores AluOut, busW Tiempo Acceso Memoria de Datos Valor anterior Dout Propagación Mux Nuevos valores de Dout en Lw y M[Aluout] en Sw Valor anterior Nuevo valor bus W en Lw busW Propagación Mux Valor anterior Dirección de salto. Setup Registro y Skew del reloj. Nuevo valor Dirección de salto. Propagación Sumador y Mux Unidad de Instrucción Valor anterior Dirección de bifurcación Nuevo valor Dirección de bifurcación Propagación Detector igualdad 47 Procesador Monociclo Diseño de la Unidad de Control. En el modelo monociclo la unidad de control es una red combinacional que tiene como entradas el código de operación-funct y la condición Equal; y como salidas las señales de Control. Unidad de Control nPC_sel U. Instrucción Cop + Funct WEPC RegDst RegWr U. Registros Equal ExtOp AluSrc AluCtr MemWr MemRd U. Operaciones U. Memoria Camino de Datos Reloj MemtoReg U.Registros 48 Procesador Monociclo Diseño de la Unidad de Control. Tabla de verdad de la Unidad de Control Monociclo Op Bnegate Operación Decimal Binario and Ø 0 00 or Ø 1 01 add 0 2 10 slt 1 3 11 sub 1 2 10 49 Procesador Monociclo Diseño de la Unidad de Control. Tabla de verdad de la Unidad de Control Monociclo OP Funct Nemo. 000000 100000 R add 000000 100010 R sub 000000 101010 R slt 001101 ØØØØØØ I ori 100011 ØØØØØØ I lw 101011 ØØØØØØ I sw 000100 ØØØØØØ I beq 000010 ØØØØØØ J j 000000 100100 R and 000000 101010 R slt 50 Procesador Monociclo Diseño de la Unidad de Control. Tabla de verdad de la Unidad de Control Monociclo Op+funct Eq WEPC nPC_sel Ext Op Add Ø 1 00 Ø Sub Ø 1 00 Slt Ø 1 Ori Ø Load Alu Ctr Reg Dst Mem Wr Mem Rd Mem toReg Reg Wr 0 010 0 0 Ø 0 1 Ø 0 110 0 0 Ø 0 1 00 Ø 0 111 0 0 Ø 0 1 1 00 0 1 001 1 0 Ø 0 1 Ø 1 00 1 1 010 1 0 1 1 1 Store Ø 1 00 1 1 010 Ø 1 0 Ø 0 Beq 1 1 01 Ø Ø ØØØ Ø 0 Ø Ø 0 Beq 0 1 00 Ø Ø ØØØ Ø 0 Ø Ø 0 Jmp Ø 1 10 Ø Ø ØØØ Ø 0 Ø Ø 0 Entradas 13 Alu Src Salidas 13 51 1 SigExt* 4 Inm1 6 (PC+4) 4 2 <5..0 ><25..21 "1 busI " > rs R R <20..16 Addr d > rt IMemoria Instruc<15..11 ciones > rd 5 5 1 0 <15..0 > <25..0 > [31..28] R a R b 32 Op32 Eq WEPC nPC_sel Ext Op Add Ø 1 00 Ø Sub Ø 1 00 Slt Ø 1 Ori Ø Load Datos Di n 1 1 Dou t Alu Ctr Reg Dst Mem Wr Mem Rd Mem toReg Reg Wr 0 010 0 0 Ø 0 1 Ø 0 110 0 0 Ø 0 1 00 Ø 0 111 0 0 Ø 0 1 1 00 0 1 001 1 0 Ø 0 1 Ø 1 00 1 1 010 1 0 1 1 1 Store Ø 1 00 1 1 010 Ø 1 0 Ø 0 Beq 1 1 01 Ø Ø ØØØ Ø 0 Ø Ø 0 Beq 0 1 00 Ø Ø ØØØ Ø 0 Ø Ø 0 Jmp Ø 1 10 Ø Ø ØØØ Ø 0 Ø Ø 0 Entradas 13 Alu Src bus W Addr D Memoria bus B Inm16 Op+funct MemtoR eg 0 0 bus B Inm16 MemW MemR d r bus A R 32 Registros W 32-bit 32 3 bus2 W add_26 W E Extensor add_26 0.. 1 5 AluSrc AluCtr ExtOp Equal Reg Wr RegDs t Igual 4 P C 0 COp Fun <31..26> ct Al u O ut WEPC nPC_sel Salidas 13 52 Procesador Monociclo Diseño de la Unidad de Control. Tabla Resumen Unidad de Control Monociclo OP+Funct+Eq Control[12..0] Obs. 000000100000Ø 100Ø001000Ø01 Add 000000100010Ø 100Ø011000Ø01 Sub 000000101010Ø 100Ø111000Ø01 Slt 001101ØØØØØØØ 1000100110Ø01 Ori 100011ØØØØØØØ 1001101010111 Load 101011ØØØØØØØ 10011010Ø10Ø0 Store 000100ØØØØØØ1 101ØØØØØØ0ØØ0 Beq 000100ØØØØØØ0 100ØØØØØØ0ØØ0 Beq 000010ØØØØØØØ 110ØØØØØØ0ØØ0 Jmp 53 Procesador Monociclo Diseño de la Unidad de Control. La implementación de la unidad de control puede ser utilizando. En base a compuertas lógicas (función mínima). Dispositivos lógicos programables (por ejemplo: GAL). O mediante EPROM. 54