Introducción a las FPGA AUTOR: Cavallero, Rodolfo Antonio

Anuncio

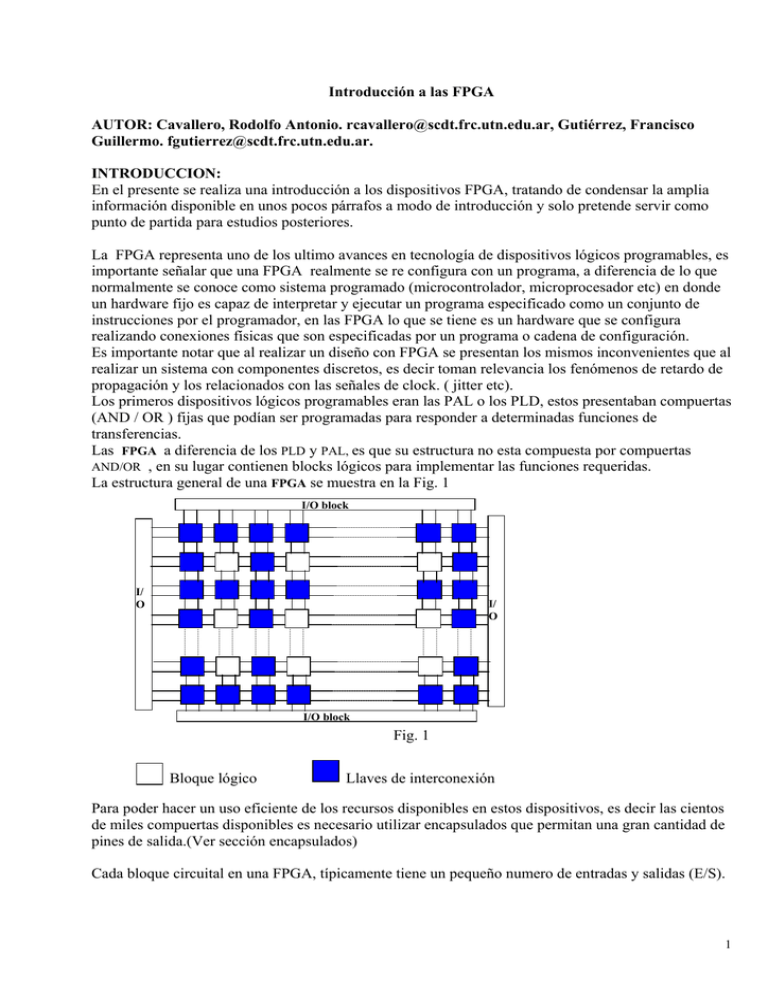

Introducción a las FPGA AUTOR: Cavallero, Rodolfo Antonio. [email protected], Gutiérrez, Francisco Guillermo. [email protected]. INTRODUCCION: En el presente se realiza una introducción a los dispositivos FPGA, tratando de condensar la amplia información disponible en unos pocos párrafos a modo de introducción y solo pretende servir como punto de partida para estudios posteriores. La FPGA representa uno de los ultimo avances en tecnología de dispositivos lógicos programables, es importante señalar que una FPGA realmente se re configura con un programa, a diferencia de lo que normalmente se conoce como sistema programado (microcontrolador, microprocesador etc) en donde un hardware fijo es capaz de interpretar y ejecutar un programa especificado como un conjunto de instrucciones por el programador, en las FPGA lo que se tiene es un hardware que se configura realizando conexiones físicas que son especificadas por un programa o cadena de configuración. Es importante notar que al realizar un diseño con FPGA se presentan los mismos inconvenientes que al realizar un sistema con componentes discretos, es decir toman relevancia los fenómenos de retardo de propagación y los relacionados con las señales de clock. ( jitter etc). Los primeros dispositivos lógicos programables eran las PAL o los PLD, estos presentaban compuertas (AND / OR ) fijas que podían ser programadas para responder a determinadas funciones de transferencias. Las FPGA a diferencia de los PLD y PAL, es que su estructura no esta compuesta por compuertas AND/OR , en su lugar contienen blocks lógicos para implementar las funciones requeridas. La estructura general de una FPGA se muestra en la Fig. 1 I/O block I/ O I/ O I/O block Fig. 1 Bloque lógico Llaves de interconexión Para poder hacer un uso eficiente de los recursos disponibles en estos dispositivos, es decir las cientos de miles compuertas disponibles es necesario utilizar encapsulados que permitan una gran cantidad de pines de salida.(Ver sección encapsulados) Cada bloque circuital en una FPGA, típicamente tiene un pequeño numero de entradas y salidas (E/S). 1 Los componentes disponibles de cada bloque varia de fabricante a fabricante. El block mas comúnmente utilizado es un lookup table (LUT), el cual contiene celdas de almacenamiento, las que se utilizan para implementar simples funciones lógicas. Cada celda es capaz de mantener un simple valor lógico, ya sea un 0 o un 1. Este valor almacenado (0 o 1) es obtenido luego a la salida de la celda de almacenamiento. En la Fig. 2 se observa la estructura de una LUT. Celdas de almacenamiento MUX MUX A f B x f 0 0 1 1 0 x f 0 A 1 B f 1 x X Fig. 2 Si se desea implementar una función booleana tal como la dada en la tabla de la Fig. 3a , x1 x1 0 0 1 1 x2 0 1 0 1 f 1 0 0 1 f1 0/1 0/1 _ _ f f = x1x2 + x1x2 f2 0/1 0/1 Fig. 3a x2 Fig. 3b entonces debemos programar las celdas de la LUT de la Fig. 3b, tal como se observa en la Fig. 3c x1 1 f1 0 f 0 f2 1 x2 Fig. 3c 2 En la Fig. 4 observamos una LUT de 3 entradas. En los chips comerciales de FPGA, las LUTs usualmente tienen entre 4 y 5 entradas, lo cual requiere entre 16 y 32 celdas de almacenamiento x1 x2 0/1 0/1 0/1 0/1 f 0/1 0/1 0/1 0/1 x3 Fig. 4. LUT de 3 entradas Las FPGAs, pueden tener circuitos extras, además de las LUTs , en cada bloque lógico. En la Fig 5 mostramos como un Flip Flop puede incluirse en un bloque lógico de una FPGA out D In1 In2 In3 Q LUT Select Ck Flip-Flop Fig. 5 – Inclusión de un FF en un bloque lógico Para la programación de las celdas LUT, así como también la asignación de las entradas y salida, existen varios metodos, los dos mas representativos son la tecnología Antifuse propuesta por la empresa ACTEL, y la tecnología SRAM utilizada por la mayoría de las otras empresas (XILINX, ALTERA, ATMEL etc).(Ver Configuración de la FPGA). 3 En cuanto a la tecnología antifuse es muy utilizada en aplicaciones espaciales, ya que una vez programada la FPGA la misma no puede ser preprogramada, además de presentar un grado alto de confiabilidad. Aquí es importante notar que esto plantea otra forma de trabajo para el desarrollos de sistemas basados en FPGA, muy diferente al normalmente adoptado en sistemas re programables. Dada la imposibilidad de reprogramar las configuraciones de las FPGA así como también su funcionalidad deben ser exhaustivamente comprobadas, debido a esto se ha invertido mucho tiempo y esfuerzo en el desarrollo de programas de simulación que permiten determinar con mucha exactitud el comportamiento del sistema. Recordemos que aquí se enfrenta el problema de los retardos asociados con las implementaciones clásicas de circuitos digitales de alta velocidad. En las FPGA basadas en SRAM esta restricción no es tan valida, pero la exactitud de los programas de simulación disponibles impone por optimización el uso de los simuladores. Además hay que tener en cuenta que cuando los sistemas crecen en complejidad se hace muy difícil la depuración de los mismos ya que no se cuenta con acceso directo a los distintos puntos de interés. En resumen la utilización correcta de los programas de simulación disponibles hacen acortar significativamente las horas de Debug necesariaso. En la Fig. 6 mostramos una FPGA que ha sido programada para realizar la siguiente función lógica _ f = x1.x2 + x2.x3 x3 f x1 x1 x2 f1 0 0 0 x2 0 1 0 f2 f1 0 1 1 f Fig.6 Sección de una FPGA programada Observemos detenidamente la Fig. 6, en ella podemos apreciar unos rectángulos (LUT) que contienen dos entradas (xi) y una salida (fi) y dentro de ellos la programación realizada. Unos rectángulos mas pequeños nos indican los terminales de entrada ( x1, x2, x3 ) y un terminal de salida (f), y están indicados con trazo continuo. Los rectángulos con trazo de línea de puntos no se utilizan. Por 4 otra parte vemos que existen interconexiones marcadas con X indicando con ello que no están realizadas. Las conexiones marcadas con son conexiones hechas. Observando atentamente podemos apreciar que: _ f1 = x1.x2 , f 2 = x2.x3 : con lo que _ f = x1.x2 + x2.x3 Encapsulados (Footprint) El encapsulado es la presentación física final de dispositivo, es el compartimiento que aloja la oblea de silicio que es el CI propiamente dicho. En el caso de los dispositivos FPGA normalmente se presenta la necesidad de disponer de un gran numero de entradas salidas, por lo que los encapsulados DIP no son una opción, además del problema del numero de pines de entrada salida se presenta el problema de las altas velocidades que pueden manejar las FPGA, performance que se vería seriamente afectada en caso de utilizar un encapsulado cuyos pines de conexión presentes altas inductancias parásitas. La evolución de las FPGA las lleva a encapsulados tipo PGA (pin grid array) o BGA (ball grid array). No es un detalle menor el considerar el tipo de encapsulado disponible al momento de seleccionar el dispositivo lógico programable a utilizar, ya que al aumentar el numero de pines el soldado del dispositivo al impreso se vuelve un problema critico. En el todos los casos el soldado se realiza con instrumental específicamente diseñado con tal fin, en el caso del BGA el problema mas fuerte radica en la verificación de la correcta soldadura del circuito integrado, ya que los pines se encuentran en la parte inferior del dispositivo y no es posible verlos directamente, para la verificación se utilizan maquinas de rayos X y otras técnicas complejas, y relativamente costosas. Demás esta decir que el uso de estos encapsulados prácticamente obligan a la utilización de circuitos impresos multicapas, otro inconveniente tecnológico a considerar. Se pueden obtener especificaciones de los distintos encapsulados disponibles directamente de la pagina de los fabricantes, o de las hojas de datos de los dispositivos. Configuración de la FPGA La forma de configurar la FPGA varia dependiendo de la tecnología adoptada, en caso de las FPGA basadas en tecnología atifuse las mismas son programadas una sola vez y haciendo uso de un programador dedicado. En el caso de la tecnología SRAM las FPGA leen su configuración interna de una memoria no volátil que es la que mantiene el programa. La lectura se realiza en forma serie, una vez finalizada la transferencia la FPGA se configura y comienza a funcionar. Esta carga se realiza en los POWER-UP o por un reset del dispositivo. En este campo para el uso de esta tecnología en la actividad espacial o militar se han incorporado técnicas de recarga del programa sin afectar el funcionamiento de la FPGA. Todo esto esa apuntado a conseguir que las FPGA basadas en tecnología SRAM sean utilizadas en lugares críticos, ya que el solo hecho de que su configuración dependa de un bit volátil genera cierta desconfianza en el medio. La memoria de configuración normalmente esta fabricada por el mismo fabricante de la FPGA, esta puede ser reemplazada por otro dispositivo mientras se respeten los protocolos de transferencia. Otro método de transferencia de configuración a la FPGA es a través del puerto JTAG. BIBLIOGRAFÍA Titulo: Fundamentals of Digital Logic with VHDL Design Autores: Stephen Brown, Zvonko Vranesic Ed. Mc Graw Hill www.xilinx.com www.altera.com www.actel.com 5