Clase

Anuncio

LAB 6

Máquinas Secuenciales

Laboratorio de Sistemas Digitales

ELO212

Primer Semestre de 2011

Objetivos Generales

Describir máquinas secuenciales sincrónicas y

asincrónicas.

Aplicar estrategias de modelado y asignación de

estados para sistemas secuenciales.

Comunicar la FPGA con el PC vía puerto serial.

Generar módulos de prueba para máquinas

secuenciales.

Módulo buart

`define CLK

50000000

module buart(rst, clk,

ld_tx_data, tx_data, tx_enable, tx, tx_empty,

uld_rx_data, rx_data, rx_enable, rx, rx_empty,

rx_err);

parameter

parameter

parameter

parameter

……….

endmodule

BAUD_RATE = 115200;

FRAME = 8;

// frame lenght 4 - 8.

PARITY = 0;

// 0: none, 1: odd, 2: even

STPBIT = 0;

// 0: 1 sb, 1: 2 sb

Reconocedor de Secuencias

Máquinas secuenciales

Hay básicamente dos tipos

de secuencia fija

contínuo

Reconcedor Secuencia 01 (1)

module rec01(clk, e, s, q);

input clk, e;

output s;

output reg [1:0] q;

assign s = (q == 2);

always @(posedge clk)

case (q)

0: if (!e) q <= 1;

1: if (e) q <= 2;

2,3: if (e) q <= 0; else q <= 1;

endcase

endmodule

Reconcedor Secuencia 01 (2)

En el sitio del curso se encuentra el módulo

mrec() que implementa el reconocedor

anterior:

instancia módulo rec01 (pero puede ser genérico)

instancia módulo buart()

Usa led para indicar reconocimiento

Reconcedor Secuencia 01 (3)

Uso del generador de señales con mrec()

usa S0 como señal de reloj

usa S1 como señal de entrada

entrada se captura con canto de subida

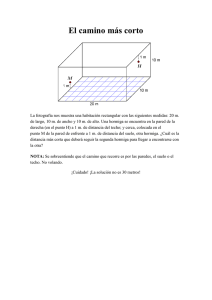

Cerebro de Hormiga (1)

Una hormiga busca la salida de un laberinto

La hormiga tiene 2 antenas (sensores)

Cada antena tiene 2 estados: 1 ó 0

El estado ‘uno’ indica contacto con un muro

El estado ‘cero’ indica que no hay contacto con un muro

(aire libre)

Desafío: proponer un algoritmo para sacar a la

hormiga del laberinto. El ejemplo aquí propuesto

considera que la hormiga mantiene la muralla a su

derecha, modifique según corresponda.

Cerebro de Hormiga (2)

r+l

r’l’

F

L

r’l’

r+l

Cerebro de Hormiga (3)

Motores

{4’b0, R, L, B, F}

Controlador

FPGA

Emulador

Laberinto - Hormiga

Sensores

{6’b0, ra, la}

Cerebro de Hormiga (4)

Cerebro de Hormiga (5)

`define

`define

`define

`define

`define

`define

`define

State_F 0

State_L 1

Antenna_L d[7]

Antenna_R d[6]

Action_F 8

Action_L 2

Reset d[4]

Cerebro de Hormiga (6)

module BasicAnt(clk, d, s);

input clk; input [7:0] d; output [3:0] s; reg State;

assign s = State == `State_F ? `Action_F : `Action_L;

always @ (posedge clk or posedge `Reset) begin

if (`Reset) State <= `State_F;

else

case (State)

`State_F:

if (`Antenna_R || `Antenna_L) State <= `State_L;

else State <= `State_F;

`State_L:

if (`Antenna_R || `Antenna_L) State <= `State_L;

else State <= `State_F;

endcase

endmodule

Cerebro de Hormiga (7)

En el sitio se encuentra un archivo ant.v

que implementa una hormiga de 2 estados

usando el simulador.

Trabajo Previo (1)

Reconocedor de P2 si P0 y P3 si P1 si switch

está en alto, o reconocedor de P4 si switch

está en bajo

P0: #grupo % 16,

P1:( ~P0+1)%16,

P2: rol sin dígito verificador 1er integrante %

16,

P3: (P2 + 3) % 16,

P4: Dado por el profesor.

Trabajo Previo (2)

Cerebro de hormiga

Diseñar un algoritmo que haga circular la hormiga

con la muralla al lado derecho o izquierdo según

el valor de un switch.

Mostrar estado en displays 7 segmentos, e indicar

mediante leds el estado de los sensores de la

hormiga.

En el Laboratorio

Revisión Actividades Previas

Verificar funcionamiento del cerebro de

hormiga

Demostrar funcionamiento del reconocedor

de secuencia

Diseñar un reconocedor continuo de palabras

del tipo LLLDL; ej. abc1d.