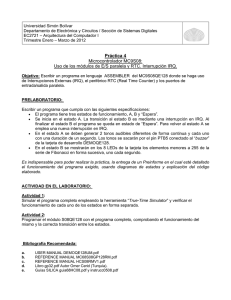

10-Interrupciones 414KB May 06 2014 10:03:02 PM

Anuncio

INTERRUPCIONES Ing. Julio César Doumecq – Prof. Asoc. Área Digitales – Fac. Ingeniería UNMDP, Mar del Plata, Argentina ©2011 1 INTERRUPCIONES Definición de interrupción Interrupciones en el µP 6800 Diagrama de flujo de interrup. Diagrama temporal de RES, IRQ, NMI Instrucciones WAI y SWI CI’s controladores de interrup. Repaso de E/S estándar E/S con uso de interrupciones Ing. Julio César Doumecq – © 2011 2 InterrupcionesDefinición Son el mecanismo más importante para vincular al µP con el mundo exterior Son similares a una subrutina Se diferencian por: - la forma en que se inician, - los datos que se guardan y - su desvinculación del programa principal De forma similar a la subrutina, al finalizar se regresa a la instrucción siguiente a la que estaba ejecutando el µP cuando recibió el pedido de interrupción Ing. Julio César Doumecq – © 2011 3 El proceso de atención de un pedido de interrupción Mapa de Memoria 6800 0000h Inicio Programa Principal XXXXh Instante de arribo del pedido IRQ de interrupción al µP Programa Principal (memoria de programa) Salto a la Rutina de Interrupción Retorno al Programa Principal YYZZh Subrutina de atención de interrupción RTI Instrucción final de subrutina de atención de IRQ Zona de vectores de interrupción IRQ YY ZZ FFF8h SWI NMI RES FFFFh Ing. Julio César Doumecq – © 2011 4 Vectores de Interrupción IRQ (Byte Alto) $FFF8 IRQ (Byte Bajo) $FFF9 SWI (Byte Alto) $FFFA SWI (Byte Bajo) $FFFB NMI (Byte Alto) $FFFC NMI (Byte Bajo) $FFFD RES (Byte Alto) $FFFE RES (Byte Bajo) $FFFF Ing. Julio César Doumecq – © 2011 5 Interrupciones en el µP 6800 Interrupciones por Hardware - RES: se usa para iniciar el µP o cuando es necesario “resetearlo” - IRQ: se activa por un nivel BAJO y es “enmascarable” (si bit I del CCR es “1”) - NMI: se activa por un flanco NEGATIVO, ignora el bit “I” del CCR Interrupciones por Software - SWI: interrupción por programa, es una subrutina “ampliada” - WAI: instrucción de espera de una interrupción por hardware. Inconveniente: detiene la ejecución del programa hasta que llega la interrupción Ing. Julio César Doumecq – © 2011 6 RES - Diagrama de flujo Ing. Julio César Doumecq – © 2011 7 IRQ - Diagrama de flujo Ing. Julio César Doumecq – © 2011 8 NMI - Diagrama de flujo Ing. Julio César Doumecq – © 2011 9 SWI - Diagrama de flujo Ing. Julio César Doumecq – © 2011 10 WAI - Diagrama de flujo SWI WAI NMI IRQ Ing. Julio César Doumecq – © 2011 11 Ahora veamos esto mismo en los diagramas temporales … (cambiamos de Presentación, después volvemos para ver el hardware) Ing. Julio César Doumecq – © 2011 12 CI Motorola MC6828 PIC: controlador de interrupciones priorizadas $FFF8,9 $FFE8,9 $FFEA,B $FFEC,D $FFEE,F $FFF0,1 $FFF2,3 $FFF4,5 $FFF6,7 13 Interior del PIC 6828 ¿Cuándo actúa el 6828? Si se detecta pedido de interrup. y: - R/W en ALTO, - VMA en ALTO, - A4 a A1 en 1100 ($C) y - A15 a A5 en $FFF ¿Cómo se establece el límite de prioridad? - R/W en BAJO, El PIC interpreta que se lo está seleccionando - VMA en ALTO y y las líneas A4 a A1 se toman como datos, definiendo el nivel de máscara de inhibición - A15 a A5 en $FFF 14 El CI de la PC actual 15 Cómo hace una PC para manejar más de 8 pedidos de IRQ? Pedidos de interrupción De esta forma se puede manejar hasta un máximo de 64 pedidos de interrupción por parte de dispositivos externos al µP. Ing. Julio César Doumecq – © 2011 16 Manejo de Entradas/Salidas mediante interrupciones Ing. Julio César Doumecq – © 2011 17 Repaso de E/S estándar E/S por puertos mapeados Æ sondeo o encuesta (“polling” - 6800) E/S por puertos dedicados (Intel) 18 E/S con interrupciones (µP Intel) Ing. Julio César Doumecq – © 2011 19 Esto es todo por hoy … Ing. Julio César Doumecq – © 2011 20