cbcb cbabc ax cacbca x abc cba x qn m qn m qn mx nqmqnm mnq x

Anuncio

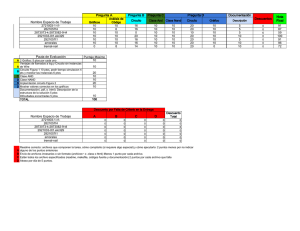

EJERCICIOS SEPTIEMBRE

1ª EVALUACIÓN

CF: STI

MODULO: AESI

PRIMERO

Escribe la tabla de verdad de las siguientes funciones (2 ptos).

X =ABC + AB (A ⋅ C )

X = ABC + AB C + ABC

X = (A + B )(A + B + C )C

X = RST (R + S +T )

X = MNQ ⋅ M N Q ⋅ MNQ

X = M + N +Q + M + N +Q + M + N +Q

X = A + B + C + ABC

X = AC + B C + A + C

X = A + BC (A + B + C ) + (B + C )(B + C )

F1 = a’b’c’ + a’b’c+ a’bc’ + abc’ + abc

F2 = (a+b’+c’) (a’+b+c) (a’+b+c’) (a+b’+c)

F3 = [(a’ + b) + c] + (a’ + b’)

F4 = {(a’ + b) [c(b+c’)]’} ([]’ niega todo lo que esta entre corchetes)

F5 = a’b’c’d’ + a’b’c’d + a’b’cd + a’bc’d’ + ab’c’d + ab’cd’ + ab’cd + abc’d + abcd

F6 = (a+b+c’+d’) (a+b’+c+d) (a’+b+c’+d) (a’+b+c’+d’) (a’+b’+c+d) (a’+b’+c’+d’)

F7 = abc + ab’c + abc’d

F8 = (a+b+c’)(a+b+c’+d)

F9 = (a+b+c)(a+b+d)(a’+b+c’)(c+d’)(b+d)

Dibuja el diagrama de tiempos.

Escribir las siguientes funciones según las formas canónicas (primera y segunda).

Simplifica por el método de Karnaugh.

Dibuja el circuito simplificado con puertas lógicas de 2 entradas.

Impleméntalo con multiplexores o demultiplexores.

SEGUNDO

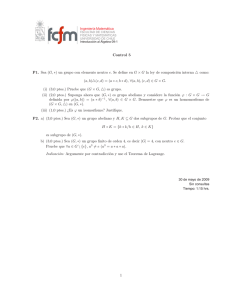

Se desea diseñar un circuito de control de una maquina trituradora. En esta maquina

existen dos sensores de llenado (S1 y S2), que determinan el nivel de los elementos a

triturar como se muestran en la figura:

Cuando la maquina se encuentra llena del todo, tienen que entrar en funcionamiento

ambos trituradores; cuando se encuentra medio lleno, solo tiene que funcionar uno de

ellos; mientras que si no se detecta ningún elemento a triturar, ambos motores se han de

EJERCICIOS SEPTIEMBRE

1ª EVALUACIÓN

CF: STI

MODULO: AESI

parar. Dicha maquina tiene un mecanismo de emergencia a través de un conmutador de

trituración, de tal forma que cuando está conectado la máquina opera según su

contenido, mientras que si esta desconectado, la máquina ha de pararse

independientemente de su contenido.

TERCERO

Determine en el circuito de un sistema con cuatro entradas y una salida, en la que esta

sea “1”, cuando el número binario aplicado a las entradas sea un número primo.

• Tabla de verdad y diagrama de tiempos.

• Ecuación lógica con minitérminos y maxitérminos.

• Simplifique la ecuación.

• Implementa el circuito con puertas lógicas universales.

• Implementa el circuito con un mutliplexor.

CUARTO

Determine en el circuito de un sistema con cuatro entradas y una salida, en la que esta

sea “1”, cuando el número binario aplicado a las entradas NO sea un número primo.

• Tabla de verdad y diagrama de tiempos (2 ptos)

• Ecuación lógica con minitérminos y maxitérminos. (2 ptos)

• Simplifique la ecuación. (2 ptos)

• Implementa el circuito con puertas lógicas universales. (2 ptos)

• Implementa el circuito con un mutliplexor (2 ptos).

QUINTO

El tipo de instrucciones (A o B) que se han de impartir al comienzo de un rally

dependerá de las características y propiedades de los coches.

Las variables que caracterizan a los vehículos y las condiciones de participación se

pueden resumir de la siguiente manera:

Los coches extranjeros con un motor superior a 2 litros deberán correr en Clase II, junto

con los coches nacionales. Si su cilindrada es menor, deben correr en Clase I. Tanto los

coches que compitan en la Clase I como en la II pueden estar equipados con arreglo a

las normas generales de la competición, o de acuerdo con unas normas especiales que

les permiten modificar el sistema de inyección. Los coches de Clase I pueden llevar

ruedas de serie o ruedas con un ancho especial.

Las instrucciones de tipo A se entregarán a los coches de Clase II que estén equipados

de acuerdo con las normas generales, y a los de Clase I que estén equipados según las

normas generales o lleven ruedas de serie. Al resto se les entregarán las instrucciones

del tipo B.

Definir, utilizando el menor número posible de circuitos integrados, el diagrama lógico

que, al aplicar a la entrada las condiciones de cada participante, permita activar una

señal luminosa cuando haya que entregarle las instrucciones de tipo A, y no se ilumine

cuando las instrucciones sean de tipo B

Diseñar el circuito con puertas NOR.

EJERCICIOS SEPTIEMBRE

1ª EVALUACIÓN

Donde las entradas son:

a = Nacionalidad del coche

• a= 1 Extranjero

• a = 0 Nacional

b = Cilindrada

• b = 1 > 2 litros

• b = 0 < 2 litros

c =Equipamiento

• c = 1 Normas específicas

• c = 0 Normas generales

d = Tipo de ruedas

• d = 1 Especiales

• d = 0 De serie

y las salidas

Clase

• 1 Clase II

• 0 Clase I

Tipo de instrucción.

• 1 Tipo A

• 0 Tipo B

CF: STI

A

0

0

0

0

0

0

0

0

1

1

1

1

1

1

1

1

B

0

0

0

0

1

1

1

1

0

0

0

0

1

1

1

1

MODULO: AESI

C

0

0

1

1

0

0

1

1

0

0

1

1

0

0

1

1

D

0

1

0

1

0

1

0

1

0

1

0

1

0

1

0

1

Clase Instrucción

SEXTO

Una máquina recreativa dispone, en la plataforma por la que discurre la bola, de cuatro

interruptores luminosos a, b, c y d que pueden ser activados con la bola en juego.

Diseñar un circuito con puertas NAND de dos entradas para que la máquina conceda

una bola gris cuando se pulsan los interruptores correspondientes a las combinaciones

binarias equivalentes a los números decimales 4, 5, 8, 9, 11, 13 ó 15. Se supone que los

interruptores que se activan quedan cerrados hasta que una nueva bola entra en juego.

SEPTIMO

Definir y ensayar un sistema de alarma al que se conectan cuatro detectores a, b, c y d.

El sistema se pondrá en marcha cuando se activen tres o cuatro detectores, o cuando se

active exclusivamente el sensor d, que es el de la puerta principal. Cuando no se active

ningún detector o se active uno solo ( a excepción del d), la alarma no actuará. Por

último si se activan los dos, el funcionamiento del sistema es indiferente, salvo que uno

de ellos sea el d, en cuyo caso el sistema se activará. Se supone que cuando se activa un

sensor la señal queda memorizada, es decir, permanece a nivel 1 hasta que se desactive

intencionadamente.

Implementar el circuito con el mínimo número de puertas NOR de dos puertas. (No hay

que definir el sistema de memorización de las señales de los detectores).

OCTAVO

Una máquina recreativa dispone, en la plataforma por la que discurre la bola, de cuatro

interruptores luminosos a, b, c y d que pueden ser activados con la bola en juego.

Diseñar un circuito para que la máquina conceda una bola gratis cuando se pulsan los

interruptores correspondientes a las combinaciones binarias equivalentes a los números

decimales 4, 5, 8, 9, 11, 13 ó 15. Se supone que los interruptores que se activan quedan

cerrados hasta que una nueva bola entra en juego.

EJERCICIOS SEPTIEMBRE

1ª EVALUACIÓN

•

•

•

•

•

CF: STI

MODULO: AESI

Tabla de verdad y diagrama de tiempos (2 ptos)

Ecuación lógica con minitérminos o maxitérminos. (2 ptos)

Simplifique la ecuación. (2 ptos)

Implementa el circuito con puertas lógicas universales (NAND de 2 entradas).

Implementa el circuito con un mutliplexor (2 ptos).

NOVENO

Diseña un sumador total.

• Tabla de verdad y diagrama de tiempos (2 ptos)

• Ecuación lógica con minitérminos y maxitérminos. (2 ptos)

• Simplifique la ecuación. (2 ptos)

• Implementa el circuito con puertas lógicas universales. (2 ptos)

• Implementa el circuito con un mutliplexor (2 ptos).

EJERCICIOS SEPTIEMBRE

1ª EVALUACIÓN

CF: STI

MODULO: AESI

PRIMERO

Realiza las siguientes operaciones (5ptos).

Pasa a complemento a uno y a complemento a dos los números (1/8 ptos cada una):

Ca1

Ca2

01010110

11010111

10110100

01100011

Haz las siguientes operaciones (0,5 ptos cada una) y descomplementa el resultado si es

negativo:

SUMA

11001110

+01001110

00110010

+00011110

00100010 – 00011101

00110011 - 01001110

00100010 – 00111101

00010011 - 01001110

00111100 - 00101010

01101110 - 01110001

Resta en

complemento a

uno.

Resta en

complemento a

uno la primera , y a

dos la segunda

Resta en

complemento a

dos.

EJERCICIOS SEPTIEMBRE

1ª EVALUACIÓN

CF: STI

MODULO: AESI

SEGUNDO

Realiza las siguientes operaciones (5ptos).

Pasa a complemento a uno y a complemento a dos los números (1/8 ptos cada una):

Ca1

Ca2

01010110

11010111

10110100

01100011

Haz las siguientes operaciones (0,5 ptos cada una) y descomplementa el resultado si es

negativo:

SUMA

01011010

+01000111

10110010

+01011110

00101010 – 00110011

00110011 - 01101000

00101010 – 00101101

00110011 - 01101101

00110011 - 00101110

01111111 - 01000001

Resta en

complemento a

uno.

Resta en

complemento a

uno la primera , y a

dos la segunda

Resta en

complemento a

dos.

EJERCICIOS SEPTIEMBRE

1ª EVALUACIÓN

CF: STI

MODULO: AESI

TERCERO

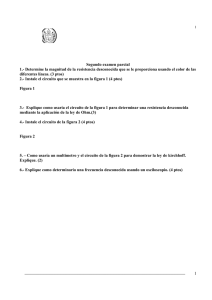

Diseña un flip-flop D y un flip-flop T, a partir de flip-flops J-K. (3pts)

Diseña un flip-flop J-K a partir de un flip-flop tipo D y un flip-flop T. (5pts)

CUARTO

Diseña un contador en anillo de 5 bits con flip-flops tipo D (Secuencia de estados, 1pto,

circuito 5ptos). Añade un circuito de reset de 1ms. (1pto). Finalmente, dibuja el

cronograma de funcionamiento, suponemos que el tiempo de propagación es 2/10

aproximadamente del ciclo de reloj. (2 ptos, detalle de dos ciclos de reloj 2 ptos)

QUINTO

Diseña un contador JOHNSON de 3 bits con flip-flops tipo D (Secuencia de estados,

1pto, circuito 5ptos). Añade un circuito de reset de 0.1ms. (1pto). Finalmente, dibuja el

cronograma de funcionamiento, suponemos que el tiempo de propagación es 2/10

aproximadamente del ciclo de reloj. (2 ptos, detalle de dos ciclos de reloj 2 ptos)

SEXTO

Diseña un dado electrónico síncrono con flip-flops, y dibuja el diagrama de tiempos y el

detalle cuando cambian todas las señales de salida con respecto el reloj.

Además, diseña el circuito de reset para un tiempo de 10ms, R= 10k, ¿Calcula C?

(10ptos).

SEPTIMO

Implementa un contador de 6 estados.

1. Tabla de estados. (2ptos)

2. Dibuja el diagrama de tiempos (2 ptos)

3. Dibuja en detalle cuando cambian todas las señales de salida con respecto el

reloj. El tiempo de propagación lo suponéis un 1/10 el tiempo de reloj. (1 pto)

4. Implementación del circuito (3ptos) y diseña el circuito de reset para un tiempo

de 5ms, R= 10k, ¿Calcula C? (1pto).

OCTAVO

Diseña un registro de desplazamiento a derecha entrada serie salida paralelo de 4 bits (

circuito 5ptos). Añade un circuito de reset de 2ms. (1pto). Finalmente, dibuja el

cronograma de funcionamiento, donde la secuencia de entrada serie es 0100111101,

suponemos que el tiempo de propagación es 2/10 aproximadamente del ciclo de reloj. (3

ptos, detalle de dos ciclos de reloj 2 ptos)

NOVENO

Diseña un registro de desplazamiento a izquierdas entrada serie salida serie de 4 bits (,

circuito 5ptos). Añade un circuito de reset de 2ms. (1pto). Finalmente, dibuja el

cronograma de funcionamiento, donde la secuencia de entrada serie es 0100111101,

suponemos que el tiempo de propagación es 2/10 aproximadamente del ciclo de reloj. (3

ptos, detalle de dos ciclos de reloj 2 ptos)

EJERCICIOS SEPTIEMBRE

1ª EVALUACIÓN

CF: STI

MODULO: AESI

EJERCICIOS SEPTIEMBRE

2ª EVALUACIÓN

CF: STI

MODULO: AESI

PRIMERO

Localiza los siguientes elementos de una placa base en los siguientes tarjetas

madres:

PUERTO PARALELO

PUERTO SERIE

VGA

DVI

HDMI

LAN (ETHERNET)

USB

FIREWIRE

WIFI

BLUETOOTH

AUDIO PORT

MIDI

TECLADO

RATON

MODEM

PUERTO DE JUEGOS

SLOTS DE MEMORIA

PCI EXPRESS x1

PCI EXPRESS x16

AGP

PCI SLOTS

ISA SLOTS

SATA (HDD)

SATA EXTERNO

ATA (HDD)

ATA EXTERNO

FDD

SOCKET MICRO

NORTBRIGDE

SOUTHBRIGDE

WESTBRIGDE

EASTBRIGGE

VENTILADOR CPU

VENTI. NORTB

VENTI SISTEMA.

BIOS

BATERIA

ATX 12V

ALIMENTACIÓN ATX

ALIMENTACIÓN AT

Fabricante

Placa

Socket

Asus

P5B Deluxe

SK775

Gigabyte

M55S-S3

AM2

Intel

D946-GZIS

SK775

MSI

K9AGM2 Series

AM2

EJERCICIOS SEPTIEMBRE

2ª EVALUACIÓN

CF: STI

MODULO: AESI

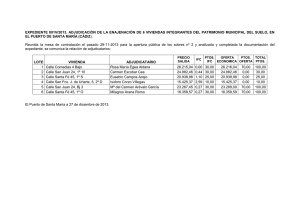

SEGUNDO

Supongamos una PDA que puede direccionar hasta X GB de memoria, y que

disponemos de las siguientes memorias:

• dispositivos de I/Os, situado en las primeras posiciones,

• memoria principal SDRAM,

• memoria externa a través de una tarjeta SD o CF,

• memoria FLASH donde se instala el SO que estará situado en las ultimas

direcciones de memoria.

Capacidad

PDA

I/O

SDRAM

SD

FLASH

PDA 1

512MB

PDA 2

1GB

PDA 3

2GB

PDA 4

4GB

PDA 5

8GB

8kB

96MB

48MB

128MB

16kB

128MB

192MB

512MB

32kB

256MB

1GB

512MB

64kB

384MB

3GB

512MB

64kB

512MB

4GB

1GB

Dibuja el mapa de memoria detallado (2ptos).

Calcula y refleja en el mapa donde empiezan y acaban cada bloque. (4ptos)

Diseña el circuito de selección (4 ptos) utilizando los siguientes dispositivos lógicos y

puertas lógicas discretas.

EJERCICIOS SEPTIEMBRE

2ª EVALUACIÓN

CF: STI

MODULO: AESI

TERCERO

Supongamos una PDA que puede direccionar hasta 8GB, y que disponemos de los

siguientes tipos de bloques de E/S (Entrada/salida o I/O) y/o memorias:

• 64kB en dispositivos de

E/S, situado en las

primeras posiciones,

• 256MB de memoria

principal SDRAM,

• hasta 4GB memoria

externa a través de

tarjeta SD,

• y 512MB de memoria

FLASH donde se instala

el SO que estará situado

en

las

ultimas

direcciones de memoria.

Si se utilizan los siguientes

chips de memoria:.

• Chip

SDRAM

de

128MB.

• Chip

FLASH

de

128MB.

Dibuja el mapa de memoria

detallado (2ptos).

Calcula y refleja en el mapa donde empiezan y acaban cada bloque y cada una de las

memorias. (4ptos)

Diseña el circuito de selección (4 ptos) utilizando los siguientes dispositivos lógicos y

puertas lógicas discretas.

EJERCICIOS SEPTIEMBRE

2ª EVALUACIÓN

CF: STI

MODULO: AESI

CUARTO

Relléname la siguiente ficha de mantenimiento de las realizadas en prácticas, e

indícame si es de tipo preventivo o correctivo, y si es software o hardware. (5ptos)

Acción:

Tipo

mantenimiento:

Material necesario:

Procedimiento:

de

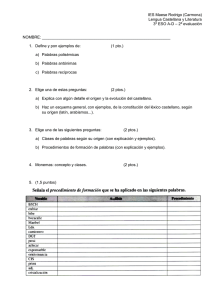

EJERCICIOS SEPTIEMBRE

3ª EVALUACIÓN

CF: STI

MODULO: AESI

PRIMERO

Un floppy disk de 1,44MB tiene 2 cabezales (numerados del 0 al 1), y 18 sectores

(numerados del 1 al 18). ¿Cuántos cilindros tiene? (1pto)

Si tenemos un disco duro de 2.1 GB de capacidad aproximadamente al cual se le hacen

cuatro particiones:

1

2

3

4

Sistema de archivos

FAT

FAT32

FAT

FAT32

Tamaño

8MB

64MB

256MB

512MB

Calcula el tamaño mínimo de los clusters en cada una de las particiones.

Calcula el número de clusters máximo utilizado en la partición.

SEGUNDO

Calcula la capacidad en GB de un disco duro con Cilindros, Cabezales y Sectores. Al

cual se le hacen cuatro particiones:

C

2112

2484

3309

4092

4969

6232

7480

1

2

3

4

H

16

Sistema de archivos

FAT

FAT

FAT

FAT32

S

63

GB

Tamaño

20MB

120MB

280MB

280MB

Calcula el tamaño mínimo de los clusters en cada una de las particiones.

Calcula el número de clusters máximo utilizado en la partición.

EJERCICIOS SEPTIEMBRE

3ª EVALUACIÓN

CF: STI

MODULO: AESI

SEGUNDO (2ptos)

¿Que periféricos se pueden conectar en cada uno de los conectores de la parte trasera de

la placa base?

TECLADO

RATON

ROUTER

MODEM

SWITCH

CRT

LCD TFT

MICROFONO

# PUERTO

1

2

3

4

5

6

7

8

ALTAVOZ

IMPRESORA

SCANNER

MEMORIA FLASH

HDD

WEBCAM

DVD/CD ROM

CAMARA VIDEO

PERIFERICOS

EJERCICIOS SEPTIEMBRE

3ª EVALUACIÓN

CF: STI

MODULO: AESI

TERCERO (10 ptos)

Da nombre a las diferentes tipos de redes por tamaño, y por topología, y describe el

soporte físico que se emplea para esa red.

Por otra parte, describe todos los elementos que componen las redes en árbol, bus, e

inalámbricas. Y asigna para la red en árbol todas las direcciones IP de todos los

elementos, utiliza las direcciones que más le corresponda: 192.168.0.X. 172.26.X.X, o

10.x.x.x

EJERCICIOS SEPTIEMBRE

3ª EVALUACIÓN

#

1

2

3

4

5

6

7

8

9

10

Tamaño

CF: STI

Topología Física

MODULO: AESI

Medio

EJERCICIOS SEPTIEMBRE

3ª EVALUACIÓN

CF: STI

MODULO: AESI

TERCERO (5 ptos)

Da nombre a las diferentes tipos de redes por tamaño, y por topología, y describe el

soporte físico (línea continua medio guiado, línea discontinua no guiado) que se emplea

para esa red.

Por otra parte, describe todos los elementos que componen las redes en árbol, bus, e

inalámbricas (línea discontinua).

EJERCICIOS SEPTIEMBRE

3ª EVALUACIÓN

#

1

2

3

4

5

6

7

8

9

10

Tamaño

CF: STI

Topología Física

MODULO: AESI

Medio