Informe - Escuela de Ingeniería Eléctrica

Anuncio

Universidad de Costa Rica

Facultad de Ingeniería

Escuela de Ingeniería Eléctrica

IE – 0502 Proyecto Eléctrico

Filtro Digital implementado en un PLD

Por:

Denic Danay Murillo Murillo

Noviembre del 2004

Filtro Digital implementado en un PLD

Por:

Denic Danay Murillo Murillo

Sometido a la Escuela de Ingeniería Eléctrica

de la Facultad de Ingeniería

de la Universidad de Costa Rica

como requisito parcial para optar por el grado de:

BACHILLER EN INGENIERÍA ELÉCTRICA

Aprobado por el Tribunal:

___________________

Ing. Roberto Rodríguez Rodríguez

Profesor Guía

___________________

Ing. Jorge Romero Chacón, PhD.

Profesor Lector

___________________

Ing. Federico Ruiz Ugalde

Profesor Lector

DEDICATORIA

A mi padre y a mi madre,

ya que su apoyo y cariño

me acompañarán por siempre.

A mis hermanos y hermanas,

por creer siempre en mí y en mis sueños.

A toda mi familia,

porque todos han sacrificado parte de su vida

y me la han regalado.

RECONOCIMIENTOS

A los Profesores:

Randolf Steinvort, Roberto Rodríguez,

Jorge Romero y Federico Ruiz,

por su ayuda en la elaboración de este proyecto.

A todos los profesores de la Escuela,

a las colaboradoras de la oficina de Secretaría

y a la Universidad, porque esta ha sido mi casa.

Y un reconocimiento muy especial a mi madre,

porque su sola presencia es razón para seguir adelante.

IE-0502

Filtro Digital Implementado en un PLD

i

ÍNDICE GENERAL

ÍNDICE DE FIGURAS.....................................................................................ii

ÍNDICE DE TABLAS......................................................................................iv

NOMENCLATURA.........................................................................................v

MARCAS REGISTRADAS.............................................................................vi

RESUMEN .....................................................................................................vii

CAPÍTULO 1: Introducción.............................................................................1

1.1

Objetivos ..........................................................................................................................2

1.1.1

Objetivo general...................................................................................................... 2

1.1.2

Objetivos específicos .............................................................................................. 2

1.2

Justificación .....................................................................................................................3

1.3

Metodología .....................................................................................................................3

CAPÍTULO 2: Desarrollo teórico.....................................................................5

CAPÍTULO 3: Diseño del Filtro.......................................................................9

3.1

3.2

El “codec”........................................................................................................................9

Diseño del Filtro a Implementar ....................................................................................11

3.2.1

Módulo de Reloj ................................................................................................... 13

3.2.2

Módulo de Canal................................................................................................... 14

3.2.3

Módulo “codec_top”............................................................................................. 17

3.2.4

Módulo de Filtro ................................................................................................... 19

3.2.5

Módulo “top_level”............................................................................................... 21

CAPÍTULO 4: Análisis de resultados.............................................................23

CAPÍTULO 5: Conclusiones y recomendaciones ...........................................32

BIBLIOGRAFÍA............................................................................................34

ANEXOS ........................................................................................................35

Anexo 1: Guía de Xilinx WebPack ................................................................................................35

Anexo 2: Código Fuente de los Módulos ......................................................................................45

Noviembre 2004

IE-0502

Filtro Digital Implementado en un PLD

ii

ÍNDICE DE FIGURAS

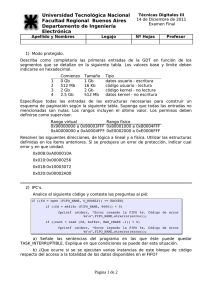

Figura 2.1 Arquitectura típica de un filtro digital FIR ................................................................ 5

Figura 3.1 Diagrama del Codec CS4222 .................................................................................. 10

Figura 3.2 Conexión del Codec al FPLD .................................................................................. 11

Figura 3.3 Vista del nivel más alto del chip de filtro diseñado................................................. 12

Figura 3.4 Vista del nivel más alto del Módulo de Reloj, llamado “clockGenerator” ............. 14

Figura 3.5 Vista del nivel más alto del Módulo de Canal, llamado “channel”......................... 16

Figura 3.6 Vista del nivel más alto del Módulo “codec_top”................................................... 19

Figura 3.7 Vista del nivel más alto del módulo de filtro, llamado “filtro”............................... 21

Figura 3.8 Vista externa del Módulo “top_level” ..................................................................... 22

Figura 4.1 Respuesta a una frecuencia de entrada de 44Hz...................................................... 23

Figura 4.2 Respuesta a una frecue ncia de entrada de 100Hz.................................................... 24

Figura 4.3 Respuesta a una frecuencia de entrada de 256Hz.................................................... 24

Figura 4.4 Respuesta a una frecuencia de entrada de 545Hz.................................................... 25

Figura 4.5 Respuesta a una frecuencia de entrada de 782Hz.................................................... 25

Figura 4.6 Respuesta a una frecuencia de entrada de 1.40kHz................................................. 26

Figura 4.7 Respuesta a una frecuencia de entrada de 2.0kHz................................................... 26

Figura 4.8 Respuesta a una frecuencia de entrada de 3.22kHz................................................. 27

Figura 4.9 Respuesta a una frecuencia de entrada de 3.85kHz................................................. 27

Figura 4.10 Respuesta a una frecuencia de entrada de 4.0kHz................................................. 28

Figura 4.11 Respuesta a una frecuencia de entrada de 4.35kHz............................................... 28

Figura 4.12 Sugerencia del uso de un único multiplicador....................................................... 30

Figura Anexo 1.1 Ventana para construir un nuevo proyecto. ................................................. 36

Figura Anexo 1.2. Construcción de nuevo proyecto, selección del dispositivo. ...................... 37

Figura Anexo 1.3. Creación de nuevo proyecto, agregar una nueva fuente (programa). ......... 38

Figura Anexo 1.4. Crear nuevo proyecto, agregar una fuente existente. .................................. 39

Figura Anexo 1.5. Proceso de implementación del diseño en el Spartan II. ............................ 41

Noviembre 2004

IE-0502

Filtro Digital Implementado en un PLD

iii

Figura Anexo 1.6. Creación del archivo .UCF de asignación de pines. ................................... 42

Figura Anexo 1.7. Proceso de programación del FPGA. .......................................................... 44

Noviembre 2004

IE-0502

Filtro Digital Implementado en un PLD

iv

ÍNDICE DE TABLAS

Tabla Anexo 1.1. Asignación de pines a los puertos ................................................................ 42

Noviembre 2004

IE-0502

v

Filtro Digital Implementado en un PLD

NOMENCLATURA

CPLD: Dispositivo lógico programable complejo (Complex Programmable Logic Device).

Codec: Dispositivo codificador/decodificador.

Fs: Frecuencia de muestreo (sample frecuency).

F: Frecuencia.

FPGA: Arreglo programable de compuertas de campo (Field Programmable Gate Array).

PLD: Dispositivo lógico programable (Programmable Logic Device).

TAP: Se llama así a cada una de las etapas del Filtro Digital.

Noviembre 2004

IE-0502

vi

Filtro Digital Implementado en un PLD

MARCAS REGISTRADAS

Verilog® es una marca registrada de Cadence Design Systems, Inc.

XILINX, FPGA, XC4005, XC2S200E son marcas registradas de Xilinx, Inc.

Todos los prefijos XC para la designación de productos, Xilinx Foundation Series y Xilinx

WebPack son marcas registradas de Xilinx, Inc. The Programmable Logic Company y The

Programmable Gate Array Company son marcas al servicio de Xilinx, Inc.

Digilab 2E y Digilent son marcas registradas de Digilent, Inc.

MATLAB® es una marca registrada de The MathWorks, Inc.

CIRRUS LOGIC ® y CS4222 son marcas registradas de Cirrus Logic, Inc.

XESS y XStend Board son marcas registradas de X Engineering Software Systems Corporation.

Todos los prefijos XS para la designación de productos son marcas registradas de X Engineering

Software Systems Corporation.

Noviembre 2004

IE-0502

vii

Filtro Digital Impl ementado en un PLD

RESUMEN

El filtro digital diseñado e implementado en este proyecto es sólo una pequeña muestra de la

amplia variedad de posibilidades que se tienen a la mano para poder desarrollar proyectos de

gran valor educativo utilizando PLD’s.

El interés por la manipulación de señales de audio surge de la importancia que tienen las

comunicaciones para la humanidad, y por esta razón es que se decidió aprovechar lo s recursos

que ofrecen estos dispositivos para introducir este tema que aún no se acaba de explorar.

Se invirtió tiempo en el manejo del lenguaje Verilog, de tal forma que los módulos programados

fueran 100% sintetizables. Además, la necesidad de estudiar el comportamiento de los filtros

digitales se hizo cada vez más notoria conforme se avanzaba en la programación de los mismos.

El “codec” y sus señales de control requirieron de mucho trabajo, esto para conseguir

implementar un protocolo de comunicación que respondiera a los requerimientos del circuito y

permitiera de esta forma el intercambio de información entre el PLD y el “codec”.

Una vez finalizadas cada una de las partes del proyecto, se unieron para probar su

funcionamiento en conjunto y afinar detalles, donde principalmente se trabajó con el algoritmo

del filtro digital (tipo FIR) y de esta forma cumplir con los objetivos establecidos.

Noviembre 2004

IE-0502

1

Filtro Digital Impl ementado en un PLD

CAPÍTULO 1: Introducción

La idea de este proyecto fue hacer un filtro digital utilizando los recursos de un PLD

(Dispositivo Lógico Programable), con lo cual se podría motivar a otros estudiantes a utilizar

estos dispositivos para probar sus diseños elaborados en el lenguaje Verilog.

Entre las ventajas que ofrece este circuito integrado, es que se tiene la facilidad de que es

reprogramable, esto es algo similar a construir un componente electrónico en software, con la

diferencia que lo que se tiene es hardware.

El objetivo final del proyecto, es permitirle a un usuario contar con un filtro que se adapta a las

características y especificaciones que él mismo determine.

Primeramente, el usuario debe tener claro qué tipo de filtro desea. Entiéndase por tipo de filtro si

es paso bajo, paso alto o paso banda. Para esto, se debe tener conocimiento del lenguaje de

MATLAB, donde es posible ingresar los parámetros como frecuencia de corte, ganancia y

frecuencia de muestreo. Este software le retorna al usuario los coeficientes que debe tener el

filtro para que funcione de la manera esperada.

Los parámetros deben ser ingresados por el usuario al PLD modificando el archivo fuente del

filtro para cambiar los coeficientes que correspondan y programando nuevamente el PLD.

Noviembre 2004

IE-0502

1.1

Objetivos

1.1.1

Objetivo general

•

2

Filtro Digital Impl ementado en un PLD

Diseñar e implementar un filtro digital en un PLD, con la facilidad de que al variar los

coeficientes de manera correcta en el filtro, este se comporte como un filtro paso bajo,

paso alto o paso banda.

1.1.2

Objetivos específicos

•

Diseñar un filtro tipo FIR, utilizando el lenguaje Verilog y el sintetizador de Xilinx.

•

Crear una interfaz entre el “codec” y el PLD, de manera que ambos se puedan comunicar

mediante un protocolo a establecer.

•

Transferir el archivo del sintetizador al PLD y probar su funcionamiento.

•

El filtro diseñado deberá funcionar para el caso en que la señal de entrada sea analógica y

su salida también sea de manera analógica, haciendo uso de un “codec” que viene

incluido en la tarjeta del PLD que se pretende utilizar.

•

Realizar las mejoras que correspondan y documentar todo el proceso.

Noviembre 2004

IE-0502

1.2

Filtro Digital Impl ementado en un PLD

3

Justificación

Lo que se pretende lograr con este proyecto, es promover el uso de los dispositivos electrónicos

como el CPLD o FPGA, los cuales pueden ser de gran ayuda y complemento en el aprendizaje y

comprensión de los circuitos digitales de una manera más rápida y efectiva. Esto le permitirá al

estudiante probar sus diseños sin necesidad de armar todo el circuito, el cual puede ser

complicado y hasta se podría incurrir en errores que den al traste con la motivación del

estudiante.

Para cumplir con esto, se pudo haber seleccionado cualquier circuito e implementarlo en uno de

estos dispositivos, pero se seleccionó el filtro digital porque es algo útil y que podría dar paso a

nuevos proyectos en el área de procesamiento de señales, tal como ecualizadores digitales y

manipulación de señales, tanto de audio como de video.

1.3

Metodología

Primeramente se estudió la documentación existente acerca de los FPGA y CPLD’s. Se buscaron

diferentes fuentes de información, tomando como fuente principal Internet. Además es

conveniente mencionar que es necesario poseer un nivel intermedio de programación en Verilog

para comprender el proyecto, debido a que es este el lenguaje que se utilizó para describir los

circuitos que se implementaron.

Noviembre 2004

IE-0502

Filtro Digital Impl ementado en un PLD

4

Después de haber estudiado lo anterior, se procedió a desarrollar proyectos pequeños utilizando

los dispositivos ya mencionados, esto con el fin de evacuar dudas y poner en práctica la

información recopilada.

Cuando se comprendió de manera general el funcionamiento de los PLD’s, se empezó a diseñar

el controlador necesario para manejar el “codec”. Ya diseñado e implementado en el PLD, se

hicieron pruebas para asegurar su buen funcionamiento.

Por otra parte, se diseñó y programó el filtro digital, y una vez finalizado, se modificaron los

controladores para poner a funcionar en conjunto todas las etapas.

Noviembre 2004

IE-0502

Filtro Digital Impl ementado en un PLD

5

CAPÍTULO 2: Desarrollo teórico

Un Filtro Digital es un sistema digital que es usado para filtrar señales en tiempo discreto. Las

señales en tiempo discreto son señales definidas en un instante discreto, monitoreadas cada

milisegundo, segundo, día, etc.

Para este proyecto, es necesario diseñar un Filtro Digital, es decir, que se debe iniciar un proceso

de diseño, síntesis e implementación de un filtro que al darle las excitaciones preescritas,

resulten las respuestas deseadas. Existen varios tipos de filtros digitales. Aquí se diseñó un filtro

tipo FIR con una arquitectura típica como el que se muestra en la Figura 2.1.

Figura 2.1 Arquitectura típica de un filtro digital FIR

Tomado de www.iberchip.org/IX/Articles/POST-082.pdf

En este caso, el filtro tiene 8 multiplicadores, 8 registros de “w” bits organizados en una

configuración de registros de desplazamiento (shift-register) y un sumador completo de ocho

Noviembre 2004

IE-0502

Filtro Digital Impl ementado en un PLD

6

datos de entrada, cada uno de “w” bits. Cada registro contiene la muestra anterior (unit sample

delay), y la salida de cada registro en una etapa (TAP) y es representada por x(n), donde n es el

número del TAP. Cada señal de salida de la etapa (delay inputs), es multiplicada por un

coeficiente h(n) y todos los productos son sumados para producir la salida del filtro. La

operación del filtro FIR de la Figura 2.1, de 8 TAP’s, puede ser representada por la ecuación:

8

y (n ) = ∑ x( n) h( n)

(2.1-1)

n =1

donde x(n) y h(n) son los valores de la n-ésima muestra de la señal de entrada y los coeficientes

del filtro respectivamente. En el caso específico del filtro diseñado en este proyecto, el número

de TAP’s es 15, y la cantidad de bits “w” de los registros es 20.

Una forma de simplificar el proceso de síntesis, es con el uso de herramientas como Verilog y el

WebPack de Xilinx de los cuales se hablará a continuación.

El lenguaje de programación de Verilog es de gran utilidad, ya que permite describir el

comportamiento de circuitos, realizar pruebas y analizar los diagramas temporales del mismo de

una manera muy sencilla y rápida.

El lenguaje de Verilog es un lenguaje de descripción de hardware que provee formas de

especificar un sistema digital con un amplio ámbito de niveles de abstracción. El lenguaje

soporta todos los conceptos de las etapas de diseño a nivel de comportamiento, y la siguiente

Noviembre 2004

IE-0502

Filtro Digital Impl ementado en un PLD

7

etapa de implementación a nivel estructural. Este lenguaje posee jerarquías de construcción,

permitiéndole al diseñador el control de la complejidad de la descripción.

Verilog fue originalmente diseñado en el invierno de 1983/84 como un producto con la

propiedad de verificación/simulación. Luego, muchas otras propiedades de análisis fueron

desarrolladas alrededor del lenguaje, incluyendo un simulador de falla y un analizador de

tiempos. Más recientemente, Verilog tiene también especificaciones de entrada para las

herramientas de síntesis lógica y por comportamiento.

Ahora el lenguaje ha sido estandarizado como IEEE standard #1364-1995 y está abierto para

cualquier herramienta en lectura y escritura.

Por otra parte, el WebPack de Xilinx es una herramienta mucho más poderosa, ya que por medio

de algoritmos logra traducir la descripción que se ha hecho en Verilog, a un esquemático cuya

simbología es de fácil comprensión y que eventualmente se podría construir utilizando

componentes digitales, o bien, pueden ser implementados y probados utilizando un Dispositivo

Lógico Programable ó PLD (por sus siglas en inglés).

Los PLD’s son dispositivos que proveen un espacio lleno de partes TTL y CMOS en un único

chip. Cada PLD contiene cientos de compuertas lógicas digitales interconectadas por

Noviembre 2004

IE-0502

Filtro Digital Impl ementado en un PLD

8

interruptores electrónicos internos. Los interruptores pueden ser reprogramados en cualquier

momento para crear un circuito lógico completamente diferente.

Existen dos tipos muy conocidos de PLD’s, el FPGA (arreglo programable de compuertas de

campo, por sus siglas en inglés) y el CPLD (dispositivo lógico programable complejo, por sus

siglas en inglés).

Noviembre 2004

IE-0502

Filtro Digital Impl ementado en un PLD

9

CAPÍTULO 3: Diseño del Filtro

3.1

El “codec”

Para la conversión analógico/digital y digital/analógico de la señal de audio, se utilizó un

“codec”, por lo que se debe tener conocimiento de cómo está conectado al PLD y su protocolo

de comunicación.

El “codec” que se utilizó en este proyecto fue el CS4222, de CIRRUS LOGIC, ya que forma

parte de los componentes con que cuenta la XStend Board V1.2. Este es un

codificador/decodificador de audio capaz de digitalizar dos señales analógicas con 20 bits de

resolución mientras genera simultáneamente dos señales analógicas desde los valores de los 20

bits (típicamente estas señales corresponden a los canales derecho e izquierdo de una señal de

audio en estéreo).

Opera con una alimentación de +5V y es de bajo consumo de potencia. Su comunicación es

serial, por tanto, la entrada como la salida son de una sola línea, es decir, que los 20 bits deben

transmitirse y recibirse uno a uno.

Para el caso específico del filtro, se necesita trabajar con los valores de los bits en forma

paralela, por lo que el circuito a diseñar debe contar con un conjunto de registros que conviertan

Noviembre 2004

IE-0502

Filtro Digital Impl ementado en un PLD

10

la entrada serial en un valor de 20 bits, y otro que convierta valores de 20 bits en una salida

serial.

Además de estos registros, el PLD necesita un circuito para leer y escribir en los mismos, y para

indicar cuando están llenos o vacíos. Es también necesario construir un circuito que detecte el

rebase positivo (overflow), y el rebase negativo (underflow) de los registros del PLD si éstos no

han sido leídos o escritos a tiempo.

Figura 3.1 Diagrama del Codec CS4222

Tomado de las hojas del fabricante, Cirrus Logic

A continuación se muestra la conexión entre el codec de la XStendBoard y la XS Board FPGA o

CPLD:

Noviembre 2004

IE-0502

Filtro Digital Impl ementado en un PLD

11

Figura 3.2 Conexión del Codec al FPLD

Tomado de las hojas del fabricante, XESS Corporation

En la Figura 3.2, la señal indicada como serial data out corresponde a la salida del ADC

(Analogic/Digital Converter), y serial data in indica la entrada al DAC (Digital/Analogic

Converter). Para efectos de este diseño, ambas señales serán llamadas sdout y sdin

respectivamente.

3.2

Diseño del Filtro a Implementar

Con esta información, ya se puede tener una idea general de las entradas y salidas que se

necesitan para poder manejar las señales del circuito del “codec”.

Por ejemplo, se sabe que el filtro necesita una señal de reloj, un reset y una entrada por donde se

recibe la salida del convertidor A/D (sdout). Se requiere también de una salida para enviar el

Noviembre 2004

IE-0502

Filtro Digital Impl ementado en un PLD

12

dato digital ya procesado al convertidor D/A (sdin), el cual da como resultado la señal analógica

filtrada. Además hay que agregar las salidas de control del “codec” (lrck, sclk, mclk, s), las

cuales se explicarán más adelante, junto con cada uno de los módulos que forman el circuito

integrado de filtro.

Figura 3.3 Vista del nivel más alto del chip de filtro diseñado

El bloque de la Figura 3.3 es la propuesta del circuito implementado, el cual se puede

descomponer en cinco módulos, que contienen los circuitos necesarios para realizar el filtrado:

•

Una unidad de reloj, encargada de sincronizar la transferencia de información entre el

PLD y el codec, genera una señal de reloj para los registros y las señales de selección de

canales derecho/izquierdo

•

Un módulo de canal que contiene los registros, control de lectura/escritura y un circuito

de detección del overflow/underflow (rebase positivo y negativo, respectivamente), se

encarga de controlar la transferencia de datos entre el “codec” y el filtro

Noviembre 2004

IE-0502

•

13

Filtro Digital Impl ementado en un PLD

El módulo “codec_top”, que contiene el módulo de reloj y dos módulos de canal

(estéreo), para hacer las conexiones entre ellos y así tener lista la interfaz del “codec” con

el filtro

•

El filtro, que realiza y ejecuta el algoritmo de filtrado digital tipo FIR

•

Un módulo “top-level” o “superior”, que combina el módulo codec_top con el módulo

del filtro para completar el circuito

A continuación se analiza cada uno de los módulos y su función.

3.2.1

Módulo de Reloj

Se encarga de coordinar todas las señales de control de todos los demás módulos,

sincronizándolos entre sí. Como el “codec” sólo puede trabajar con relojes de frecuencias entre

1.014 a 25.6 MHz, fue necesario construir un pequeño módulo para bajar la frecuencia del reloj

que posee la tarjeta del FPGA Spartan IIE, cuya frecuencia es de 32 MHz. Así, la nueva

frecuencia del reloj utilizado es de 16 MHz aproximadamente, con lo que se consigue una

frecuencia de muestreo de 48 KHz, suficiente para manipular señales de audio.

Las entradas y salidas de este módulo se definen a continuación:

clk: Esta es la entrada del reloj principal.

reset: Esta entrada inicializa el contador del generador de reloj. Sincroniza el circuito.

mclk: Esta salida es el reloj master para el chip.

sclk: Es el reloj para sincronizar la transferencia serial de datos entre el PLD y el “codec”.

Noviembre 2004

IE-0502

Filtro Digital Impl ementado en un PLD

14

lrck: Esta salida controla la activación del circuito de canal izquierdo y derecho en el “codec” y

el PLD.

bit_cntr: Estas salidas indican el bit actual que ha sido transmitido y recibido en las líneas de

datos.

subcycle_cntr: La duración de cada bit de dato serial es dividido en cuatro fases, y estas salidas

indican la fase actual.

Figura 3.4 Vista del nivel más alto del Módulo de Reloj, llamado “clockGenerator”

3.2.2

Módulo de Canal

Este módulo recibe los datos seriales desde el “codec” ADC para almacenarlos en un registro de

desplazamiento hasta completar el dato de 20 bits. Una vez estable el contenido de este registro,

queda disponible en formato paralelo para que sea leído por el filtro.

Por otro lado, este módulo recibe la salida del filtro en formato paralelo para ser transmitida al

“codec” DAC en forma serial.

Noviembre 2004

IE-0502

Filtro Digital Impl ementado en un PLD

15

Las entradas y salidas de este módulo se definen a continuación:

clk: Entrada de reloj principal.

reset: Esta entrada sincroniza e inicializa el canal.

chan_on: Un “nivel alto” en esta entrada activa el canal. Esta entrada es usualmente controlada

por el selector de canal “left/right”.

bit_cntr: Estas entradas informan al canal del índice del bit de dato serial que está siendo

transmitido y recibido.

chan_sel: Un “nivel alto” en esta entrada habilita la interfaz que permite que los registros sean

leídos y escritos. (Note que esta señal no controla el selector de canal “left/right”).

rd: Un “nivel alto” en esta entrada, saca el valor guardado en el registro conectado al ADC.

wr: Un “nivel alto” en esta entrada escribe un nuevo valor en el registro conectado al DAC.

adc_out: Los bits guardados en el registro ADC son sacados en paralelo a través de estas

salidas.

dac_in: El registro DAC es cargado en paralelo con los bits que pasan a través de estas entradas.

adc_out_rdy: Esta salida se pone en nivel alto después de que todos los bits han sido colocados

desde el “codec” al registro ADC.

adc_overrun: Esta salida se pone en nivel alto si un nuevo dato serial es agregado dentro del

registro ADC antes de que el contenido anterior haya sido leído a través de las salidas en

paralelo.

Noviembre 2004

IE-0502

16

Filtro Digital Impl ementado en un PLD

dac_in_rdy: Esta salida va a nivel alto después de que todos los bits en el registro DAC han sido

tomados por el “codec”.

dac_underrun: Esta salida va a nivel alto si el registro DAC empieza a enviar datos al “codec”

antes de que estos hayan sido escritos a través de las entradas en paralelo.

sdin: El dato serial para el “codec” DAC es enviado a través de esta salida. (Note que esta salida

toma su nombre del pin al que está conectada en el chip del “codec”; esta no es una entrada).

sdout: El dato serial desde el “codec” ADC es introducido a través de esta entrada. (Note que

esta entrada toma su nombre del pin al que está conectada en el chip del “codec”; esta no es una

salida).

Figura 3.5 Vista del nivel más alto del Módulo de Canal, llamado “channel”

Noviembre 2004

IE-0502

3.2.3

17

Filtro Digital Impl ementado en un PLD

Módulo “codec_top”

Combina el módulo “clockGenerator” con dos módulos “channel”. La instancia del

“clockGenerator”, u0, recibe un reloj de 16 MHz aproximadamente, y genera el “master clock”,

“left/right clock”, y “serial shift clock” para el “codec”.

Las instancias de “channel”, u_left y u_right son las correspondientes a los canales izquierdo y

derecho del “codec” , respectivamente. Estos módulos están activos , cada uno por separado,

durante una mitad del periodo del “left/right clock”. Además tiene un indicador de error

producido por rebase positivo y negativo para la interfase total del “codec”. El error es reportado

si cualquiera de los canales reporta un error.

Las entradas y salidas de este módulo se definen a continuación:

clk: Esta es la entrada del reloj principal.

reset: Entrada sincrónica que inicializa los dos módulos de canal y el generador de reloj.

lrsel: Esta entrada selecciona entre el canal derecho o izquierdo para las operaciones de

lectura/escritura en paralelo.

rd: Un “nivel alto” en esta entrada, saca el valor guardado en el registro de desplazamiento

seleccionado conectado al ADC.

wr: Un “nivel alto” en esta entrada escribe un nuevo valor en el registro de desplazamiento

seleccionado conectado al DAC.

ladc_out, radc_out: Los bits guardados en los registros de desplazamiento izquierdo/derecho

del ADC, son leídos afuera en paralelo a través de estas salidas.

Noviembre 2004

IE-0502

Filtro Digital Impl ementado en un PLD

18

ldac_in, rdac_in: Los registros de desplazamiento del DAC son cargados en paralelo con bits a

través de estas entradas.

ladc_out_rdy, radc_out_rdy: Estas salidas van a “nivel alto” después de que todos los bits han

sido desplazados desde el “codec” hasta el registro izquierdo/derecho del ADC, respectivamente.

adc_overrun: Esta salida va a “nivel alto” si un nuevo dato serial es desplazado dentro del

registro de desplazamiento derecho o izquierdo del ADC antes de que el viejo contenido haya

sido leído afuera a través de las salidas paralelas.

ldac_in_rdy, rdac_in_rdy: Estas salidas van a “nivel alto” después de que todos los bits del

registro de desplazamiento izquierdo o derecho del DAC, han sido desplazados al “codec”,

respectivamente.

dac_underrun: Esta salida va a “nivel alto” si algún registro de desplazamiento izquierdo o

derecho del DAC empieza a enviar datos al “codec” antes de que haya sido escrito a través de las

entradas en paralelo.

mclk: Esta salida es el reloj maestro para el “codec”.

sclk: Esta salida es el reloj para sincronizar la transferencia serial de datos entre el PLD y el

“codec”.

lrck: Esta salida controla la activación del circuito del canal izquierdo y derecho en el “codec”.

sdin: Los datos seriales para el “codec” DAC son enviados a través de esta salida.

sdout: Los datos seriales enviados desde el “codec” ADC son desplazados a través de esta

entrada.

Noviembre 2004

IE-0502

Filtro Digital Impl ementado en un PLD

19

Figura 3.6 Vista del nivel más alto del Módulo “codec_top”

3.2.4

Módulo de Filtro

Dentro de este módulo es donde se reciben los datos de los canales izquierdo y derecho para ser

sometidos al proceso de filtrado (algoritmo FIR), y una vez que completa todas las operaciones,

pone en “nivel alto” la salida tx_right o tx_left según corresponda, para indicar que está listo

para recibir un nuevo dato.

El filtro trabaja con el reloj original de 32MHz del FPGA Spartan IIE. No está de más recordar

que se construyó un módulo para disminuir la frecuencia de este reloj a la mitad, debido a las

limitantes presentadas por el “codec”.

Noviembre 2004

IE-0502

Filtro Digital Impl ementado en un PLD

20

Este módulo no cuenta con una señal de inicialización o “reset” debido a que el tipo de algoritmo

utilizado no lo requiere.

Las entradas y salidas de este módulo se definen a continuación:

ladc_out: Esta entrada proviene del registro de desplazamiento que almacena la salida del canal

izquierdo del “codec” ADC.

radc_out: Esta entrada proviene del registro de desplazamiento que almacena la salida del canal

derecho del “codec” ADC.

ladc_out_rdy: Esta señal indica al filtro cuándo el dato del canal izquierdo está listo para ser

leído.

radc_out_rdy: Esta señal indica al filtro cuándo el dato del canal derecho esta listo para ser

leído.

reloj: Entrada de reloj para sincronizar el filtro con los otros módulos.

lrck: Esta entrada recibe una señal que indica cuál de los dos canales debe ser leído por el filtro.

Dicha señal proviene del módulo “clockGenerator”.

rdac_in: Salida que envía los datos del registro de 20 bits del canal derecho, al módulo

“channel” para que dicho módulo los pase de manera serial al “codec” DAC.

ldac_in: Salida que envía los datos del registro de 20 bits del canal izquierdo, al módulo

“channel” para que dicho módulo los pase de manera serial al “codec” DAC.

tx_left: Salida para indicar que se han realizado las operaciones sobre el dato del canal izquierdo

y está listo para ser transmitido.

Noviembre 2004

IE-0502

21

Filtro Digital Impl ementado en un PLD

tx_right: Salida para indicar que se han realizado las operaciones sobre el dato del canal derecho

y está listo para ser transmitido.

Figura 3.7 Vista del nivel más alto del módulo de filtro, llamado “filtro”

3.2.5

Módulo “top_level”

Contiene el módulo reloj, cuya única función es la de reducir la frecuencia del reloj principal a la

mitad. Además tiene un módulo “codecTop” y un módulo “filtro”. El módulo “top_level” se

encarga de conectar cada uno de estos módulos como corresponde, y se encarga de controlar la

señal de lrsel, que indica sobre cuál de los canales se está trabajando, y las señales rd y wr, que

son las señales de lectura y escritura a los registros de desplazamiento del módulo “channel”.

Este módulo coordina sus acciones sobre las señales de control gracias a que recibe las señales

radc_out_rdy, ladc_out_rdy, ldac_in_rdy, rdac_in_rdy, tx_left y tx_right. Estas señales

indican procesos que ya han sido finalizados y le comunican al “top_level” que los diferentes

módulos están listos para un nuevo proceso.

Noviembre 2004

IE-0502

22

Filtro Digital Impl ementado en un PLD

A continuación se describe cada uno de los puertos I/O:

reloj_in: Es la entrada de reloj al circuito.

rst: Señal de inicialización del sistema.

sdout: Esta entrada es la salida del “codec” ADC, donde envía los datos de manera serial.

s[0]: Salida de overrun.

s[1]: Salida de underrun.

lrck: Salida que indica cuál de los canales debe ser manejado.

mclk: Salida de reloj para el sistema.

reloj_out: Esta salida de reloj tiene la misma frecuencia del reloj de entrada.

sclk: Esta salida es el reloj para sincronizar la transferencia serial de datos entre el PLD y el

“codec”.

sdin: Esta salida es la entrada del “codec” DAC, por donde recibe el dato de manera serial.

Figura 3.8 Vista externa del Módulo “top_level”

Noviembre 2004

IE-0502

Filtro Digital Impl ementado en un PLD

23

CAPÍTULO 4: Análisis de resultados

Las pruebas realizadas al circuito implementado muestran resultados aceptables, como se

mostrará más adelante, y abren el camino para quienes quieran investigar sobre las

comunicaciones digitales, donde se podría pensar en proyectos que permitan el procesamiento de

señales no sólo de audio, sino también de video, y la creación de nuevos algoritmos que hagan

más eficiente la manipulación de las mismas.

A continuación se muestran las señales de entrada (señal 2->) y salida (señal1->) del filtro

digital FIR comportándose como filtro paso banda. Se realizó un barrido de frecuencia para

observar su comportamiento, que en teoría debería permitir el paso de señales cuya frecuencia

sea mayor a 300Hz e inferior a 4.8kHz.

Figura 4.1 Respuesta a una frecuencia de entrada de 44Hz

Noviembre 2004

IE-0502

Filtro Digital Impl ementado en un PLD

24

La señal de entrada tiene una magnitud de aproximadamente 500mV y no se varió durante todo

el barrido. Como se puede ver en las figuras, el ruido fue un factor que estuvo presente durante

todas las pruebas y resultó imposible eliminarlo por completo y en algunas frecuencias se

presentaba con mayor magnitud que en otras.

Figura 4.2 Respuesta a una frecuencia de entrada de 100Hz

En esta figura se puede observar como la salida del filtro comienza a permitir el paso de la

señal. Hasta este momento, la salida no era audible pero sí observable en el osciloscopio.

Figura 4.3 Respuesta a una frecuencia de entrada de 256Hz

Noviembre 2004

IE-0502

Filtro Digital Impl ementado en un PLD

25

Figura 4.4 Respuesta a una frecuencia de entrada de 545Hz

Figura 4.5 Respuesta a una frecuencia de entrada de 782Hz

Noviembre 2004

IE-0502

Filtro Digital Impl ementado en un PLD

26

Figura 4.6 Respuesta a una frecuencia de entrada de 1.40kHz

Figura 4.7 Respuesta a una frecuencia de entrada de 2.0kHz

Noviembre 2004

IE-0502

Filtro Digital Impl ementado en un PLD

27

Figura 4.8 Respuesta a una frecuencia de entrada de 3.22kHz

Figura 4.9 Respuesta a una frecuencia de entrada de 3.85kHz

Noviembre 2004

IE-0502

Filtro Digital Impl ementado en un PLD

28

Figura 4.10 Respuesta a una frecuencia de entrada de 4.0kHz

En este punto del barrido, la salida todavía era audible. Al hacer un ligero aumento en la

frecuencia de la señal de entrada, ya no fue posib le escuchar la salida, aunque esta realmente

desapareció por completo en el osciloscopio hasta que alcanzó una frecuencia de 4.35kHz

aproximadamente.

Figura 4.11 Respuesta a una frecuencia de entrada de 4.35kHz

Noviembre 2004

IE-0502

Filtro Digital Impl ementado en un PLD

29

Una etapa importante del diseño del filtro, fue la obtención de los coeficientes para los diferentes

tipos. Aquí se utilizó una herramienta de MATLAB llamada Filter Design, en donde se

introducen las características del filtro y esta retorna los valores de los coeficientes en decimal.

Estos coeficientes, proporcionados por MATLAB, deben ser normalizados con respecto al de

mayor magnitud y luego, de acuerdo a la resolución que se desea de los mismos (# de bits), se

multiplica el vector normalizado por

(2 n −1)

en caso que existan coeficientes negativos, o

2

solamente por ( 2 n − 1) si todos los coeficientes son positivos, donde n es el # de bits. Para este

caso específico n = 6 . Se considera suficiente ya que los resultados de los experimentos

resultaron satisfactorios.

Otro factor importante a analizar es el tiempo. La frecuencia de muestreo del “codec” es cercana

a los 48000Hz, y de acuerdo al teorema de Nyquist sobre muestreo, con esa frecuencia se puede

muestrear señales de 24000Hz (por encima de la frecuencia audible) o menos, según la fórmula

Fs > 2 ∗ F , donde Fs es la frecuencia de muestreo, y F es la frecuencia de la señal muestreada.

Por lo tanto se dice que para el objetivo de este proyecto de manipular señales de audio, la Fs es

más que suficiente.

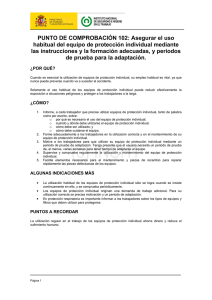

Una de las conclusiones expone la posibilidad de mejorar el diseño del filtro, esto porque el que

se ha mostrado en este trabajo tiene un multiplicador por cada TAP, lo cual compromete gran

Noviembre 2004

IE-0502

30

Filtro Digital Impl ementado en un PLD

parte de los recursos del FPGA. Como se ha mencionado en este apéndice, el tiempo no es factor

crítico, lo que daría oportunidad de diseñar un único multiplicador para realizar las operaciones

en cada una de las etapas (TAP´s).

Para visualizar mejor esta idea, se muestra la Figura Apéndice 1.1, en donde se puede observar

que se cuenta con un único módulo Multiplicador y un único módulo Sumador. Con esto se

consigue reducir la cantidad de hardware (circuitería), sacrificando velocidad del filtro.

Figura 4.12 Sugerencia del uso de un único multiplicador

Tomado de www.iberchip.org/IX/Articles/POST-082.pdf

Noviembre 2004

IE-0502

Filtro Digital Impl ementado en un PLD

31

Los PLD’s pueden ser un complemento importante de los cursos de electrónica digital y servir

de motivación en la búsqueda de nuevos circuitos, que sirvan para el desarrollo de soluciones

innovadoras dentro de un mercado que evoluciona día con día.

Noviembre 2004

IE-0502

Filtro Digital Impl ementado en un PLD

32

CAPÍTULO 5: Conclusiones y recomendaciones

•

Se diseñó un filtro tipo FIR utilizando el lenguaje Verilog que permitió la descripción de

la gran mayoría del circuito por comportamiento, ya que algunas partes debieron ser

descritas de manera estructural.

•

La interfaz creada entre el “codec” y el PLD fue posible mediante un protocolo de

comunicación que se estableció, y que permitió la transferencia de datos entre ellos.

•

El archivo que contiene la descripción de todo el circuito se sintetizó por medio de las

herramientas de Xilinx y luego fue transferido al PLD, lo que permitió realizar pruebas

para verificar su funcionamiento.

•

El filtro diseñado en este proyecto funciona para señales de entrada analógicas y señales

de salida también analógicas. Esto es posible gracias al uso de un “codec” y a la interfaz

de éste con el PLD.

•

El sintetizador de Xilinx junto con los PLD’s, son herramientas importantes que pueden

ayudar a los estudiantes a comprender con mayor facilidad los circuitos digitales y su

funcionamiento, esto porque se pueden implementar circuitos rápidamente y probar su

funcionamiento sin necesidad de manipular muchos componentes, lo que disminuye

considerablemente las posibilidades de incurrir en errores de tipo técnico.

•

Promover el uso de los PLD’s como un complemento de los cursos de electrónica digital.

Noviembre 2004

IE-0502

•

33

Filtro Digital Impl ementado en un PLD

La arquitectura expuesta en este proyecto emplea un área considerable de hardware

(recursos del FPGA), por lo que se puede pensar en diseñar una arquitectura que use

menor área, ya que la velocidad no es un factor crítico (ver Apéndice 1).

•

Que el estudiante conozca más acerca de los protocolos de comunicación existentes, le

permitiría trabajar en proyectos complejos y de gran utilidad en materia de tecnologías de

información.

•

Agregar en el laboratorio de circuitos digitales, un experimento que incluya el uso de un

PLD para darle al estudiante una herramienta más de diseño.

•

Fomentar el uso del lenguaje Verilog, pero que el estilo de programación vaya orientado

de manera tal que sea posible sintetizar los circuitos con la herramienta de Xilinx.

Noviembre 2004

IE-0502

34

Filtro Digital Impl ementado en un PLD

BIBLIOGRAFÍA

Libros:

1. Van den Bout, D. “The Practical Xilinx ® Designer Lab Book”, Prentice Hall, Estados

Unidos, 1998.

2. Thomas, D., Moorby, P. “The Verilog® Hardware Description Language”, 3ra

Edición, Kluwer Academic Publisher, Estados Unidos, 1996.

Páginas web:

1. “DigiLab 2E Reference Manual”, www.digilentinc.com

2. “Spartan-IIE 1.8V FPGA Family: Complete Data Sheet”, www.xilinx.com

3. “XStend Board V1.2 Manual”, www.wess.com

4. “20-Bit Stereo Audio Codec with Volume Control, CS4222” www.cirrus.com

5. “DISEÑO

DE

FUNCIONES

DSP

USANDO

VHDL

Y

CPLDs-FPGA”

www.iberchip.org/IX/Articles/POST-082.pdf

Noviembre 2004

IE-0502

Filtro Digital Impl ementado en un PLD

35

ANEXOS

Anexo 1:

Guía de Xilinx WebPack

Descripción en VeriLog y programación del PLD

A continuación se mostrará una breve descripción de cómo programar un PLD utilizando la

herramienta de Xilinx WebPack.

Para empezar, se debe seleccionar un lenguaje de programación para la descripción de

Hardward, entre los que están Verilog y VHDL.

Una vez que se tiene suficiente conocimiento del mismo, es recomendable que se elabore un

pequeño programa con su respectivo test o prueba, y si la simulación “corre” como se esperaba,

se procede a utilizar el archivo (sin el test), en el programa de “Project Navigator”. Para hacerlo

siga los siguientes pasos:

1. Abra la ventana de Project Navigator.

2. Seleccione File - New Project.

3. Escriba el nombre de la carpeta del proyecto (ver Figura Anexo 1.1).

4. El “Top-Level Module Type” se selecciona en HDL si se va a utilizar un lenguaje de

descripción de Hardware.

Noviembre 2004

IE-0502

Filtro Digital Impl ementado en un PLD

36

Figura Anexo 1.1 Ventana para construir un nuevo proyecto.

5. Al presionar siguiente, se debe indicar la familia del dispositivo, su nombre, el

encapsulado y su grado de velocidad, así como también el lenguaje de simulación que se

va a utilizar, y luego presione “Siguiente” (ver Figura Anexo 1.2).

Noviembre 2004

IE-0502

37

Filtro Digital Impl ementado en un PLD

Figura Anexo 1.2. Construcción de nuevo proyecto, selección del dispositivo.

6. Si ya se tienen el o los archivos que se desean sintetizar, presione “Siguiente”, donde

aparecerá una ventana con la opción de “Add Source” (ver Figura Anexo 1.4), pero si

aún no tiene el programa escrito, puede escribirlo directamente en el “Project Navigator”

marcando la opción de “N ew Source” (ver Figura Anexo 1.3).

Noviembre 2004

IE-0502

Filtro Digital Impl ementado en un PLD

38

7. Una vez seleccionadas y añadidas la(s) fuente(s), aparecerá la ventana de la Figura

Anexo 1.5. Presione “Siguiente” y compruebe que la información introducida durante el

proceso es la correcta, luego presione “Finalizar”.

Figura Anexo 1.3. Creación de nuevo proyecto, agregar una nueva fuente (programa).

Noviembre 2004

IE-0502

39

Filtro Digital Impl ementado en un PLD

Figura Anexo 1.4. Crear nuevo proyecto, agregar una fuente existente.

Una vez que se han realizado los pasos anteriores, se procede a efectuar la síntesis del circuito

que se haya descrito. Para explicar mejor la manera cómo debe realizarse este proceso, se

mostrará un ejemplo de un circuito para implementarlo en el FPGA Spartan II, de Xilinx, el cual

Noviembre 2004

IE-0502

40

Filtro Digital Impl ementado en un PLD

consiste en un marcador de pulsos de reloj por medio de un led. La descripción en VeriLog del

circuito se muestra en la Lista Anexo 1.1.

Ya cargada la descripción en la aplicación de Project Navigator, se puede observar en la ventana

de Processes for Source varias opciones. Lo que interesa en este punto es implementar el circuito

en el FPGA, por lo que selecciona la opción Implement Design (ver Figura Anexo 1.5).

Lista Anexo 1.1. Programa fuente para la descripción en VeriLog de un circuito marcador de

pulsos.

module ledSpartan(clk, reset, led);

input clk,

reset;

output led;

reg

[23:0]cont;

assign led=cont[23];

always @(negedge clk)

begin

if(reset)

cont<=0;

else

cont<=cont+1;

end

endmodule

Noviembre 2004

IE-0502

41

Filtro Digital Impl ementado en un PLD

Figura Anexo 1.5. Proceso de implementación del diseño en el Spartan II.

Cuando finaliza el proceso de implementación, se pueden observar las advertencias y/o errores

en caso que existan. Además, es necesario realizar la asignación de pines, que consiste en

asignarle a cada puerto del circuito diseñado, el número de pin que corresponda de acuerdo a la

función de dicho puerto. Para esto, se debe seleccionar Assign Package Pins para crear un

archivo UCF, el cual contiene la información de los pines (ver Figura Anexo 1.6).

Noviembre 2004

IE-0502

42

Filtro Digital Impl ementado en un PLD

Para este ejemplo, los puertos son clk, reset y led, y deben asignarse de la siguiente manera:

Tabla Anexo 1.1. Asignación de pines a los puertos

Reset

P15

Led

P69

Clk

P80

Donde P15 es el pin #15 del Spartan y el pin #2 es el pin del puerto paralelo.

Figura Anexo 1.6. Creación del archivo .UCF de asignación de pines.

Noviembre 2004

IE-0502

Filtro Digital Impl ementado en un PLD

43

Después de esto, se debe pasar a la fase final, que consiste en generar un archivo de

programación, el cual será transmitido, en este caso, al Spartan II, por medio del puerto paralelo

de la computadora.

Conectados los dispositivos, el proceso que debe seleccionarse es el de Configure Device. Se

abrirá una ventana con varias opciones de cómo configurar el dispositivo. Para el Spartan II, se

selecciona el Boundary-Scan Mode y en la siguiente ventana se selecciona Enter a BoundaryScan Chain. Esto permite que se seleccione el archivo .bit de la carpeta del proyecto. Se debe

recordar que en este punto, el Spartan II debe estar conectado a la computadora y alimentado con

una fuente de 5V.

Dentro de esta ventana, se marca el chip que aparece, y en la opción de Operations se marca

Program (ver Figura Anexo 1.7).

Noviembre 2004

IE-0502

Filtro Digital Impl ementado en un PLD

44

Figura Anexo 1.7. Proceso de programación del FPGA.

Ahora el circuito está listo para ser probado. Introduciendo un “nivel alto” en el pin #2 del puerto

paralelo, comenzará a parpadear el LED1 de la tabla DIGILAB IIE del SpartanII.

Noviembre 2004

IE-0502

Filtro Digital Impl ementado en un PLD

Anexo 2:

45

Código Fuente de los Módulos

////////////////**** MODULO DE RELOJ PARA REDUCIR LA FRECUENCIA DEL ***//////////////

//

RELOJ PRINCIPAL

//

module reloj(reloj, clk);

input reloj;

output clk;

reg cont;

assign clk=cont;

always @(posedge reloj)

cont=cont+1;

endmodule

//////////************ FILTRO PARA COEF ICIENTES DE 6 BITS *****************////////

///********************

Y 15 TAPS

**********************////////

`define dac_width 20

`define adc_width 20

`define left 0

`define right 1

`define tap 15

module filtro(reloj, lrck, ladc_out, radc_out, ldac_in, rdac_in,

ladc_out_rdy, radc_out_rdy, tx_left, tx_right);

input reloj,

lrck,

ladc_out_rdy,

radc_out_rdy;

input [`adc_width-1:0]ladc_out,

radc_out;

output [`dac_width-1:0]ldac_in,

rdac_in;

output tx_left,

tx_right;

reg

reg

reg

reg

reg

reg

reg

reg

[`adc_width-1:0]fifo_lchannel[0:`tap-1];

[`adc_width-1:0]fifo_lchannel_aux[0:`tap-1];

[`adc_width-1:0]fifo_rchannel[0:`tap-1];

[`adc_width-1:0]fifo_rchannel_aux[0:`tap-1];

[5:0]firCoef[0:`tap-1];

[`dac_width-1:0]ldac_in,

rdac_in;

[26:0]left_dataTem,

right_dataTem;

ready_left,

ready_right,

ready_left_aux,

Noviembre 2004

IE-0502

Filtro Digital Impl ementado en un PLD

46

ready_right_aux,

rdataTem,

ldataTem,

tx_right,

tx_left;

always @(posedge reloj)

begin

/*

///COEFICIENTES DE FILTRO PASO BAJO

//Fstop = 7500 Hz

firCoef[0] <= 6'b000000;//0

firCoef[1] <= 6'b001001;//9

firCoef[2] <= 6'b001100;//12

firCoef[3] <= 6'b010001;//17

firCoef[4] <= 6'b010110;//22

firCoef[5] <= 6'b011011;//27

firCoef[6] <= 6'b011110;//30

firCoef[7] <= 6'b011111;//31

firCoef[8] <= 6'b011110;//30

firCoef[9] <= 6'b011011;//27

firCoef[10] <= 6'b010110;//22

firCoef[11] <= 6'b010001;//17

firCoef[12] <= 6'b001100;//12

firCoef[13] <= 6'b001001;//9

firCoef[14] <= 6'b000000;//0

*/

/*

///COEFICIENTES DE FILTRO PASO ALTO

//Fstop = 1100Hz Fpass = 7500Hz (TEORICO)

firCoef[0] <= 6'b000000;//0

firCoef[1] <= 6'b000000;//0

firCoef[2] <= 6'b000000;//0

firCoef[3] <= 6'b111110;//-2

firCoef[4] <= 6'b111101;//-3

firCoef[5] <= 6'b111011;//-5

firCoef[6] <= 6'b111010;//-6

firCoef[7] <= 6'b011111;//31

firCoef[8] <= 6'b111010;//-6

firCoef[9] <= 6'b111011;//-5

firCoef[10] <= 6'b111101;//-3

firCoef[11] <= 6'b111110;//-2

firCoef[12] <= 6'b000000;//0

firCoef[13] <= 6'b000000;//0

firCoef[14] <= 6'b000000;//0

*/

//*

///COEFICIENTES DE FILTRO PASA BANDA

//Fpass = 300Hz-4800Hz

firCoef[0] <= 6'b111110;//-2

firCoef[1] <= 6'b111111;//-1

Noviembre 2004

IE-0502

Filtro Digital Impl ementado en un PLD

47

firCoef[2] <= 6'b111110;//-2

firCoef[3] <= 6'b110111;//-9

firCoef[4] <= 6'b110001;//-15

firCoef[5] <= 6'b111010;//-6

firCoef[6] <= 6'b010010;//18

firCoef[7] <= 6'b011111;//31

firCoef[8] <= 6'b010010;//18

firCoef[9] <= 6'b111010;//-6

firCoef[10] <= 6'b110001;//-15

firCoef[11] <= 6'b110111;//-9

firCoef[12] <= 6'b111110;//-2

firCoef[13] <= 6'b111111;//-1

firCoef[14] <= 6'b111110;//-2

//*/

end

//DESPLAZAMIENTO DE LOS REGISTROS PRINCIPALES A LOS AUXILIARES

always @(posedge reloj)

begin

// CANAL LCHANNEL

if(lrck == `left & ladc_out_rdy & ~ready_left_aux)

begin

fifo_lchannel_aux[14]<=fifo_lchannel[13];

fifo_lchannel_aux[13]<=fifo_lchannel[12];

fifo_lchannel_aux[12]<=fifo_lchannel[11];

fifo_lchannel_aux[11]<=fifo_lchannel[10];

fifo_lchannel_aux[10]<=fifo_lchannel[9];

fifo_lchannel_aux[9]<=fifo_lchannel[8];

fifo_lchannel_aux[8]<=fifo_lchannel[7];

fifo_lchannel_aux[7]<=fifo_lchannel[6];

fifo_lchannel_aux[6]<=fifo_lchannel[5];

fifo_lchannel_aux[5]<=fifo_lchannel[4];

fifo_lchannel_aux[4]<=fifo_lchannel[3];

fifo_lchannel_aux[3]<=fifo_lchannel[2];

fifo_lchannel_aux[2]<=fifo_lchannel[1];

fifo_lchannel_aux[1]<=fifo_lchannel[0];

fifo_lchannel_aux[0]<=ladc_out;

ready_left_aux<=1;

end

else if(~ladc_out_rdy)

ready_left_aux<=0;

end

// CANAL RCHANNEL

always @(posedge reloj)

begin

if(lrck == `right & radc_out_rdy & ~ready_right_aux)

begin

fifo_rchannel_aux[14]<=fifo_rchannel[13];

fifo_rchannel_aux[13]<=fifo_rchannel[12];

fifo_rchannel_aux[12]<=fifo_rchannel[11];

Noviembre 2004

IE-0502

Filtro Digital Impl ementado en un PLD

48

fifo_rchannel_aux[11]<=fifo_rchannel[10];

fifo_rchannel_aux[10]<=fifo_rchannel[9];

fifo_rchannel_aux[9]<=fifo_rchannel[8];

fifo_rchannel_aux[8]<=fifo_rchannel[7];

fifo_rchannel_aux[7]<=fifo_rchannel[6];

fifo_rchannel_aux[6]<=fifo_rchannel[5];

fifo_rchannel_aux[5]<=fifo_rchannel[4];

fifo_rchannel_aux[4]<=fifo_rchannel[3];

fifo_rchannel_aux[3]<=fifo_rchannel[2];

fifo_rchannel_aux[2]<=fifo_rchannel[1];

fifo_rchannel_aux[1]<=fifo_rchannel[0];

fifo_rchannel_aux[0]<=radc_out;

ready_right_aux<=1;

end

else if(~radc_out_rdy)

ready_right_aux<=0;

end

//DESPLAZAMIENTO DE LOS REGISTROS AUXILIARES A LOS PRINCIPALES

always @(posedge reloj)

begin

if(ready_left_aux & ~ready_left)

begin

//CANAL LCHANNEL

fifo_lchannel[14]<=fifo_lchannel_aux[14];

fifo_lchannel[13]<=fifo_lchannel_aux[13];

fifo_lchannel[12]<=fifo_lchannel_aux[12];

fifo_lchannel[11]<=fifo_lchannel_aux[11];

fifo_lchannel[10]<=fifo_lchannel_aux[10];

fifo_lchannel[9]<=fifo_lchannel_aux[9];

fifo_lchannel[8]<=fifo_lchannel_aux[8];

fifo_lchannel[7]<=fifo_lchannel_aux[7];

fifo_lchannel[6]<=fifo_lchannel_aux[6];

fifo_lchannel[5]<=fifo_lchannel_aux[5];

fifo_lchannel[4]<=fifo_lchannel_aux[4];

fifo_lchannel[3]<=fifo_lchannel_aux[3];

fifo_lchannel[2]<=fifo_lchannel_aux[2];

fifo_lchannel[1]<=fifo_lchannel_aux[1];

fifo_lchannel[0]<=fifo_lchannel_aux[0];

ready_left<=1;

end

else if(~ready_left_aux)

ready_left<=0;

end

always @(posedge reloj)

begin

if(ready_right_aux & ~ready_right)

begin

//CANAL RCHANNEL

fifo_rchannel[14]<=fifo_rchannel_aux[14];

Noviembre 2004

IE-0502

Filtro Digital Impl ementado en un PLD

49

fifo_rchannel[13]<=fifo_rchannel_aux[13];

fifo_rchannel[12]<=fifo_rchannel_aux[12];

fifo_rchannel[11]<=fifo_rchannel_aux[11];

fifo_rchannel[10]<=fifo_rchannel_aux[10];

fifo_rchannel[9]<=fifo_rchannel_aux[9];

fifo_rchannel[8]<=fifo_rchannel_aux[8];

fifo_rchannel[7]<=fifo_rchannel_aux[7];

fifo_rchannel[6]<=fifo_rchannel_aux[6];

fifo_rchannel[5]<=fifo_rchannel_aux[5];

fifo_rchannel[4]<=fifo_rchannel_aux[4];

fifo_rchannel[3]<=fifo_rchannel_aux[3];

fifo_rchannel[2]<=fifo_rchannel_aux[2];

fifo_rchannel[1]<=fifo_rchannel_aux[1];

fifo_rchannel[0]<=fifo_rchannel_aux[0];

ready_right<=1;

end

else if(~ready_right_aux)

ready_right<=0;

end

//MULTIPLICACION Y SUMA, PROCESO DE FILTRADO DIGITAL

always @(posedge reloj)

begin

if(ready_right & ~rdataTem)

begin

//CANAL RCHANNEL

right_dataTem<=(fifo_rchannel[0]*firCoef[0]+

fifo_rchannel[1]*firCoef[1]+

fifo_rchannel[2]*firCoef[2]+

fifo_rchannel[3]*firCoef[3]+

fifo_rchannel[4]*firCoef[4]+

fifo_rchannel[5]*firCoef[5]+

fifo_rchannel[6]*firCoef[6]+

fifo_rchannel[7]*firCoef[7]+

fifo_rchannel[8]*firCoef[8]+

fifo_rchannel[9]*firCoef[9]+

fifo_rchannel[10]*firCoef[10]+

fifo_rchannel[11]*firCoef[11]+

fifo_rchannel[12]*firCoef[12]+

fifo_rchannel[13]*firCoef[13]+

fifo_rchannel[14]*firCoef[14]);

rdataTem<=1;

end

else if(~ready_right)

begin

rdataTem<=0;

right_dataTem<=0;

end

end

always @(posedge reloj)

Noviembre 2004

IE-0502

Filtro Digital Impl ementado en un PLD

50

//CANAL LCHANNEL

begin

if(ready_left & ~ldataTem)

begin

left_dataTem<=(fifo_lchannel[0]*firCoef[0]+

fifo_lchannel[1]*firCoef[1]+

fifo_lchannel[2]*firCoef[2]+

fifo_lchannel[3]*firCoef[3]+

fifo_lchannel[4]*firCoef[4]+

fifo_lchannel[5]*firCoef[5]+

fifo_lchannel[6]*firCoef[6]+

fifo_lchannel[7]*firCoef[7]+

fifo_lchannel[8]*firCoef[8]+

fifo_lchannel[9]*firCoef[9]+

fifo_lchannel[10]*firCoef[10]+

fifo_lchannel[11]*firCoef[11]+

fifo_lchannel[12]*firCoef[12]+

fifo_lchannel[13]*firCoef[13]+

fifo_lchannel[14]*firCoef[14]);

ldataTem<=1;

end

else if(~ready_left)

begin

ldataTem<=0;

left_dataTem<=0;

end

end

always @(posedge reloj) //TRANSFERENCIA DE RESULTADO A LA SALIDA

begin

if(rdataTem & ~tx_right)

begin

rdac_in <= right_dataTem[19:0];

tx_right<=1;

end

else if(~rdataTem)

tx_right<=0;

if(ldataTem & ~tx_left)

begin

ldac_in <= left_dataTem[19:0];

tx_left<=1;

end

else if(~ldataTem)

tx_left<=0;

end

endmodule

////////////**************** MODULO CLOCKGENERATOR *******************///////////

//*** SE ENCARGA DE SINCRONIZAR LA TRANSFERENCIA DE DATOS ENTRE LOS MODULOS ***//

`define yes 1

Noviembre 2004

IE-0502

Filtro Digital Impl ementado en un PLD

51

`define no 0

`define left 0

`define right 1

`define channel_duration 128

module clockGenerator(clk, reset, mclk, sclk, lrck, bit_cntr, subcycle_cntr);

input clk, //Entrada de Reloj

reset; //Reset sincronico activo en alto

output mclk, //Salida Master Clock al codec

sclk, //Reloj del serial data al codec

lrck; //Selector de canal left/right

output [5:0]bit_cntr; //Estas salidas indican el bit que esta siendo transmitido y recibido

output [1:0]subcycle_cntr; //La duracion de cada bit del dato serial es dividido en 4 fases

reg

lrck_int;

wire lrck,

sclk,

mclk;

reg [7:0]seq;

wire [5:0]bit_cntr;

wire [1:0]subcycle_cntr;

assign lrck = lrck_int;

assign mclk = clk;

assign sclk = seq[1]; //El serial shift clock es 1/4 del Master Clock

assign bit_cntr = seq[7:2];

assign subcycle_cntr = seq[1:0];

always @(posedge clk)

begin

if(reset == `yes)

begin

seq <= 0;

lrck_int <= `left;

end

else if(seq == `channel_duration-1)

begin

seq <= 0; //Se resetea la secuencia cada periodo de canal

lrck_int <= !lrck_int; //Cambia la seleccion del canal cada periodo

end

else

begin

seq <= seq+1; //Se incrementa el secuenciador normalmente

lrck_int <= lrck_int; //No se cambia el selector de canal

end

end

endmodule

//////////************ MODULO CHANNEL ************///////////

////////******* MANEJA LOS REGISTROS DE DESPLAZAMIENTO ********////

///**** PARA CAPTURAR LOS DATOS SERIALES Y PASARLOS A PARALELO****///////

`define dac_width 20

Noviembre 2004

IE-0502

Filtro Digital Impl ementado en un PLD

52

`define adc_width 20

`define yes 1

`define no 0

`define left 0

`define right 1

`define channel_duration 128

module channel(clk, reset, chan_on, bit_cntr, subcycle_cntr, chan_sel, rd, wr,

adc_out, dac_in, adc_out_rdy, adc_overrun, dac_in_rdy, dac_underrun,

sdin, sdout);

input clk, //Entrada de reloj Master

reset; //Reset activo en alto para sincronizacion

input chan_on; //Selector de canal left/right

input [5:0]bit_cntr;

input [1:0]subcycle_cntr;

input chan_sel; //Selecciona left/rigth codec channel para rd/wr

input rd, //Leer desde el codec ADC

wr; //Escribir al codec DAC

output [`adc_width-1:0]adc_out; //Desde el codec ADC

input [`dac_width-1:0]dac_in; //Hacia codec DAC

output adc_out_rdy; //Salida ADC lista para ser leida

output adc_overrun; //Salida del canal ADC overwritten

output dac_in_rdy; //Entrada DAC lista para ser escrita

output dac_underrun; //Entrada DAC no lista a tiempo

output sdin; //Salida serial al codec DAC

input sdout; //Entrada serial desde el codec ADC

wire [`adc_width-1:0]adc_out;

wire adc_out_rdy;

reg adc_overrun;

wire dac_in_rdy;

reg dac_underrun,

sdin;

reg [`dac_width-1:0]dac_shfreg; //Registro de desplazamiento DAC

reg dac_empty; //Registro DAC esta vacio

reg dac_wr; //Canal DAC ha sido escrito

reg dac_wr_nxt; //Canal DAC ha sido escrito

reg dac_in_rdy_int; //DAC esta listo para una entrada

reg [`adc_width-1:0]adc_shfreg;

reg adc_full; //Registro ADC esta lleno

reg adc_rd; //Canal ADC ha sido leido

reg adc_rd_nxt; //Canal ADC ha sido leido

reg adc_out_rdy_int; //ADC listo para salida

//Recibe dato del codec ADC

assign adc_out = adc_shfreg;

always @(posedge clk)

begin

if(reset == `yes)

begin

Noviembre 2004

IE-0502

Filtro Digital Impl ementado en un PLD

53

adc_shfreg <= 0;

adc_full <= `no;

end

else if((chan_on==`yes) & (subcycle_cntr==1))

begin

if((bit_cntr>=1) & (bit_cntr<`adc_width))

begin

adc_full <= `no;

adc_shfreg <= {adc_shfreg[`adc_width-2:0],sdout};

end

else if(bit_cntr==`adc_width)

begin

adc_full <= `yes;

adc_shfreg <= {adc_shfreg[`adc_width-2:0],sdout};

end

end

if((adc_full == `yes & chan_sel == `yes & rd == `yes) || (adc_full == `yes & adc_rd == `yes))

adc_rd_nxt <= `yes;

else

adc_rd_nxt <= `no;

end

//Lectura del ADC

assign adc_out_rdy = adc_out_rdy_int;

always @(posedge clk)

begin

if(reset == `yes)

adc_rd <= `no;

else

adc_rd <= adc_rd_nxt;

if(adc_full == `yes & adc_rd == `no)

adc_out_rdy_int <= `yes;

else

adc_out_rdy_int <= `no;

end

//Detecta señal sobre escrita en dato del canal ADC

always @(posedge clk)

begin

if(reset == `yes)

adc_overrun <= `no;

else if(bit_cntr == 1 & chan_on == `yes & adc_out_rdy_int == `yes)

adc_overrun <= `yes;

end

//Transmision de dato al codec DAC

always @(posedge clk)

begin

Noviembre 2004

IE-0502

54

Filtro Digital Impl ementado en un PLD

if(reset == `yes)

begin

dac_shfreg <= 0;

dac_empty <= `yes;

end

else if(chan_sel == `yes & wr == `yes)

dac_shfreg <= dac_in;

else if(chan_on == `yes & subcycle_cntr == 1)

begin

if(bit_cntr == 0)

dac_empty <= `no;

else if(bit_cntr < `dac_width)

dac_shfreg <= {dac_shfreg[`dac_width-2:0],1'b0};

else if(bit_cntr == `dac_width)

begin

dac_empty <= `yes;

dac_shfreg <= {dac_shfreg[`dac_width-2:0],1'b0};

end

end

if(chan_on == `yes)

sdin <= dac_shfreg[`dac_width-1];

else

sdin <= 0;

if((dac_empty == `yes & chan_sel == `yes & wr == `yes) || (dac_empty == `yes & dac_wr == `yes))

dac_wr_nxt <= `yes;

else

dac_wr_nxt <= `no;

end

//Lectura DAC

always @(posedge clk)

begin

if(reset == `yes)

dac_wr <= `no;

else

dac_wr <= dac_wr_nxt;

if(dac_empty == `yes & dac_wr == `no)

dac_in_rdy_int <= `yes;

else

dac_in_rdy_int <= `no;

end

assign dac_in_rdy = dac_in_rdy_int;

//Detectar señal underflow

always @(posedge clk)

begin

if(reset == `yes)

dac_underrun <= `no;

Noviembre 2004

IE-0502

Filtro Digital Impl ementado en un PLD

55

else if(bit_cntr == 1 & chan_on == `yes & dac_in_rdy_int == `yes)

dac_underrun <= `yes;

end

endmodule

///////////********* MODULO CODEC TOP **********/////////

///**** CONTIENE LOS MODULOS CHANNEL Y CLOCKGENERATOR ****/////

`define dac_width 20

`define adc_width 20

`define channel_duration 128

`define yes 1

`define no 0

`define left 0

`define right 1

module codecTop(clk, reset, lrsel, rd, wr, ladc_out, radc_out, ldac_in, rdac_in,

ladc_out_rdy, radc_out_rdy, adc_overrun, ldac_in_rdy, rdac_in_rdy,

dac_underrun, mclk, sclk, lrck, sdin, sdout);

input clk,

reset,

lrsel, //Selecciona el canal left/rigth para rd/wr

rd, //lectura del codec ADC

wr; //escribe al codec DAC

output [`adc_width-1:0]ladc_out, // ADC left

radc_out; // ADC rigth

input [`dac_width-1:0]ldac_in, // DAC left

rdac_in; // DAC rigth

output ladc_out_rdy, // ADC left listo para ser leido

radc_out_rdy, // ADC rigth listo para ser leido

adc_overrun, // Datos del ADC reescritos antes de leerse

ldac_in_rdy, // Entrada DAC left lista para ser escrita

rdac_in_rdy, // Entrada DAC rigth lista para ser escrita

dac_underrun, // DAC no escrita a tiempo

mclk, // Reloj Master, salida al codec

sclk, // Reloj de los datos seriales al codec

lrck, // selector de canal del codec left/rigth

sdin; // salida serial al codec DAC

input sdout; // entrada serial desde el codec

wire [`adc_width-1:0]ladc_out, // ADC left

radc_out; // ADC rigth

wire ladc_out_rdy, // ADC left listo para ser leido

radc_out_rdy; // ADC rigth listo para ser leido

reg adc_overrun; // Datos del ADC reescritos antes de leerse

wire ldac_in_rdy, // Entrada DAC left lista para ser escrita

rdac_in_rdy; // Entrada DAC rigth lista para ser escrita

wire ldac_underrun,

rdac_underrun;

reg dac_underrun; // DAC no escrita a tiempo

wire mclk, // Reloj Master, salida al codec

sclk, // Reloj de los datos seriales al codec

lrck; // selector de canal del codec left/right

reg sdin; // salida serial al codec DAC

Noviembre 2004

IE-0502

Filtro Digital Impl ementado en un PLD

56

// Registros de senales

wire lrck_int; //selector interno de canal del codec left/right

wire [5:0]bit_cntr;

wire [1:0]subcycle_cntr;

wire lsdin,

rsdin;

wire ladc_overrun,

radc_overrun;

reg lchan_sel,

rchan_sel,

lchan_on,

rchan_on;

//arquitectura del codec

assign lrck = lrck_int;

clockGenerator u0(clk, reset, mclk, sclk, lrck_int, bit_cntr, subcycle_cntr);

// LEFT CHANNEL

always @(posedge clk)

begin

if(lrsel == `left)

lchan_sel <= `yes;

else

lchan_sel <= `no;

if(lrck_int == `left)

lchan_on <= `yes;

else

lchan_on <= `no;

end

channel u_left(clk, reset, lchan_on, bit_cntr, subcycle_cntr, lchan_sel, rd, wr,

ladc_out, ldac_in, ladc_out_rdy, ladc_overrun, ldac_in_rdy,

ldac_underrun, lsdin, sdout);

// RIGHT CHANNEL

always @(posedge clk)

begin

if(lrsel == `right)

rchan_sel <= `yes;

else

rchan_sel <= `no;

if(lrck_int == `right)

rchan_on <= `yes;

else

rchan_on <= `no;

end

channel u_rigth(clk, reset, rchan_on, bit_cntr, subcycle_cntr, rchan_sel, rd, wr,

radc_out, rdac_in, radc_out_rdy, radc_overrun, rdac_in_rdy,

rdac_underrun, rsdin, sdout);

Noviembre 2004

IE-0502

Filtro Digital Impl ementado en un PLD

57

// REBASE

always @(posedge clk)

begin

if(ldac_underrun == `yes || rdac_underrun == `yes)

dac_underrun <= `yes;

else

dac_underrun <= `no;

if(ladc_overrun == `yes || radc_overrun == `yes)

adc_overrun <= `yes;

else

adc_overrun <= `no;

if(lrck_int == `left)

sdin <= lsdin;

else

sdin <= rsdin;

end

endmodule

///////////////********* MODULO TOP LEVEL **********///////////////

////***** CONTIENE TODOS LOS DEMAS MODULOS Y LOS CONECTA ENTRE SI *****////

//*** ADEMAS MANEJA UNA UNIDAD DE CONTROL PARA LA TX Y RX ENTRE CODEC Y CHANNEL

***//

`define dac_width 20

`define adc_width 20

`define channel_duration 128

`define yes 1

`define no 0

`define left 0

`define right 1

module top_level(reloj_in, reloj_out, rst, mclk, lrck, sclk, sdout, sdin, s);

input reloj_in,

rst,

sdout;

output mclk,

lrck,

sclk;

reloj_out;

output sdin;

output [1:0]s;

reg

lrsel,

rd,

wr;

wire [`dac_width-1:0]left_channel_out,

right_channel_out;

wire [`adc_width-1:0]left_channel_in,

right_channel_in;

wire ldac_in_rdy,

rdac_in_rdy;

Noviembre 2004

IE-0502

Filtro Digital Impl ementado en un PLD

58

wire ladc_out_rdy,

radc_out_rdy;

wire clk;

wire tx_left,

tx_right;

assign reloj_out=reloj_in;

reloj uno(reloj_in, clk);

codecTop codec(clk, rst, lrsel, rd, wr, left_channel_out, right_channel_out,

left_channel_in, right_channel_in, ladc_out_rdy, radc_out_rdy, s[1],

ldac_in_rdy, rdac_in_rdy, s[0], mclk, sclk, lrck, sdin, sdout);

filtro digital(reloj_in, lrck, left_channel_out, right_channel_out,

left_channel_in, right_channel_in, ladc_out_rdy, radc_out_rdy,

tx_left, tx_right);

always @(posedge clk)

begin

if(ladc_out_rdy == `yes & ldac_in_rdy == `yes & tx_left)

begin

lrsel <= `left;

rd <= `yes;

wr <= `yes;

end

else if(radc_out_rdy == `yes & rdac_in_rdy == `yes & tx_right)

begin

lrsel <= `right;

rd <= `yes;

wr <= `yes;

end

else

begin

lrsel <= `left;

rd <= `no;

wr <= `no;

end

end

endmodule

Noviembre 2004