La evolución de la computadora. Ing. Obadiah

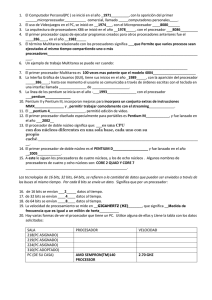

Anuncio