Estudio de un radio enlace entre los dispensaríos de pulinguí y

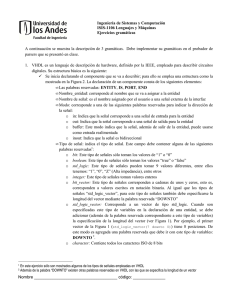

Anuncio