Descarga

Anuncio

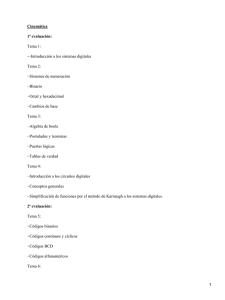

Capítulo 3: Análisis y Diseño de Circuitos Combinacionales ANALISIS Y DISEÑO DE CIRCUITOS COMBINACIONALES • Codificadores • Decodificadores • Multiplexores • Comparadores • Generadores/Detectores de paridad Capitulo 3:Análisis y diseño de circuitos combinacionales 1 Códigos BCD Sistema Decimal BCD Natural BCD Exceso tres BCD Aiken 0 1 2 3 4 5 6 7 8 9 0000 0001 0010 0011 0100 0101 0110 0111 1000 1001 0011 0100 0101 0110 0111 1000 1001 1010 1011 1100 0000 0001 0010 0011 0100 1011 1100 1101 1110 1111 Capitulo 3:Análisis y diseño de circuitos combinacionales Lógica Digital y Microprogramable. Autor: Fernando Remiro Domínguez 2 1 Capítulo 3: Análisis y Diseño de Circuitos Combinacionales Códigos Binarios Decimal Hexadecimal Binario Natural Gray 0 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 0 1 2 3 4 5 6 7 8 9 A B C D E F 0000 0001 0010 0011 0100 0101 0110 0111 1000 1001 1010 1011 1100 1101 1110 1111 0000 0001 0011 0010 0110 0111 0101 0100 1100 1101 1111 1110 1010 1011 1001 1000 Capitulo 3:Análisis y diseño de circuitos combinacionales 3 Código Hamming b7 b6 b5 b4 b3 b2 b1 0 1 2 3 4 5 6 7 8 9 0 0 0 0 0 0 0 0 1 1 0 0 0 0 1 1 1 1 0 0 0 0 1 1 0 0 1 1 0 0 0 0 1 1 1 1 0 0 1 1 0 1 0 1 0 1 0 1 0 1 0 1 0 1 1 0 1 0 1 0 0 1 1 0 0 1 1 0 1 0 Obtención de los bits redundantes b1 = b3 ⊕ b5 ⊕ b7 b2 = b3 ⊕ b6 ⊕ b7 b4 = b5 ⊕ b6 ⊕ b7 Detector de errores C1 = b1 ⊕ b3 ⊕ b5 ⊕ b7 C2 = b1 ⊕ b3 ⊕ b6 ⊕ b7 C3 = b4 ⊕ b5 ⊕ b6 ⊕ b7 Capitulo 3:Análisis y diseño de circuitos combinacionales Lógica Digital y Microprogramable. Autor: Fernando Remiro Domínguez 4 2 Capítulo 3: Análisis y Diseño de Circuitos Combinacionales Codificador de Prioridad 74148 Capitulo 3:Análisis y diseño de circuitos combinacionales 5 Tabla de funcionamiento del Codificador 74148 Capitulo 3:Análisis y diseño de circuitos combinacionales Lógica Digital y Microprogramable. Autor: Fernando Remiro Domínguez 6 3 Capítulo 3: Análisis y Diseño de Circuitos Combinacionales Ampliación de la capacidad de un codificador de prioridad a 16 bits MSB LSB EI 7 6 5 4 3 2 1 0 EI 7 6 74148 EO A3 A2 A2 A1 A1 5 4 3 2 1 0 74148 A0 GS EO A2 A1 A0 GS A0 LSB = bit menos significativo MSB = bit más significativo Capitulo 3:Análisis y diseño de circuitos combinacionales 7 Decodificador BCD-7 Segmentos Ánodo Común Capitulo 3:Análisis y diseño de circuitos combinacionales Lógica Digital y Microprogramable. Autor: Fernando Remiro Domínguez 8 4 Capítulo 3: Análisis y Diseño de Circuitos Combinacionales Tabla de funcionamiento del decodificador 7447 Capitulo 3:Análisis y diseño de circuitos combinacionales 9 Display Cátodo Común Capitulo 3:Análisis y diseño de circuitos combinacionales Lógica Digital y Microprogramable. Autor: Fernando Remiro Domínguez 10 5 Capítulo 3: Análisis y Diseño de Circuitos Combinacionales Display Ánodo Común Capitulo 3:Análisis y diseño de circuitos combinacionales 11 Conexión del decodificador al display de ánodo común y un cátodo común Vcc g e 15 f 14 g f Vcc a a g b f g b f g b e d c e d c e d Vcc c 13 a 12 b 11 c 10 d 15 9 14 C 1 2 4 d Gnd c 13 12 b 11 c 10 9 f g a d e A B C BI/ LT RBO RBI D A 7448 BI/ LT RBO RBI D 3 b e 7447 B f Gnd a a 5 6 1 7 Display Ánodo Común 2 3 4 5 6 7 Display Cátodo Común Capitulo 3:Análisis y diseño de circuitos combinacionales Lógica Digital y Microprogramable. Autor: Fernando Remiro Domínguez 12 6 Capítulo 3: Análisis y Diseño de Circuitos Combinacionales VISUALIDADOR DE TRES DIGITOS Capitulo 3:Análisis y diseño de circuitos combinacionales 13 El Multiplexor 74151 74151 7 11 10 9 4 3 2 1 15 14 13 12 S A B C D0 D1 D2 D3 D4 D5 D6 D7 74151 5 Y 6 W ANSI-IEEE 91-1973 A B C D0 D1 D2 D3 D4 D5 D6 D7 7 11 10 9 4 3 2 1 15 14 13 12 EN 0 G 2 0 1 2 3 4 5 6 7 0 7 5 6 Y W ANSI-IEEE 91-1984 Capitulo 3:Análisis y diseño de circuitos combinacionales Lógica Digital y Microprogramable. Autor: Fernando Remiro Domínguez MUX 14 7 Capítulo 3: Análisis y Diseño de Circuitos Combinacionales Tabla de funcionamiento del multiplexor 74151 G A B C D0 D1 D2 D3 D4 D5 D6 D7 7 11 MUX EN 0 10 9 4 3 2 1 15 14 13 12 0 G7 2 0 5 1 6 2 Y W 3 4 5 6 7 ANSI-IEEE 911984 Y = A B C D0 + A B C D1 + A B C D2 + A B C D3 + A B C D4 + A B C D5 + A B C D6 + A B C D7 Capitulo 3:Análisis y diseño de circuitos combinacionales +Vcc 15 Implementación de una función de 3 variables con un multiplexor de 3 entradas de direccionamiento D0 C BA Y 0 0 0 0 1 1 1 1 1 1 1 0 0 0 1 1 D1 D2 D3 Y D4 D5 D6 D7 S 0 0 1 1 0 0 1 1 0 1 0 1 0 1 0 1 C B A c b a Y =A B C D0 + A B C D1 + A B C D2 + A B C D6 + A B C D7 Capitulo 3:Análisis y diseño de circuitos combinacionales Lógica Digital y Microprogramable. Autor: Fernando Remiro Domínguez 16 8 Capítulo 3: Análisis y Diseño de Circuitos Combinacionales Función de 4 variables implementada con un multiplexor de 3 entradas de direccionamiento +Vcc 4 3 2 1 15 14 13 12 d D0 D1 D2 D3 5 Y D4 D5 D6 D7 S 7 C B A 9 10 11 c b a dcba Y 0000 0001 0010 0011 0100 0101 0110 0111 1000 1001 1010 1011 1100 1101 1110 1111 0 0 1 0 1 0 1 1 1 0 0 0 1 1 0 1 Capitulo 3:Análisis y diseño de circuitos combinacionales 17 Dual multiplexor 74153 A B 1G 1C0 1C1 1C2 1C3 2G 2C0 2C1 2C2 2C3 14 2 1 6 5 4 3 1 EN G 0 3 MUX 0 1 7 1Y 2 3 15 10 11 9 2Y 12 13 Capitulo 3:Análisis y diseño de circuitos combinacionales Lógica Digital y Microprogramable. Autor: Fernando Remiro Domínguez 0 18 9 Capítulo 3: Análisis y Diseño de Circuitos Combinacionales Tabla de funcionamiento del multiplexor 74153 A B 1G 1C0 1C1 1C2 1C3 2G 2C0 2C1 2C2 2C3 14 0 2 G 0 3 1 1 EN 6 MUX 0 5 7 1Y 1 4 2 3 3 15 10 9 11 2Y 12 13 Capitulo 3:Análisis y diseño de circuitos combinacionales 19 Multiplexor 74150 INPUTS MUX G EN A 0 0 G 15 B C D 3 D0 0 D1 1 D2 2 D3 3 D4 4 D5 5 D6 6 D7 D8 8 D9 9 D10 10 D11 11 D12 12 D13 13 D14 14 D15 W 7 15 ANSI-IEEE 91-1984 STROBE G W LL L L L L L H L L H L L L H H L H L L L H L H L H H L L H H H H L L L H L L H H L H L H L H H H H L L H H L H H H H L H H H H H L L L L L L L L L L L L L L L H /E0 /E1 /E2 /E3 /E4 /E5 /E6 /E7 /E8 /E9 /E10 /E11 /E12 /E13 /E14 Capitulo 3:Análisis y diseño de circuitos combinacionales Lógica Digital y Microprogramable. Autor: Fernando Remiro Domínguez OUTPUT SELECT DCBA 20 10 Capítulo 3: Análisis y Diseño de Circuitos Combinacionales Cuádruple Multiplexor 74157 G A/B 1A 1B 2A 2B 3A 3B 4A 15 EN 1 G1 2 1 3 4 MUX 1Y 1 5 7 6 11 9 10 14 12 13 2Y 3Y 4Y Capitulo 3:Análisis y diseño de circuitos combinacionales 21 Decodificador de 4 a 10 líneas 7442 7442 0 1 15 14 13 12 A 2 3 B C D 4 5 6 7 8 9 1 BCD/DEC 0 2 1 3 4 5 6 A B C 7 9 D 15 14 13 12 10 11 Capitulo 3:Análisis y diseño de circuitos combinacionales Lógica Digital y Microprogramable. Autor: Fernando Remiro Domínguez 1 2 3 2 4 8 4 5 6 7 8 9 1 0 2 1 3 2 4 3 5 4 6 5 7 6 9 7 10 8 11 9 22 11 Capítulo 3: Análisis y Diseño de Circuitos Combinacionales Tabla de funcionamiento del decodificador de 4 a 10 líneas 7442 BCD/DEC 1 0 2 1 A B C D 3 2 15 1 14 2 13 5 4 4 12 4 3 6 5 8 7 6 9 7 10 8 11 9 0 1 2 3 4 5 6 7 8 9 ANSI-IEEE 91-1984 Capitulo 3:Análisis y diseño de circuitos combinacionales 23 Implementación de una función con un decodificador CBA Y a b c 15 A 14 B 13 C 12 D 7442 0 1 2 3 4 5 6 7 8 9 1 2 3 4 5 6 7 1 2 6 4 5 F 1/7420 9 10 11 000 001 010 011 100 101 110 111 0 1 0 1 1 0 0 1 Y =C B A+ C B A +C B A+C B A Capitulo 3:Análisis y diseño de circuitos combinacionales Lógica Digital y Microprogramable. Autor: Fernando Remiro Domínguez 24 12 Capítulo 3: Análisis y Diseño de Circuitos Combinacionales Decodificador de 4 a 16 líneas EL 74154 74154 1 BIN/DEC 0 2 1 A0 A1 23 22 A2 21 A3 20 3 2 1 4 3 2 5 4 4 5 8 6 6 7 8 7 9 8 10 9 10 11 12 13 G1 & G2 11 13 14 15 14 16 15 17 ANSI-IEEE 91-1984 __ __ 1G 2G Ent. binarias A3 A2 A1 A0 Salidas 0 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 H H L L L L L L L L L L L L L L L L L X X X L L L L L L L L H H H H H H H H H H H L H H H H H H H H H H H H H H H H L H L L L L L L L L L L L L L L L L X X X L L L L H H H H L L L L H H H H X X X X X X L L L H H L H H L L L H H L H H L L L H H L H H L L L H H L H H H H H H L H H H H H H H H H H H H H H H H H H H L H H H H H H H H H H H H H H H H H H H L H H H H H H H H H H H H H H H H H H H L H H H H H H H H H H H H H H H H H H H L H H H H H H H H H H H H H H H H H H H L H H H H H H H H H H H H H H H H H H H L H H H H H H H H H H H H H H H H H H H L H H H H H H H H H H H H H H H H H H H L H H H H H H H H H H H H H H H H H H H L H H H H H H H H H H H H H H H H H H H L H H H H H H H H H H H H H H H H H H H L H H H H H H H H H H H H H H H H H H H L H H H H H H H H H H H H H H H H H H H L H Capitulo 3:Análisis y diseño de circuitos combinacionales H H H H H H H H H H H H H H H H H H L 25 Doble decodificador de 2 a 4 líneas 74155 Tabla de funcionamiento X/Y 0 2 1G 1C A B & EN 1 1 3 3 1 14 2C 15 4 9 0 2 1 2G 6 5 2 13 7 10 11 & 2 EN 3 12 1Y0 1Y1 1Y2 1Y3 2Y0 2Y1 2Y2 2Y3 ANSI-IEEE 91-1984 Capitulo 3:Análisis y diseño de circuitos combinacionales Lógica Digital y Microprogramable. Autor: Fernando Remiro Domínguez 26 13 Capítulo 3: Análisis y Diseño de Circuitos Combinacionales Ampliación del 74155 como decodificador de 3 a 8 líneas 3-LINE TO 8-LINE DECODER X/Y A B 13 3 1 0 2 1 9 1 4 G EN 1Y0 6 1Y1 5 6 14 2Y3 7 4 5 2 2Y2 12 3 15 2Y1 11 2 C 2Y0 10 1Y2 4 7 1Y3 Capitulo 3:Análisis y diseño de circuitos combinacionales 27 Circuito comparador 7485 10 12 13 15 4 3 2 9 11 14 1 10 A0 A1 A2 A3 A>B A=B A<B A0 12 A1 13 A2 15 A3 4 3 2 7 6 5 A<B A=B A>B 0 1 2 3 0 1 2 3 B3 ANSI-IEEE 91-1973 A<B A=B A>B 7 A<B 6 A=B 5 A>B B ANSI-IEEE 91-1984 Capitulo 3:Análisis y diseño de circuitos combinacionales Lógica Digital y Microprogramable. Autor: Fernando Remiro Domínguez A > = < 9 B0 11 B1 14 B2 1 B0 B1 B2 B3 COM 28 14 Capítulo 3: Análisis y Diseño de Circuitos Combinacionales Tabla de funcionamiento del comparador 7485 Entradas Entradas Montaje Paralelo A>B A<B A=B Salidas A3,B3 A2,B2 A1,B1 A0,B0 A3>b3 A3<B3 A3=B3 A3=B3 A3=B3 A3=B3 A3=B3 A3=B3 A3=B3 A3=B3 A3=B3 X X A2>B2 A2<B2 A2=B2 A2=B2 A2=B2 A2=B2 A2=B2 A2=B2 A2=B2 X X X X A1>B1 A1<B1 A1=B1 A1=B1 A1=B1 A1=B1 A1=B1 X X X X X X A0>B0 A1>B1 A0=B0 A0=B0 A0=B0 X X X X X X X X H L L X X X X X X X X L H L X X X X X X X X L L H A>B A<B A=B H L H L H L H L H L L L H L H L H L H L H L L L L L L L L L L L H A3=B3 A3=B3 A3=B3 A2=B2 A2=B2 A2=B2 A1=B1 A1=B1 A1=B1 A0=B0 A0=B0 A0=B0 X H L X H L H L L L L H L L H H L L Capitulo 3:Análisis y diseño de circuitos combinacionales 29 Comparador de dos palabras de 8 bit con el 7485 (Conexión en cascada) A7 B7 A6 B6 A5 B5 A4 B4 15 1 13 14 12 11 10 9 A3 B3 A2 B2 A1 B1 A0 B0 A3 B3 A2 B2 A1 B1 A0 B0 15 1 13 14 12 11 A3 B3 A2 B2 A1 B1 10 7485 7485 A<B A=B A>B A<B A=B A>B A<B A=B A>B A<B A=B A>B 7 6 5 2 3 4 7 6 5 2 3 9 A0 B0 4 L H L Entradas Salidas Capitulo 3:Análisis y diseño de circuitos combinacionales Lógica Digital y Microprogramable. Autor: Fernando Remiro Domínguez 30 15 Capítulo 3: Análisis y Diseño de Circuitos Combinacionales Capitulo 3:Análisis y diseño de circuitos combinacionales 31 Circuito Generador de Paridad 74280 TABLA DE FUNCIONAMIENTO A B C D E F G H I 8 2k 9 10 5 11 Σ EVEN 12 13 6 NO. OF INPUTS A-I THAT ARE HIGH Σ EVEN Σ ODD 0, 2, 4, 6, 8 H L 1, 3, 5, 7, 9 L H SALIDAS Σ ODD 1 2 EVEN = PAR 4 ODD = IMPAR Capitulo 3:Análisis y diseño de circuitos combinacionales Lógica Digital y Microprogramable. Autor: Fernando Remiro Domínguez 32 16 Capítulo 3: Análisis y Diseño de Circuitos Combinacionales Estructura interna del circuito generador/detector de paridad 74280 Capitulo 3:Análisis y diseño de circuitos combinacionales 33 Circuito generador/detector de paridad de 25 líneas Capitulo 3:Análisis y diseño de circuitos combinacionales Lógica Digital y Microprogramable. Autor: Fernando Remiro Domínguez 34 17 Capítulo 3: Análisis y Diseño de Circuitos Combinacionales Circuito generador/detector de paridad de 8 líneas Capitulo 3:Análisis y diseño de circuitos combinacionales 35 Diagrama de bloques del circuito de control de una máquina para adivinar un número Capitulo 3:Análisis y diseño de circuitos combinacionales Lógica Digital y Microprogramable. Autor: Fernando Remiro Domínguez 36 18 Capítulo 3: Análisis y Diseño de Circuitos Combinacionales Capitulo 3:Análisis y diseño de circuitos combinacionales 37 Codificador de 16 líneas con salida BCD Capitulo 3:Análisis y diseño de circuitos combinacionales Lógica Digital y Microprogramable. Autor: Fernando Remiro Domínguez 38 19 Capítulo 3: Análisis y Diseño de Circuitos Combinacionales Ampliación de un multiplexor a 32 líneas Capitulo 3:Análisis y diseño de circuitos combinacionales 39 Control de antena parabólica Encoder Circuito de Control Capitulo 3:Análisis y diseño de circuitos combinacionales Lógica Digital y Microprogramable. Autor: Fernando Remiro Domínguez 40 20