Pipeline Organización de Computadoras

Anuncio

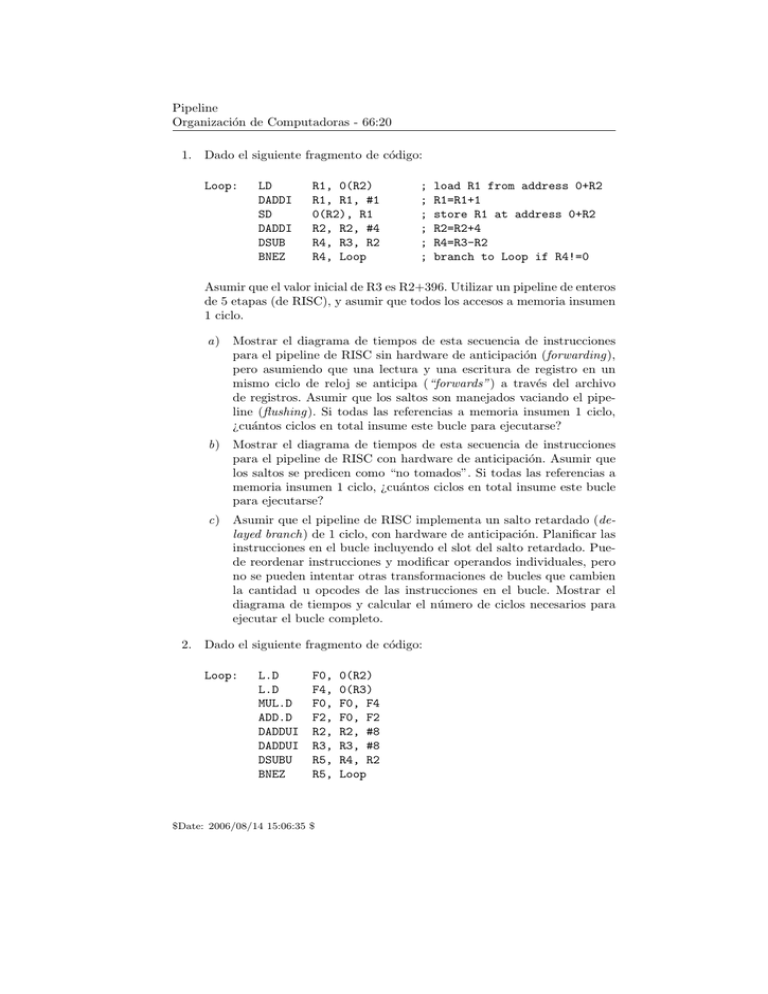

Pipeline Organización de Computadoras - 66:20 1. Dado el siguiente fragmento de código: Loop: LD DADDI SD DADDI DSUB BNEZ R1, 0(R2) R1, R1, #1 0(R2), R1 R2, R2, #4 R4, R3, R2 R4, Loop ; ; ; ; ; ; load R1 from address 0+R2 R1=R1+1 store R1 at address 0+R2 R2=R2+4 R4=R3-R2 branch to Loop if R4!=0 Asumir que el valor inicial de R3 es R2+396. Utilizar un pipeline de enteros de 5 etapas (de RISC), y asumir que todos los accesos a memoria insumen 1 ciclo. 2. a) Mostrar el diagrama de tiempos de esta secuencia de instrucciones para el pipeline de RISC sin hardware de anticipación (forwarding), pero asumiendo que una lectura y una escritura de registro en un mismo ciclo de reloj se anticipa (“forwards”) a través del archivo de registros. Asumir que los saltos son manejados vaciando el pipeline (flushing). Si todas las referencias a memoria insumen 1 ciclo, ¿cuántos ciclos en total insume este bucle para ejecutarse? b) Mostrar el diagrama de tiempos de esta secuencia de instrucciones para el pipeline de RISC con hardware de anticipación. Asumir que los saltos se predicen como “no tomados”. Si todas las referencias a memoria insumen 1 ciclo, ¿cuántos ciclos en total insume este bucle para ejecutarse? c) Asumir que el pipeline de RISC implementa un salto retardado (delayed branch) de 1 ciclo, con hardware de anticipación. Planificar las instrucciones en el bucle incluyendo el slot del salto retardado. Puede reordenar instrucciones y modificar operandos individuales, pero no se pueden intentar otras transformaciones de bucles que cambien la cantidad u opcodes de las instrucciones en el bucle. Mostrar el diagrama de tiempos y calcular el número de ciclos necesarios para ejecutar el bucle completo. Dado el siguiente fragmento de código: Loop: L.D L.D MUL.D ADD.D DADDUI DADDUI DSUBU BNEZ F0, F4, F0, F2, R2, R3, R5, R5, $Date: 2006/08/14 15:06:35 $ 0(R2) 0(R3) F0, F4 F0, F2 R2, #8 R3, #8 R4, R2 Loop Pipeline Organización de Computadoras - 66:20 Asumir que el valor inicial de R4 es R2+792. Utilizar un pipeline de enteros de 5 etapas y un pipeline de punto flotante de MIPS. Si los riesgos (hazards) estructurales son debidos a contienda de escrituras aplazadas (write-back ), asumir que la instrucción más antigua tiene prioridad y otras instrucciones son detenidas. 3. a) Mostrar el diagrama de tiempos de esta secuencia de instrucciones para el pipeline de punto flotante de MIPS sin hardware de anticipación, pero asumiendo que una lectura y una escritura de registro en un mismo ciclo de reloj se anticipa a través del archivo de registros. Asumir que los saltos son manejados vaciando el pipeline. Si todas las referencias a memoria son aciertos en la caché, ¿cuántos ciclos en total insume este bucle para ejecutarse? b) Mostrar el diagrama de tiempos de esta secuencia de instrucciones para el pipeline de punto flotante de MIPS con hardware de anticipación. Asumir que los saltos se predicen como “no tomados”. Si todas las referencias a memoria son aciertos en la caché, ¿cuántos ciclos en total insume este bucle para ejecutarse? Suponer las siguientes frecuencias de saltos (como porcentaje del total de instrucciones): Saltos condicionales Saltos y llamadas 15 % (60 % son tomados) 1% Estamos examinando un pipeline de 4 etapas donde los saltos incondicionales son resueltos al final del segundo ciclo, y los condicionales al final del tercer ciclo. Asumiendo que la primer etapa puede hacerse independientemente del resultado del salto, e ignorando otras situaciones de detenimiento del pipeline, ¿cuánto más rápido serı́a la máquina sin riesgos de salto (branch hazards)? 4. Planificar los slots de los saltos retardados puede mejorar el desempeño. Asumir un único slot de retardo de salto y un pipeline que determina la salida de un salto en la segunda etapa. a) Para una instrucción de salto retardado, ¿cuál es la penalidad para cada esquema de planificación de slot de retardo de salto, si el salto es tomado y si no es tomado, y qué condición, si hay alguna, debe satisfacerse para asegurar la ejecución correcta? b) Una instrucción de salto que “cancela si no es tomado” (cancel-ifnot-taken) no ejecuta la instrucción en el slot de retardo si el salto no es tomado. Ası́, un compilador no necesita ser tan conservador al momento de llenar el slot de retardo. Para cada esquema de planificación, ¿cuál es la penalidad si el salto es tomado y si no es tomado, $Date: 2006/08/14 15:06:35 $ Pipeline Organización de Computadoras - 66:20 y qué condición, si hay alguna, debe satisfacerse para asegurar la ejecución correcta? c) Asumir que un conjunto de instrucciones posee un salto retardado y un salto que “cancela si no es tomado”. ¿Cuándo el compilador deberı́a utilizar cada instrucción de salto, y desde dónde deberı́a llenarse el slot? $Date: 2006/08/14 15:06:35 $