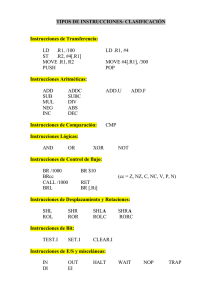

Capítulo 3 Instrucciones y direccionamiento

Anuncio

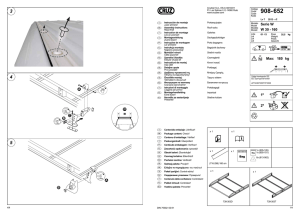

Capítulo 3 Instrucciones y direccionamiento Félix García Carballeira Jesús Carretero Pérez José Daniel Sánchez García David Expósito Singh © Ediciones Paraninfo 1 Código de Registro operación fuente Registro destino Valor inmediato 001000 01000 01010 0000000000000100 addi $t2, $t0, 0x04 Figura 3.1: Ejemplo de instrucción máquina de la arquitectura MIPS y su equivalente en ensamblador © Ediciones Paraninfo 2 ADD_SP Sin uso Figura 3.2: Ejemplo de una instrucción con cero operandos © Ediciones Paraninfo 3 ADDR_SP 7 Sin uso Figura 3.3: Ejemplo de una instrucción con un operando © Ediciones Paraninfo 4 ADD 4 2 Sin uso Figura 3.4: Ejemplo de una instrucción con dos operandos © Ediciones Paraninfo 5 ADDR 4 2 7 Sin uso Figura 3.5: Ejemplo de una instrucción con tres operandos © Ediciones Paraninfo 6 addi Rf Rd 103 103 Figura 3.6: Direccionamiento inmediato © Ediciones Paraninfo 7 add $t1 $t3 $t2 $t2 $t1 sin uso código de en add función $t3 Figura 3.7: Direccionamiento de registro © Ediciones Paraninfo 8 Instrucción lw Memoria $t1, Formato $t2 lw 0x10AD0F82 ($t2) $t1 0 103 Banco de registros 0x10AD0F82 $t1 $t2 Contenido a almacenar en $t1 Figura 3.8: Direccionamiento indirecto de registro © Ediciones Paraninfo 9 Memoria Instrucción ADD_DA 0x10AD0F82 0x10AD0F82 4 103 Operando Figura 3.9: Direccionamiento directo absoluto © Ediciones Paraninfo 10 Instrucción lw Memoria $t1, 4($t2) Instrucción lw $t2 4 $t1 Banco de registros 0x10AD0F00 $t2 Suma Dirección base: 0x10AD0F00 Desplazamiento 0x10AD0F04 103 0x10AD0F04 Dato a almacenar en $t1 Figura 3.10: Direccionamiento directo relativo a registro base © Ediciones Paraninfo 11 Instrucción lw Memoria $t1, 0x10B2($t2) Instrucción lw $t2 $t1 0x1B02 Banco de registros 4 Dirección base: $t2 Suma 0x10B2 Desplazamiento 0x10B6 103 0x1B06 Dato a almacenar en $t1 Figura 3.11: Direccionamiento directo relativo a registro índice © Ediciones Paraninfo 12 Contador de programa Instrucción beqz t0 Sin uso 0x10AD0F00 64 64 x 4 Sumador if (t0==0) 0x10AD1000 Figura 3.12: Direccionamiento relativo a contador de programa en el MIPS © Ediciones Paraninfo 13 Memoria Instrucción LW_DI R4 0x10A00422 0x10A00422 0x10AD0F82 0x10AD0F82 103 Dato a cargar en el registro R4 Figura 3.13: Direccionamiento indirecto © Ediciones Paraninfo 14 Instrucción 0 1 OP Otros campos OP Otros campos Figura 3.14: Ejemplo de campo de extensión © Ediciones Paraninfo 15 Tipo registro Código de operación Registro fuente Registro objetivo Registro destino Desplazamiento función 5 5 5 5 6 6 Tipo inmediato Código de operación Registro fuente Registro objetivo o condición salto 6 5 5 Inmediato, desplazamiento de bifurcación o dirección de desplazamiento 16 Tipo salto Código de operación Dirección destino 6 26 Figura 3.15: Formato de las instrucciones del MIPS32 © Ediciones Paraninfo 16 Código de operación 15 bits Registro 5 bits Dirección 12 bits Figura 3.16: Formato de instrucción del Problema 3.1 © Ediciones Paraninfo 17 COP EXT RD RB Sin uso D 6 1 4 4 1 16 Figura 3.17: Formato de la instrucción del Problema 3.3 © Ediciones Paraninfo 18 ADDI 1011100 111 ADDR 1011000 101 ADDM 1011001 001 ADDRB 1011010 111 ADDPC 1111010 100 1000000000 000 sin uso 1111000000 101 0001100 1001011100 Figura 3.18: Formato de las instrucciones del Problema 3.4 © Ediciones Paraninfo 19 Figura 3.19: Formato de las instrucciones del Problema 3.6 © Ediciones Paraninfo 20 TIPO1 R1 R2 R3 Sin uso 6 3 3 3 1 TIPO2 Sin uso Dir 6 10 16 TIPO3 R1 DESPL 6 3 7 TIPO4 Sin uso Dir 6 10 16 Figura 3.20: Formato de las instrucciones del Problema 3.7 © Ediciones Paraninfo 21 8 2 Sin uso 65KB 8 4 20 32 9 2 1KB 8 4 20 10 2 5 -5KB 8 4 4 16 11 2 Sin uso 65KB 8 4 20 32 Figura 3.21: formato de las instrucciones del Problema 3.9 © Ediciones Paraninfo 22 COP R1 Sin uso Desplazamiento Sin uso 11 5 16 21 11 Figura 3.22: Formato de la instrucción del Problema 3.10 © Ediciones Paraninfo 23