Introducción a la lógica digital

Anuncio

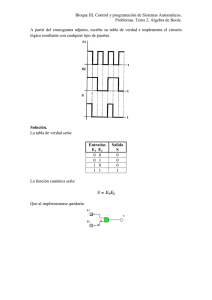

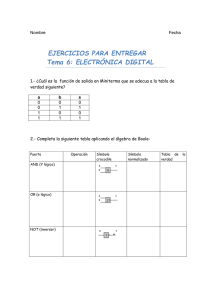

Organización del Computador I Verano Introducción a la lógica digital Basado en el Apéndice B del libro de Patterson y Hennessy Verano 2014 Profesora Borensztejn Señales Digitales • Los transistores operan con dos niveles de voltajes: alto y bajo • Puede haber otros niveles entre esos dos, pero son transitoriosè ocurren cuando se pasa de un valor alto a bajo (o viceversa) • Hay varias y distintas familias lógicas (TTL, CMOS) y cada una define sus valores de voltajes, por ello, en lugar de hablar de niveles de voltajes hablamos de señales. • Señales que son: – Verdaderas, o valen 1 o están activas (asserted) – Falsas, o valen 0 o están inactivas (deasserted) • Los valores 1 y 0 decimos que son inversos entre sí Señales. Verilog • • • • En el diseño de sistemas digitales (procesadores, etc) se utilizan Lenguajes de Descripción de Hardware (HDL). Se utilizan: – Para simular circuitos con una descripción abstracta del hardware – Para sintetizar circuitos , es decir para implementarlos en hardware Verilog es un HDL ampliamente utilizado El tipo básico en Verilog son las señales (wire). Estas pueden ser de un bit o de varios bits. Bloques Lógicos • Se dividen en dos grupos – Los que no utilizan memoria, llamados Combinacionales: • Las salidas dependen únicamente de los valores presentes en las entradas – Los que utilizan memoria, llamados Secuenciales: • Las salidas dependen de las entradas y tambien del valor almacenado en su memoria. • En esta clase nos concentramos en los bloques sin memoria: lógica combinacional Tablas de Verdad • Dado que un bloque lógico combinacional no tiene memoria, puede ser descrito completamente definiendo el valor de las salidas para cada uno de los posibles valores de la entrada. • Por ej: si tenemos n entradas, tendremos 2n combinaciones, o sea, 2n entradas de la Tabla de Verdad Tablas de Verdad Tabla de Verdad para la función igualdad b1 b0 a1 a0 i1 i0 eq 0 0 1 0 1 0 1 0 0 1 1 1 0 0 0 0 0 0 0 0 1 1 1 1 1 1 1 1 0 0 0 0 1 1 1 1 0 0 0 0 1 1 1 1 0 0 1 1 0 0 1 1 0 0 1 1 0 0 1 1 0 1 0 1 0 1 0 1 0 1 0 1 0 1 0 1 eq 1 0 0 0 0 1 0 0 0 0 1 0 0 0 0 1 Algebra de Boole • Las Tablas de Verdad crecen muy rápidamente al aumentar el número de entradas. • Otra manera de describir las funciones lógicas es mediante al algebra de Boole. • En el año 1854, George Boole, matemático inglés, escribió un tratado sobre como usar técnicas algebraicas aplicadas a la lógica. Nadie supo que hacer con eso, hasta que cien años mas tarde, Claude Shannon, ingeniero electrónico y matemático americano, desempolvó el libro de Boole y le pareció adecuado para describir circuitos electrónicos. Algebra de Boole • En el Algebra de Boole todas las variables tienen los valores 0 o 1, y existen 3 operadores: – OR: se escribe con el símbolo + (suma lógica) – AND: se escribe con el símbolo * (producto lógico) – NOT: se escribe con el símbolo A. Es la inversión. Algebra de Boole: Leyes y Teoremas • Leyes de Morgan De Tabla de Verdad a Expresión Lógica De Tabla de Verdad a expresión lógica • Expresamos la función como SUMA de PRODUCTOS: Suma de términos producto • Una función en forma de suma de productos (o producto de sumas) puede ser minimizada. (Mapas de Karnaugh, Simplificaciones algebraicas) • Las minimizaciones y simplificaciones son procesos mecánicos que hoy realizan herramientas automáticamente Puertas Lógicas • Los bloques lógicos se construyen con puertas (gates) que implementan la función AND, OR y NOT. • Las funciones AND y OR son conmutativas y asociativas è las puertas pueden tener múltiples entradas • La función NOT siempre tiene una única entrada. Puertas Lógicas • Las puertas NOT se representan mediante una burbujita simplificada Verilog: assign i1 i0 eq 0 0 1 0 1 0 1 0 0 1 1 1 • La sentencia assign funciona como la lógica combinacional: la salida es continuamente asignada, y un cambio en las entradas produce un cambio en la salida Verilog. Descripción de un circuito combinacional b1 b0 a1 a0 0 0 0 0 0 0 0 0 1 1 1 1 1 1 1 1 0 0 0 0 1 1 1 1 0 0 0 0 1 1 1 1 0 0 1 1 0 0 1 1 0 0 1 1 0 0 1 1 0 1 0 1 0 1 0 1 0 1 0 1 0 1 0 1 eq 1 0 0 0 0 1 0 0 0 0 1 0 0 0 0 1 Bloques Combinacionales: Decodificador Bloques Combinacionales: Multiplexor • Multiplexor de dos entradas Arrays de Bloques Lógicos FIGURE B.3.6 A multiplexor is arrayed 32 times to perform a selection between two 32-bit inputs. Note that there is still only one data selection signal used for all 32 1-bit multiplexors. Copyright © 2014 Elsevier Inc. All rights reserved. 18 Verilog: construcción always@ • Cuando la lógica combinacional es compleja, usar assign es tediosoèVerilog provee una construcción que permite especificar estructuras de control : if then else, case Verilog: MIPS ALU • Es lo que vamos a hacer… poco a poco. FIN Lógica Digital