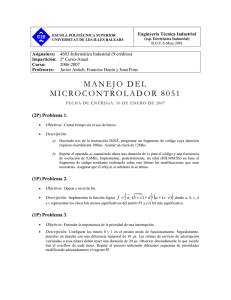

PRACTICA N0. 10

Anuncio

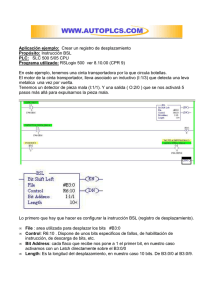

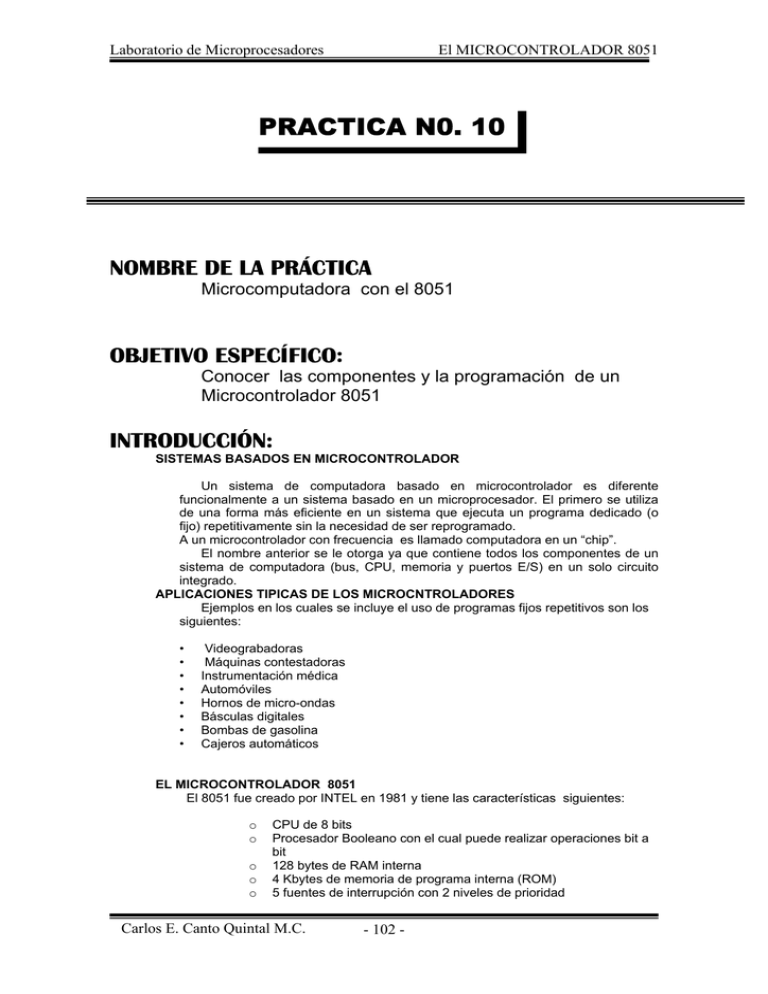

Laboratorio de Microprocesadores El MICROCONTROLADOR 8051 PRACTICA N0. 10 NOMBRE DE LA PRÁCTICA Microcomputadora con el 8051 OBJETIVO ESPECÍFICO: Conocer las componentes y la programación de un Microcontrolador 8051 INTRODUCCIÓN: SISTEMAS BASADOS EN MICROCONTROLADOR Un sistema de computadora basado en microcontrolador es diferente funcionalmente a un sistema basado en un microprocesador. El primero se utiliza de una forma más eficiente en un sistema que ejecuta un programa dedicado (o fijo) repetitivamente sin la necesidad de ser reprogramado. A un microcontrolador con frecuencia es llamado computadora en un “chip”. El nombre anterior se le otorga ya que contiene todos los componentes de un sistema de computadora (bus, CPU, memoria y puertos E/S) en un solo circuito integrado. APLICACIONES TIPICAS DE LOS MICROCNTROLADORES Ejemplos en los cuales se incluye el uso de programas fijos repetitivos son los siguientes: • • • • • • • • Videograbadoras Máquinas contestadoras Instrumentación médica Automóviles Hornos de micro-ondas Básculas digitales Bombas de gasolina Cajeros automáticos EL MICROCONTROLADOR 8051 El 8051 fue creado por INTEL en 1981 y tiene las características siguientes: o o o o o CPU de 8 bits Procesador Booleano con el cual puede realizar operaciones bit a bit 128 bytes de RAM interna 4 Kbytes de memoria de programa interna (ROM) 5 fuentes de interrupción con 2 niveles de prioridad Carlos E. Canto Quintal M.C. - 102 - Laboratorio de Microprocesadores o o o o o o o El MICROCONTROLADOR 8051 32 bits de entrada/salida direccionables bit a bit 1 puerto serie Full dúplex (UART) 2 Contadores-Temporizadores de 16 bits programables 1 oscilador para las señales de reloj Posibilidad de direccionar hasta 64Kbytes de memoria de programa externa Posibilidad de direccionar hasta 64Kbytes de memoria de datos externa varias velocidades desde 12MHz Posteriormente han sido desarrolladas otras versiones del 8051 con distintas características de RAM, ROM, etc.. ARQUITECTURA INTERNA DEL 8051 Entradas a contadores Interrupciones externas 128 128 bytes bytes RAM RAM SFR 4K 4K ROM ROM Controlador Controlador de de interrupciones interrupciones Timer0 Timer0 Timer1 Timer1 Interrupciones internas 8051 8051 CPU CPU Control Control del del bus bus OSC OSC RD 44 Puertos Puertos E/S E/S (32 (32 líneas) líneas) WR P0 P2 P1 P3 Puerto Puerto serie serie TxD RxD Bus de datos/direcciones LA DISTRIBUCIÓN DE MEMORIA DEL 8051 El 8051 está diseñado en base a lo que se conoce como Arquitectura Hardvard. Dicha arquitectura divide el espacio total de memoria en dos áreas distintas: de código o de programa y de datos. MEMORIA DE CODIGO O DE PROGRAMA. El 8051 tiene 4096 bytes de memoria de código interna. El rango se puede incrementar, usando memoria externa, hasta un total de 64 KB. MEMORIA MEMORIA DE DE PROGRAMA PROGRAMA DEL DEL 8051 8051 FFFF FFFF 60 60K K Bytes Bytes Externa Externa El tamaño de la memoria de programa externa puede ampliarse hasta 64kbytes. O 1000 & 0FFF 0000 4K 4KBytes Bytes Interna Interna Los primeros 4k (8 K para el 8052 ) pueden residir en el chip. Carlos E. Canto Quintal M.C. - 103 - 0000 64 64K K Bytes Bytes Externa Externa Laboratorio de Microprocesadores El MICROCONTROLADOR 8051 MEMORIA DE DATOS INTERNA. La capacidad de memoria de datos interna es de 256 bytes. La mitad baja, 128 bytes, se usa para almacenamiento por el programa de variables de datos. La parte superior se reserva para los Registros de Funciones Especiales (SFR). Memoria de Datos Interna FFH 128 bytes Más altos 80H 7FH 128 bytes Más bajos 00H Accesible Accesible Accesible Accesiblesolo solocon con Solo Solo con con Direccionamiento Direccionamiento Direccionamiento Direccionamiento Directo Directo Indirecto Indirecto Accesible Accesiblecon con Direccionamiento Direccionamiento Directo DirectoeeIndirecto Indirecto Registros de Función Especial Puertos Bits de status y control Registros de Timers Stack pointer Acumulador Etc. REGISTROS DE FUNCIONES ESPECIALES. Los SFRs se usan para almacenar los valores, en bytes, que controlan la operación del 8051. Aquellos registros cuya dirección es divisible por 8 se puede direccionar por bit. El espacio de memoria para los SFRs está contenido de los bytes 128 (80H) al 255 (FFH). Este espacio de memoria es accesible solo a través de direccionamiento directo. Algunas de las direcciones en el espacio de SFRs son direccionables tanto en forma de byte como de bit. Así que otras solo son direccionables en forma de byte. Estos registros tienen valores que el 8051 utiliza conforme ejecuta instrucciones. MEMORIA DIRECCIONABLE POR BIT. Aparte de los SFRs direccionables por bit, también se pueden direccionar 16 bytes de memoria interna de datos de esta manera. Esto le permite al programador manipular los datos en un sentido bit a bit, lo cual es una de las características más sobresalientes del 8051. MEMORIA EXTERNA DE DATOS. Si se requiere de más memoria para almacenamiento de datos, el 8051 puede direccionar en forma externa un adicional de 64 KB de RAM. FFFFH Relación de áreas de almacenamiento en el µC 8051 FFFFH El 8051 tiene espacios de direcciones separados para memoria de programa y memoria de datos. Externa Externa Externa Externa 1000H 0FFFH FFH Interna Internaoo externa externa 0000H Memoria de programas 80H 7FH 0000H 00H Memorias de Datos Interna Carlos E. Canto Quintal M.C. Espacio de Registros de Función Especial SFR - 104 - Memorias de Datos Externa Laboratorio de Microprocesadores El MICROCONTROLADOR 8051 DIAGRAMA FUNCIONAL DE PINES DEL 8051 El 8051 se encuentra disponible en un encapsulado tipo DIP de 40 pines. Sus VCC VSS RST/VPO XTAL1 PUERT0 0 XTAL2 EA/VDD ALE/PROG PSEN RXD TXD 8031 8031 PUERT0 1 INT0 INT1 PUERT0 3 T0 PUERT0 2 T1 WR RD FUNCIONES ALTERNAS DE LOS PUERTOS DEL 8051 Cada uno de los puertos de E/S tiene una función alternativa que le permite mayor versatilidad al 8051. El Puerto 0 sirve para multiplexar la parte baja de direcciones y al bus de datos durante el acceso a código y memoria de datos externos. El Puerto 1 tiene funciones alternativas solo en el 8052. Los bits 0 y 1 sirven como T2 y T2EX respectivamente. El Puerto 2 emite el byte de la parte alta de direcciones durante el acceso a memoria, de código o datos, externa que utiliza direcciones de 16 bits. El puerto 3 tiene las funciones listadas en seguida: P3.0 P3.1 P3.2 P3.3 P3.4 P3.5 P3.6 P3.7 RXD (Entrada de puerto serie) TXD (Salida de puerto serie) INT0 (Interrupción externa 0) INT1(Interrupción externa 1) T0 (Entrada para temporizador 0) T1 (Entrada para temporizador 1) WR (pulso de escritura para memoria ext.) RD (pulso de lectura para memoria ext) MIEMBROS Y PRODUCTOS DE LA FAMILIA MCS-51 Los tres miembros originales de la familia son el 8031, 8051 y 8751, en seguida se describen sus características. 8031 y 8051. • Estos dispositivos proveen una solución efectiva en costo para aquellas aplicaciones de control que requieren de hasta 64 KB de código y/o 64 KB de almacenamiento. El 8031 contiene: • 128 bytes de memoria de datos de lectura/escritura • 32 líneas de E/S bidireccional (4 puertos) • dos contadores/temporizadores de 16 bits • Una estructura de interrupciones con dos niveles de prioridad y cinco fuentes • Puerto serie de E/S programable • Oscilador integrado con circuitería de reloj Carlos E. Canto Quintal M.C. - 105 - Laboratorio de Microprocesadores El MICROCONTROLADOR 8051 El 8051 tiene todas las características del 8031 más 4 KB de memoria de código de solo lectura, no volátil. El 8751 es una versión EPROM del 8051, tiene todas las características del 8031 más 4 KB de memoria de código de solo lectura, programable y borrable. VERSIONES CHMOS Los dispositivos anteriores se encuentran disponibles en una versión CHMOS de ahorro de energía: 80C31, 80C51 y 87C51 respectivamente. Estos dispositivos CHMOS operan a una velocidad mayor, tiene una mayor densidad de transistores y consumen menos potencia que los dispositivos previamente listados. Cada uno de estos componentes tiene la misma funcionalidad que su equivalente estándar más dos modos seleccionables mediante programación que reducen el consumo de potencia: Espera (Idle) y Potencia Baja (Power Down). Estos modos hacen de dichos componentes ideales para aplicaciones operadas por batería. MODO DE ESPERA (IDLE) Este modo congela al CPU mientras que permite que continúen funcionando la memoria RAM, contadores, puerto serie y sistema de interrupciones. MODO DE POTENCIA BAJA Este modo protege el contenido de memoria RAM, pero congela el oscilador, causando que todas las demás funciones del chip no operen. Miembros de la subfamilia 8052 y 80C51FA El 8032 y el 8752 son productos subfamiliares del 8052. El 83C51FA y el 87C51FA son miembros del 80C51FA así como el 83C51FB y el 87C51FB son miembros de la subfamilia del 80C51FB. 8032, 8052 y 8752. El 8052 tiene 8 KB de ROM programada de fábrica y el 8032 es una versión sin ROM del 8052, mientras que el 8752 tiene 8 KB de memoria de programa EPROM. Sus características se listan en seguida: • 256 bytes de memoria de datos de lectura/escritura • 32 líneas bidireccionales de E/S (4 puertos) • 3 temporizadores/contadores de 16 bits • Estructura de interrupciones con dos niveles de prioridad y seis fuentes originadoras. • Puerto serie programable de E/S • Oscilador integrado con circuitería de reloj 83C51FA, 80C51FA y 87C51FA El 8032, 8052 y 8752 también tienen sus versiones CHMOS: 83C51FA y FB, 80C51FA y FB y 87C51FA y FB, respectivamente. Estos dispositivos presentan características similares a los anteriores CHMOS. Los dispositivos FB son versiones compatibles con la serie FA, pero tienen 16 KB de ROM, además se incluye una nueva característica el Arreglo de Contador Programable. ARREGLO DE CONTADOR PROGRAMABLE (PCA) Consiste de un contador de 16 bits y cinco módulos de 16 bit de comparación/captura. Estos últimos comparten los pines P1.2 a P1.7. Cada módulo tiene su propio registro de modo, CCAPMn, que se utiliza para configurar el módulo n. Cada módulo puede programarse como: • Modulador de ancho de pulso (usado para conversión d/a) • Registro de comparación/captura (para medición muy precisa en tiempo real de ancho de pulso) • salida de alta velocidad Carlos E. Canto Quintal M.C. - 106 - Laboratorio de Microprocesadores El MICROCONTROLADOR 8051 Adicionalmente, el módulo 4 se puede programar para actuar como un temporizador tipo Perro Guardián (Watchdog Timer). El PCA puede generar una interrupción cuando se programa como temporizador ó como registro de comparación/captura. OTROS PARIENTES DE LA FAMILIA 8051 Existen otros componentes que han tomado la base del microcontrolador 8051 y le han sumado alguna otra funcionalidad. Estos componentes híbridos se conocen como proliferaciones. Los siguientes componentes utilizan la arquitectura del 8051 así como un controlador de comunicaciones serie en el caso del 8X44, un controlador de comunicaciones serie de alta velocidad en el 8XC152 y un controlador de periféricos en el 8XC452. Sumario de la Familia 8051 Nombre 8051 80C51 8052 83C51FA 83C51FB 83C152 83C452 8044 Versión sin ROM 8031 80C31 8032 80C51FA 80C51FB 80C152 80C452 8344 Versión EPROM 8751 87C51 8752 87C51FA 87C51FB 87C152 87C452 8744 Bytes en ROM 4K 4K 8K 8K 16K 8K 8K 4K Bytes enRAM 128 128 256 256 256 256 256 192 Timers 2 2 3 3 2 2 2 2 TEMPORIZADORES/CONTADORES El 8051 tiene dos temporizadores/contadores de 16 bits, cada uno de ellos puede operar en cuatro modos, dándole un rango amplio de opciones para resolver muchos problemas diferentes. Los registros de funciones especiales TL0 y TH0 son los bytes alto y bajo del temporizador/contador 0. El temporizador 1 está formado por TL1 y TH1. Cada uno puede programarse para usar ciclos de máquina (temporizador) ó señales externas en su pin de puerto (contador), como fuente de conteo. fxtal fosc= fxtal Xtal1 Xtal1 Xtal2 Xtal2 Oscilador Oscilador interno interno fxtal / 12 ::12 12 C/T=0 timer Conteo Conteoinicial inicial CONTADOR CONTADOR CLK OVF C/T=1 contador TF0 TF0 Tx Tx Genera Genera Interrupción Interrupción GATE GATE CC/ /TT TRx TRx INTx INTx Un temporizador cuenta hacia arriba desde su valor inicial hasta que llega a un sobreflujo. Al ocurrir se pone a uno la bandera correspondiente (TF0 ó TF1), y el conteo continúa. TF0 y TF1 se encuentran en el registro TCON. Carlos E. Canto Quintal M.C. - 107 - Laboratorio de Microprocesadores El MICROCONTROLADOR 8051 REGISTRO PARA CONTROL DE LOS TEMPORIZADORES (TCON) Un temporizador puede ser escrito ó leído en cualquier momento. El bit TR0 es el interruptor de funcionamiento para el temporizador 0: si se pone a 1 se enciende el temporizador 0. TR1 hace lo mismo para el temporizador 1. Estos bits se pueden accesar en forma independiente. Modo 0. (Contador de 8 bits con Pre-escalamiento de 5 bits) Este modo es el de omisión después de inicializar el procesador (reset). El byte bajo utiliza solo cinco bits para ejecutar un pre-escalamiento ó división por 32 en la fuente de conteo. Cada uno de sus sobreflujos suma una cuenta al byte alto. Se pueden programar tanto el byte alto como el bajo. Al escribir los valores iniciales adecuados se puede ajustar el sobreflujo sobre un rango de 1 a 8 K (1 uS a 8.19 mS con un reloj de 12 Mhz). Interrupciones de los temporizadores La bandera de sobreflujo para cada temporizador sirve también como el flip-flop de petición de interrupción para ese temporizador. Si el bit de habilitación de interrupción es uno (Etx para el temporizador x) y EA=1, la ejecución del programa saltará a la localidad del vector de interrupción del temporizador correspondiente (por supuesto que al finalizar de ejecutar la instrucción actual, y si no se esta dando servicio a otra interrupción de igual o mayor prioridad). El hardware limpia la bandera Tfx, cuando salta hacia la rutina de servicio de interrupción del temporizador x. El uso de una interrupción (en lugar de consulta) para disparar algún proceso después de un retardo requerido permite que se manejen otros procesos durante el retardo. Modo 1. (Contador de 16 bits) En este modo, TLx se pone en cascada con THx, dando un rango máximo de conteo de 64 K, ó 65 ms (a 12 Mhz). Si se escriben valores iniciales en THx y Tlx, la cuenta antes del sobreflujo puede ajustarse tan baja como una. Carlos E. Canto Quintal M.C. - 108 - Laboratorio de Microprocesadores El MICROCONTROLADOR 8051 Se puede utilizar para el conteo ya sea ciclos de máquina ó la entrada externa. La bandera de sobreflujo se puede utilizar para consultarse ó para generar una interrupción. Modo 2. (Contador de 8 bits con auto-recarga) En este modo el conteo se hace solo por Tlx (ocho bits). THx se carga por el programa con un valor que el hardware cargará en TLx cada vez que exista sobreflujo. La cuenta antes del sobreflujo se puede seleccionar entre uno y 256 (cargar 0 para obtener una cuenta de 256). Se puede utilizar para el conteo ya sea ciclos de máquina ó la entrada externa. La bandera de sobreflujo se puede utilizar para consultarse ó para generar una interrupción. Modo 3: caso especial. Este es el único modo en el que los dos temporizadores se comportan de una forma diferente el uno del otro. Al colocar el temporizador 0 en modo 3 se divide en dos unidades de ocho bits: TL0 se convierte en un contador/temporizador de 8 bits y TH0 en un temporizador únicamente de 8 bits (no usa el pin externo de entrada). TL0 utiliza el bit de puesta en marcha, la bandera de sobreflujo y el pin externo de entrada del temporizador 0. TH0 utiliza el bit de puesta en marcha y la bandera de sobreflujo del temporizador 1 (incluyendo el vector de interrupción asociado). El temporizador 1 corre libremente si se encuentra en los modos 0, 1 ó 2 cuando el temporizador 0 se pone en modo 3. El temporizador 1 se desactiva al ponerlo en modo 3. Carlos E. Canto Quintal M.C. - 109 - Laboratorio de Microprocesadores El MICROCONTROLADOR 8051 DISPARO DE LOS TEMPORIZADORES. Cada temporizador tiene un bit en el registro TMOD que es el control de disparo. Al inicio el bit es 0, el disparo se encuentra apagado, y los temporizadores se activa y desactivan como ya se ha descrito. Cuando el bit de disparo (gate) se pone a uno, el temporizador se activa solo cuando tanto su bit de puesta en marcha (Trx) y su correspondiente entrada externa de interrupción se encuentran en uno. Esto le permite al temporizador medir la duración de pulsos aplicados a su entrada (pin) de interrupción en términos de la fuente de conteo del temporizador. También, la misma entrada continuará disparando la interrupción externa correspondiente, si se encuentra habilitada. La rutina de servicio de interrupción puede leer (y poner a cero) la cuenta acumulada mientras la señal permaneció en alto. El registro TMOD selecciona las opciones. TMOD es el registro de selección de MODo de los temporizadores; es un SFR que se encuentra en la dirección 89H. Su cuatro bits más significativos seleccionan las opciones para el temporizador 1, y los cuatro bits más bajos hacen lo mismo para el temporizador 0. Este registro no se puede accesar por bits. Los bits 0 y 1 de cada nibble seleccionan el modo (0, 1 ,2 ó 3) para cada temporizador. El bit 2 selecciona si el temporizador cuenta ciclos de máquina (bit=0) ó cuenta pulsos externos (bit=1). El bit 3 es el control de disparo para el temporizador: un 1 activa el modo de disparo. En la función de “contador”, el registro TLx se incrementa en respuesta a una transición de 1 a 0 en el pin externo de entrada Tx. La razón máxima de conteo es 1/24 de la frecuencia del cristal. TMOD PUERTO SERIE Carlos E. Canto Quintal M.C. - 110 - Laboratorio de Microprocesadores El MICROCONTROLADOR 8051 El puerto serial es un puerto “FULL DUPLEX” , lo cual significa que puede transmitir y recibir datos simultáneamente . El receptor contiene un almacén “Buffer”, que le permite comenzar a recibir un segundo dato sin necesidad de que el primero haya sido completamente leído del registro Buffer. Sin embargo si el primer byte permanece sin ser leído hasta el final de la recepción del segundo dato, éste se perderá. Tanto el dato recibido como el transmitido son depositados en el registro SBUF del SFR (espacio de funciones especiales). REGISTRO DE CONTROL DEL PUERTO SERIAL SCON El puerto Serie puede ser operado en 4 modos diferentes que son especificados con los bits SM0 y SM1 del registro de Control del Puerto Serie (SCON) SMO SM1 SM2 SCON.7 SCON.6 SCON.5 REN SCON.4 TB8 SCON.3 RB8 SCON.2 TI SCON.1 RI SCON.0 Especifica el modo de control del puerto serie. Especifica el modo de control del puerto serie. Habilita la comunicación del tipo "multiprocesador" utilizado en los modos 2 y 3. En estos modos, si SM2 = 1, RI no es activado si el noveno dato recibido (RB8) es 0. En modo 1, RI no es activado si no se recibe un bit de stop. En el modo 0, SM2 será 0. Establece la recepción serie, cuando REN = 0 se desactiva la recepción ( por software ). Almacena el noveno bit que será transmitido en los modos 2 y 3 . Es el noveno bit que fue recibido en los modos 2 y 3 . En el modo 1, si SM2 = 0, RB8 es el bit de stop recibido. En el modo 0 RB8 no es usado. Bandera de interrupción de la transmisión. Activada por hardware al final del octavo bit en el modo 0, o al principio del bit de stop en los otros modos. Debe ser limpiado por software. Bandera de interrupción de la recepción. Activada por hardware al final del octavo bit en el modo 0, o al medio tiempo de trasmitido el bit de stop en los otros modos.Debe ser limpiado por software. MODOS DE OPERACIÓN DEL PUERTO SERIE El UART del 8051 puede ser operado en un modo síncrono y 3 modos asíncronos EL MODO 0. Los datos seriales que entran o salen a través de RxD o TxD respectivamente, lo hacen mediante 8 corrimientos, con una frecuencia de transmisión (Baud Rate) fija Carlos E. Canto Quintal M.C. - 111 - Laboratorio de Microprocesadores El MICROCONTROLADOR 8051 de de 1/12 de la frecuencia del oscilador. La figura Modo 0. muestra el Puerto Serie en La transmisión es iniciada por cualquier instrucción que utilice SBUF como registro de “Destino”, v.gr. MOV SBUF,A . Para que la recepción pueda ser iniciada se debe cumplir la condición REN=1 y RI=0. Bus Businterno internode dedatos datos “1” RXD RXD escritura al SBUF DATO TRANSMITIDO Buffer Bufferserial serial SBUF SBUF D Q clk estados S6 de los ciclos de máquina MSB LSB Detector Detectorde decero cero TI Control ControlTX TX start reloj TXD TXD shift enviar Shift clk RELOJ DE SINCRONÍA CON RECEPTOR Señal Señalde deinterrupción interrupción del delpuerto puertoserial serial RI Control ControlRX RX recibir La recepción es iniciada por la detección de un transiente negativo (de 1 a 0) en la línea RxD, la cual es muestreada a una frecuencia de 16 veces la frecuencia de “Baud Rate” que ha sido establecida. Cuando un transiente es detectado el divisor entre 16 es inmediatamente reestablecido y 1FFH es escrito en la entrada del registro de corrimiento. OPERACIÓN SERIE ASÍNCRONA Los modos de comunicación serie del 8051 pensados para comunicación entre procesos ó entre sistemas son asíncronos. Esto significa que el dispositivo transmisor envía datos solos, sin una señal de sincronización. Tramas de datos: El puerto serie del 8051 puede utilizar tramas de datos que contengan ya sea 8 ó 9 bits de datos. El UART siempre le suma un bit de inicio, que es bajo, y un bit de paro, que es alto. El UART pone la línea de salida serial a un alto siempre que no 8 bits de datos Línea ociosa 0 b0 b1 b2 b3 b4 b5 b6 b7 1 Bit de parada Bit de arranque se está enviando ninguna trama. El programa debe iniciar la transmisión de cada trama que se vaya a enviar (por ende controla el tiempo de retardo entre las tramas enviadas). Pero el UART maneja la transmisión bit a bit (y la recepción), sin involucrar a la CPU. Carlos E. Canto Quintal M.C. - 112 - Laboratorio de Microprocesadores El MICROCONTROLADOR 8051 El registro de corrimientos de transmisión recibe una “onda cuadrada” del generador de baudaje. Cada bit de dato en una trama (incluyendo los bits de inicio y paro) se aplica al pin TXD por 16 de estos pulsos. El circuito de recepción (si está habilitado) espera una transición de bajada que señale el comienzo de un bit de inicio y con esto una nueva trama. Utiliza los pulsos de su generador de baudaje para determinar cual debería ser el centro de cada bit esperado. Toma tres muestras alrededor de este punto, y recorre este valor, basándose en dos de tres de dichas muestras. SBUF: El registro (buffer) del puerto serie. SBUF=fuente copia el dato de fuente al registro de corrimiento de transmisión de datos y, también, es el comando de inicio de transmisión; el registro de transmisión es de solo escritura. destino =SBUF lee el dato del registro de recepción; el cual es de solo lectura. Los dos registros de datos del puerto serie, uno para transmitir y otro para recibir, tienen el mismo nombre, SBUF, y la misma dirección, 99H en el espacio de SFR. Cual de ellos se accesa, se especifica por el hecho de que si se lee ó se escribe. Los circuitos de transmisión y recepción son independientes, así que la transmisión y recepción pueden proceder en forma simultánea (full duplex) mientras que el CPU maneja un tercer proceso. El modo del puerto serie y otras opciones se seleccionan al ajustar bits en el byte de control, el cual se denomina SCON (98H en el espacio SFR). Que también contiene al bit que habilita la recepción serie de datos. MODOS ASÍNCRONOS Carlos E. Canto Quintal M.C. - 113 - Laboratorio de Microprocesadores El MICROCONTROLADOR 8051 El 8051 provee tres modos serie de comunicación asíncrona para interfaz con otros procesadores ó sistemas. En los tres modos, el circuito de transmisión se encarga de generar un bit de inicio y un bit de paro. Modo 1: Dato de 8 bits con velocidad variable. Se transmiten por la línea (TxD) o se reciben por línea (RxD) 10 bits. Un bit de inicio (Start bit de nivel 0 lógico). En recepción el bit de Fin (Stop), se almacena en RB8 de SCON, si SM2=0. El Baud Rate (frecuencia de transmisión o recepción) es variable. Se utiliza el temporizador 1 como parte del generador de baudaje, así que programándolo con diferentes valores de recarga, el baud-rate puede ajustarse de 122 a 62500 bits por seg (bps), con un cristal de 12 Mhz. (Esto asume usar el temporizador 1 en modo 2, para autorecarga). Se puede duplicar el baud-rate al poner en uno el bit SMOD del registro PCON. El uso del octavo bit (así como de los otros siete) se controla por el programa para ajustarse a la aplicación. En algunos protocolos se utiliza para el bit de paridad, algunas veces como un segundo bit de paro, etc. Modo 2: Dato de 9 bits con velocidad fija. 11 bits son transmitidos (TxD) o recibidos (RxD), un bit de inicio (Start bit de nivel 0 lógico), 8 bits de datos, un noveno bit de datos programable, en la transmisión es TB8, en la recepción es RB8 de SCON, y un bit de Fin (Stop bit). Su Baud Rate es de 1/32 o 1/64 de la frecuencia de oscilación. Es igual al modo 3, a excepción de que no se utiliza el temporizador 1 como parte del generador de baud-rate. Así el temporizador 1 puede utilizarse en otras cosas a expensas de un baud-rate fijo, lo cual no es un problema para la comunicación entre varios 8051s. En los modos 2 y 3 el noveno bit se puede utilizar para distinguir entre una trama de datos y una de dirección en una comunicación multiprocesadores. Modo 3: Dato de 9 bits con velocidad variable. 11 bits son transmisión (TxD) o recibidos (RxD), en la misma forma que el modo 2, sólo que aquí la frecuencia de transmisión/recepción (Baud Rate) es variable. Se utiliza el Timer 1 para generar el Baud Rate. En los 4 modos, la transmisión es inicializada cuando SBUF es utilizado como registro destino. La recepción en el modo 0 comienza cuando RI=0, en los otros modos, cuando se detecta el bit de inicio (START) si REN=1. Trabaja como el modo 1, excepto que en lugar de ocho, se transmiten o reciben nueve bits de datos. Los ocho bits bajos van o vienen del SBUF, pero el noveno tiene dos espacios en SCON: TB8 para la transmisión y RB8 para la recepción. Este último bit puede utilizarse para ajustarse a protocolos especiales. Por ejemplo el TTY estándar requiere de dos bits de paro, un bit de paridad y siete bits de datos. Programación del puerto serie Para programar el puerto serie, se debe seleccionar el modo y baud-rate apropiado para la aplicación, calcular el valor de recarga necesitado para el temporizador y finalmente programar el SCON y temporizador 1. Después de escoger entre un esquema de encuesta contínua (sondeo) ó manjeo de interrupción, se escribe el programa para el proceso de transmisión/recepción. Generación del baud-rate. MODO FORMULA CON CRISTAL DE 12 MHz 0 Baud rate=Osc/12 1 Mbps Carlos E. Canto Quintal M.C. - 114 - Laboratorio de Microprocesadores 1, 3 2 El MICROCONTROLADOR 8051 Baud rate=Osc/( 12*2*16*(256-TH1) ) 31250/(256-TH1) bps Baud rate= Osc*2SMOD/64 187.5 Kbps Para los modos 1, 2 y 3 el baud-rate se duplica si el bit siete de PCON (SMOD) se pone a uno. SCON: El control del puerto serie. SM0 SM1 SM2 REN TB8 RB8 TI RI SM0, SM1: seleccionan el modo de operación. SM2: Deshabilita la recepción de tramas para las cuales el bit 8 es cero. REN: Habilita y deshabilita la recepción de datos. TB8: Determina el estado del noveno bit transmitido en modo UART de 9 bits. RB8: Indica el estado del noveno bit recibido. TI: Se pone a uno, por el circuito, cuando se esta transmitiendo. RI: Se pone a uno, por el circuito, cuando se ha recibido un byte. Debe limpiarse por software. INTERRUPCIONES La estructura de interrupciones del 8051 provee una herramienta poderosa que permite al CPU el manejar un número de procesos diferentes “concurrentemente”, siempre y cuando cada proceso necesite solo una fracción del tiempo del CPU. Concurrentemente significa manejar cada proceso con un tiempo de respuesta lo suficientemente rápido, de tal forma que el proceso funcione tan bien como si tuviera un procesador dedicado para él. Esto es, el trabajo para diferentes procesos se realiza en realidad secuencialmente pero parece serlo en paralelo. El 8051 provee interrupciones para los periféricos y también dos interrupciones de fuentes externas. • La función de las Interrupciones de Hardware • Estructura de Interrupciones del 8051 • Ejemplos de Utilización de Interrupciones • Latencia de una Interrupción • Opciones para las Interrupciones Externas La función de las Interrupciones de Hardware Esta sección muestra un ejemplo de como una interrupción puede ahorrar tiempo del CPU, y permitir lo que parece ser “procesamiento paralelo”. Se discute el sistema general para las interrupciones de hardware utilizado por los microprocesadores y lo compara con el mecanismo de una subrutina. ENTRADA/SALIDA MANEJADA POR INTERRUPCIONES Muchos dispositivos de Entrada/Salida (impresoras, modems, etc) requieren solo de una pequeña fracción de tiempo de CPU para servicio. Si, por ejemplo, se inicializa un dispositivo como una impresora, que requiere miles de ciclos de máquina para imprimir cada caracter, podría enviar una señal que indique cuando está lista para recibir otro caracter. El 8051 podría “consultar” (polling) el pin de un puerto que se encontraría conectado a la señal de “listo” de la impresora, pero de esta forma el 8051 estaría gastando miles de instrucciones entre el envío de cada caracter. Si la línea de “listo” (ready) se conecta a una entrada de interrupción externa, el 8051 puede ocuparse de otros procesos hasta que la impresora se encuentre lista para otro caracter. Entonces, se interrumpe al 8051, la ejecución salta a la rutina Carlos E. Canto Quintal M.C. - 115 - Laboratorio de Microprocesadores El MICROCONTROLADOR 8051 de servicio de interrupción (ISR) apropiada, la cual envía el siguiente caracter y la ejecución regresa a cualquiera que sea el proceso que fue interrumpido. Se le da servicio a la impresora (casi exactamente) tan rápido como si el CPU solo estuviera dedicado a ella; pero otros procesos también se están ejecutando concurrentemente. ESTRUCTURA DE INTERRUPCIONES DEL 8051 Fuentes de Interrupción y Vectores. Para cada fuente de interrupción el hardware tiene una dirección de código en particular (vector de interrupción) que carga en el Contador de Programa (PC) cuando se actúa en dicha interrupción. La primera instrucción de la ISR para esa interrupción debe estar en la localidad de ese vector. Ya que solo se tienen 8 bytes entre los vectores, con frecuencia se utiliza una instrucción JMP para ir a otra área de memoria de código. Las siguientes sentencias asumen que todas las interrupciones se encuentran habilitadas. * Interrupción externa 0 (función alternativa de entrada para la terminal P3.2, tambien llamada INT0) causa el salto de ejecución hacia la 03H. * La interrupción del Temporizador 0 causa el salto de ejecución a la 0BH. * Interrupción externa 1 (función alternativa de entrada para la terminal P3.3, también llamada INT1) causa el salto de ejecución hacia la 1BH. * La interrupción del Temporizador 1 causa el salto de ejecución a la 1BH. * La interrupción del puerto serie (entrada ó salida) causa el salto de ejecución a la 23H * La interrupción del Temporizador 2 causa el salto de ejecución a la 2BH, solo disponible en el 8052 y 80C51FA. * La interrupción del Arreglo Programable de Contadores causa el salto de ejecución a la 33H; solo disponible en el 80C51FA. * La reinicialización del micro (Reset) causa un salto en la ejecución a la 00, así como la inicialización de la mayoría de los SFR. Se puede pensar como una interrupción especial externa con vector en 0, y el programa completo como una ISR. Secuencia de Procesamiento de una Interrupción Cuando ocurre una petición de interrupción, siempre debe terminar la instrucción que actualmente se este ejecutando antes de que el hardware pueda saltar hacia la ISR. El hardware procede con las siguientes pruebas antes de que termine la instrucción: * Si la interrupción no se encuentra habilitada individualmente ( por su bit en el SFR IE), se ignora la petición de interrupción y la ejecución se continúa en forma secuencial. Carlos E. Canto Quintal M.C. - 116 - Laboratorio de Microprocesadores El MICROCONTROLADOR 8051 * Si las interrupciones no están habilitadas globalmente (con el bit EA en el SFR IE), se ignora la petición de interrupción y la ejecución se continúa en forma secuencial. * Cada interrupción se puede programar para tener ya sea prioridad alta (1) ó baja (0, por omisión). Si la nueva interrupción no es de más alta prioridad, que cualquiera que se esté ejecutando, se ignora hasta que se complete la interrupción actual. * Si la nueva interrupción pasa todas las pruebas de arriba, el hardware coloca la dirección de regreso en la pila (Stack), carga el PC con el vector de interrupción correspondiente e inicia la ejecución de su ISR. Registros de Prioridad de Interrupciones Existe un registro de hardware para cada prioridad (alta ó baja), cuya salida única se pone a uno cuando una interrupción de esa prioridad se está ejecutando. Esto previene que otra interrupción de la misma prioridad, ó menor, interrumpa a la ISR que se encuentre ejecutando actualmente. Una interrupción de alta prioridad se puede ejecutar dentro de una ISR de baja prioridad. La instrucción RETI realiza un RET y también limpia el registro de más alta prioridad que actualmente se encuentre activo. Al colocar RETI al final de cada ISR normalmente es suficiente para hacer que trabaje el sistema de prioridad tal y como se especificó. Registro de Prioridades de las Interrupciones (IP: Interrups Priority Register) Bits de Control de Interrupciones El SFR de Control de Habilitación de Interrupciones (IE, 0A8H) contiene el bit de Habilitación Global (EA), que se debe activar para que se permita cualquier interrupción. También se tienen los bits de habilitación individual para cada una de las cinco interrupciones en el 8051 (seis en el 8052 y siete en el 80C51FA). Para que cualquier interrupción pueda ser permitida, su bit individual de habilitación y el de EA deben estar activos. El registro IE se puede accesar por byte ó por bit. Registro habilitador de las Interrupciones (IE: Interrupts Enable Register) El SFR de Control de Prioridad de Interrupciones (IP, 0B8H) contiene el bit de selección de prioridad para cada interrupción individual. Un cero selecciona prioridad baja y un uno prioridad alta. Se puede accesar por byte ó por bit. Si dos ó más interrupciones de la misma prioridad hacen petición al mismo tiempo, y estan habilitadas; una secuencia de muestreo interna predefinida determina a cual se le da el servicio primero. Dicha secuencia de prioridad es la siguiente, de la más alta a más baja: Carlos E. Canto Quintal M.C. - 117 - Laboratorio de Microprocesadores El MICROCONTROLADOR 8051 Externa 0, Temporizador 0, Externa 1, Temporizador 1, (PCA), Serie, T2 OPCIONES PARA LA INTERRUPCIÓN EXTERNA Las dos interrupciones externas se pueden programar en forma separada para que sean sensibles al nivel ó al cambio. Cada tipo tiene sus beneficios; cual es el mejor depende de las necesidades de la aplicación. Sensado por nivel: Una interrupción externa que se programa con este tipo, envía una petición al circuito principal de interrupciones cuando (y mientras) en su terminal se lea un 0 lógico. La ISR se debe de asegurar que el dispositivo que realiza la petición ponga en 1 la terminal (ó debe deshabilitar la interrupción) para que evite el que se reentre a la ISR justo después de la instrucción RETI. El sensado por nivel facilita el manejo de fuentes múltiples con una sola terminal de interrupción, colocando en las terminales de otro puerto cada fuente diferente. La ISR consultará dichas terminales del puerto para identificar la fuente de interrupción. Con este método la petición de interrupción puede pasar desapercibida (olvidada) por el 8051 si la fuente se desactiva cuando no se encuentra disponible. Esto algunas veces es bueno. Sensado por Cambio: Una interrupción externa programada con este tipo se consulta una vez por cada ciclo de máquina. Si con muestras sucesivas se nota que ha ocurrido una transición de bajada (cambio de uno a cero), se activa una bandera (IE0 ó IE1). Esta bandera señala al circuito principal de interrupciones hasta que el hardware llama a la ISR requerida y al mismo tiempo limpia la bandera. Este modo "recuerda" una petición de interrupción, si es que la señal externa regresa a uno antes de que se le de servicio a la interrupción. También, si la señal permanece en cero (activa) después de que la ISR ha terminado, no ocasionará otra interrupción no deseada. Bits de Banderas y Control. La parte baja del SFR Control del Temporizador (TCON, 88H) se dedica para las interrupciones externas. Los bits IT0 e IT1 controlan el tipo de activación para la INT0 e INT1 respectivamente. Un cero (por omisión) selecciona sensado por nivel, un uno sensado por cambio. Los bits IE0, IE1 son las banderas para INT0 e INT1. Mientras IEn este activada, el circuito principal de interrupciones estará recibiendo una petición de salto a la ISR de la INTn. Carlos E. Canto Quintal M.C. - 118 - Laboratorio de Microprocesadores El MICROCONTROLADOR 8051 Almacenado temporal y restablecimiento de datos. Cuando un programa llama a una subrutina, típicamente tiene datos en algunos registros y/o en los SFR que necesita utilizar después de que la subrutina haga su trabajo. Si la subrutina también va a utilizar algunos de ellos, ya sea el programa que llama o la subrutina debe almacenar y restablecer los valores originales. Para ello se puede utilizar el stack mediante las instrucciones PUSH y POP descritas en seguida: PUSH dirección directa • SP=SP+1 • el byte contenido en la dirección directa se escribe en el stack. POP dirección directa • el contenido de la parte alta del stack se escribe a la dirección directa • SP=SP-1 • Conmutación de bancos. Los programas pueden utilizar el direccionamiento por registro de una manera eficiente conmutando entre cuatro bancos separados de registros para uso del programa principal y hasta tres subrutinas. • Colocar las variables utilizadas con mayor frecuencia en los registros para ahorrarse un byte siempre que el programa las accesa • Los cuatro bancos de ocho bytes le permiten a las subrutinas el usar registros para sus variables de uso frecuente. Se almacenan y restablecen los registros del programa que llama, conmutando entre bancos. • El banco de registros que se encuentra activo se selecciona mediante dos bits (RS0, RS1) del registro PSW. El banco seleccionado por omisión es el banco 0. CY CY AC AC F0 F0 RS1 RS1 RS0 RS0 OV OV PP PSW.0 Paridad del acumulador activada por Hardware a 1 si contiene un número impar de 1´s, sino se pone a 0 PSW.7 Bandera de acarreo recibe el acarreo producido por los bits 7 en las operaciones de la ALU PSW.6 Bandera de acarreo auxiliar recibe el acarreo producido por los bits 3 en la adición de operandos PSW.1 Bandera Definida por el Usuario PSW.5 Bandera de Status de propósito General PSW.2 Bandera de Sobreflujo, se activa con operaciones aritméticas PSW.4 Bit1 selector de Banco de Registro PSW.3 Bit 0 selector de Banco de Registro Banco 0 1 2 3 RS1 0 0 1 1 RS0 0 1 0 1 Localidades 0-7 8-FH 10-17H 18-1FH MATERIAL Y EQUIPO UTILIZADO: CI Atmel 89C52 CI Max232 (o Dallas DS275) Carlos E. Canto Quintal M.C. - 119 - Laboratorio de Microprocesadores El MICROCONTROLADOR 8051 Regulador 7805 Cristal piezo-eléctrico de 11.0592 Mhz 1 Condensador de 470 µF 6 condensadores de 1µF Resistencia de 8.2 KΩ Conector DB-9 Plug del eliminador de baterias usado Tarjeta de PCB 1 74LS244 8 LED´s 8 resistencias de 330 Ω 4 conectores de 8 bits Push-button NA Cautín Soldadura Osciloscopio o analizador lógico CORRELACIÓN CON TEMAS DEL PROGRAMA VIGENTE: Con esta práctica se cubre algunos de los aspectos de la unidad III: Microcntroladores METODOLOGÍA (DESARROLLO DE LA PRÁCTICA): I.-Para conocer a fondo la arquitectura, la programación y la aplicación los microcontroladores de la familia 8051, el alumno diseñará e implementará en circuito impreso (PCB) un sistema basado en el microcontrolador de Atmel 89C52. Para el diseño de la tarjeta impresa, se recomienda una distribución como la mostrada en la figura. Incluya un regulador 7805 para que pueda ser alimentado con un eliminador de baterías de 9 ó 12 v. También incluya un MAX232 para poder conectar su tarjeta a otro equipo con el estándar RS232 como por ejemplo una PC MAX232 Dc in Conector DB-9 Plug 7805 Reset P0 P1 89C52 89C52 P3 P2 Cristal de 11.0592 Mhz II.-Ya que la tarjeta esté ensamblada, usando un analizador lógico o un osciloscopio el alumno, observará la señal obtenida en la terminal ALE del del AT89C52. Si la frecuencia de la señal obtenida es del orden de 2 MHZ, entonces la tarjeta funciona correctamente. III.-Se le conecta al puerto P1 un buffer octal 3-state 74LS244 para poder manejar un LED con cada bit del puerto. IV.-Se implementará un programa y se cargará en la memoria Flash del microcontrolador (usando un Programador ) que debe realizar los siguiente: Carlos E. Canto Quintal M.C. - 120 - Laboratorio de Microprocesadores El MICROCONTROLADOR 8051 Al momento de resetear la tarjeta, se prende el LED en el bit menos significativo, un tiempo después se apaga y prende el siguiente y así sucesivamente, produciendo así corrimiento de encendido y apagado de LED´s Una vez que el funcionamiento del sistema sea satisfactorio, el alumno contará con una tarjeta para realizar las dos prácticas siguientes, eliminando así los riesgos inherentes al implementar el sistema en protoboard. SUGERENCIA DIDÁCTICA: I.- investigue acerca de los miembros de la familia de microcontroladores 8051 tanto de Intel como de otros fabricantes. II.- Implemente y cargue otros programas de prueba al sistema implementado III.- Estudie la posibilidad de implementar su propio programador del Microcontrolador ATMEL 89C52 y toda la parentela. IV.-Investigue y compare las ventajas de los Microcontroladores Programables en Sistema (ISP: In System Programming) como el AT89S52 y otros. REPORTE: I.- incluya en su reporte el layout de su tarjeta II.-incluya un resumen sobre su investigación realizada III.-sus comentarios y conclusiones BIBLIOGRAFÍA: • • • • http://www.8052.com Manual del Atmel 89C52 Manual del Max2322 8 bit Embedded microcontrollers Intel • TTL Data Book TI Carlos E. Canto Quintal M.C. - 121 -