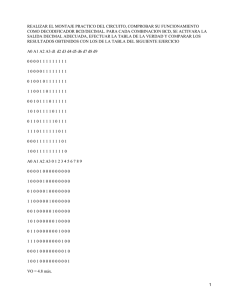

TD TP 07 - Área Electrónica ET17

Anuncio

Escuela de Educación Técnica N° 17 D.E. 13 Región V Departamento de Electrónica T.P. Nº: 7 – Circuitos M.S.I. y L.S.I. 1.- Implemente las siguientes funciones con un solo decodificador 74LS138 y lógica adicional (compuertas adicionales) F1 = f (C , B, A) = ∑ (0,1,2,6) + ∑ (3,4) 3 φ F2 = f (C , B, A, ) = ∏ (0,3,4,6) ⋅ ∏ (1,7) 3 φ 2.- Usando como bloque constructivo al 74LS42 y mínima lógica adicional implementar: a) Un decodificador de 4 a 16 b) Un decodificador de 5 a 32 3.- Usando como bloque constructivo al 74LS138 y mínima lógica adicional, implementar un decodificador de 5 a 32. 4.- Usando como bloque constructivo al 74LS151, y lógica extra, implementar un Mux de 16 vías. 5.- Usando como bloque constructivo al 74LS251 y lógica adicional, implementar un Mux de 16 vías que pueda conectarse a una línea BUS de tres estados. Diseñar la lógica de control de modo que el Mux resultante pueda volcar al bus el dato seleccionado o poner su salida en alta impedancia. 6.- Se dispone de 6 dispositivos (por ejemplo memorias RAM) y un bus de 6 líneas para su selección. Se desea habilitar a cada dispositivo cuando la información en el bus corresponda a una de las siguientes cifras hexadecimales: 10, 12, 13, 15, 16, 17. Utilizar un 74LS138 y suponer que los dispositivos se habilitan cuando se aplica un nivel bajo a la entrada correspondiente. 7.- Por medio de comparadores 74LS85, detectar que los caracteres ASCII presentes sobre un bus de 7 líneas corresponden a las letras minúsculas. 8.- Se dispone de un display de 7 segmentos para 4 dígitos decimales, dos para la parte entera y dos para la fraccionaria. Usando como bloque constructivo al CI 74LS47, implementar la etapa excitadora del display, de modo que borre los ceros no significativos a la izquierda y a la derecha del punto decimal. 9.- Usando como bloque constructivo al CI 74LS85: a) Implementar un comparador de magnitudes de 12 bits b) Implementar un comparador de 8 bits para enteros representados en el convenio de complemento a dos. 10.- Utilizando comparadores 74LS85 detectar que los caracteres ASCII sobre un bus de 8 líneas corresponden a las letras mayúsculas. 11.- Implementar usando la cantidad necesaria de decodificadores CMOS 14028B y el menor numero de compuertas. a) Un convertidor de código BCD Aiken a BCDN b) Un convertidor de código BCDN a BCD Gray 12.- Realizar un detector de validez para el código BCD Aiken en base a: a) 74LS153 b) 74LS151 13.- Implementar un comparador de dos números binarios de 2 bits cada uno, con salidas: A > B, A < B y A = B. Utilizar como bloques constructivos : a) 74LS139 b) 74LS153 __________________________________________________________________________________________ Técnicas Digitales Prof. Ing. ANDRADA, J. Abel