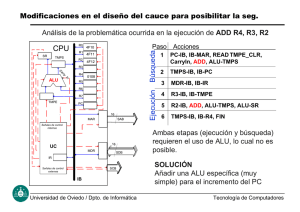

5. El Procesador - U

Anuncio

Arquitectura de Computadores El Procesador © Victor Grimblatt H. 1 Introducción En el capítulo anterior vimos que el rendimiento de una máquina está determinado por tres factores Cantidad de instrucciones Tiempo de ciclo reloj Ciclos de reloj por instrucción (CPI) El compilador y el ISA (instruction set architecture) determinan la cantidad de instrucciones El tiempo de ciclo reloj y el CPI dependen de la implementación del procesador © Victor Grimblatt H. 2 Implementación Básica del MIPS Trabajaremos sobre una implementación básica del MIPS que considera las siguientes instrucciones Instrucciones de memoria: lw y sw Instrucciones aritméticas y lógicas: add, sub, and, or y slt Instrucciones de control de flujo: beq y jump No se incluye el resto de las instrucciones para mantener la simplicidad del diseño La implementación de las otras instrucciones es similar Los conceptos que veremos son los utilizados para construir todo tipo de procesadores © Victor Grimblatt H. 3 Visión Global de la Implementación Para cada instrucción se realiza los siguiente primeros pasos Enviar el contador programa (PC) a la memoria que contiene el código y buscar (fetch) la instrucción de la memoria Leer uno o dos registros (solo uno en lw) seleccionados a partir de los campos de la instrucción Los pasos siguientes dependen de la clase de instrucción © Victor Grimblatt H. 4 Visión Global de la Implementación Hay similitudes entre las clases consideradas, como por ejemplo casi todas ellas (excepto el jump) utilizan una ALU Una vez utilizada la ALU, las acciones requeridas para terminar las instrucciones difieren Algunas de ellas escriben en memoria mientras que otras lo hacen en registros © Victor Grimblatt H. 5 Visión General del MIPS Dos tipos de unidades funcionales © Victor Grimblatt H. Elementos que operan sobre los datos (combinatorio) Elementos que contienen el estado (secuenciales) 6 Observaciones La figura recién presentada es una visión general Posee unidades que tienen dos fuentes de datos lo que no es correcto Es necesario el uso de multiplexores para seleccionar los datos El circuito presenta solo las unidades de operación, obviando la unidad de control, la que controla el flujo de acuerdo a la ínstrucción © Victor Grimblatt H. 7 © Victor Grimblatt H. 8 Unidad de Control Las instrucciones son la entrada de esta unidad Es utilizada para determinar las lineas de control de las unidades funcionales y de los multiplexores © Victor Grimblatt H. 9 Construyendo una ALU Básica Dispositivo que permite realizar operaciones aritméticas tales como la adición y substracción Dispositivo que permite realizar operaciones lógicas tales como AND u OR El MIPS tienen 32 bits por lo que se requiere de una ALU de 32 bits © Victor Grimblatt H. 10 ALU 1 Bit Las operaciones lógicas son fáciles ya que se implementan directamente con compuertas lógicas Este circuito permite realizar las operaciones de AND o OR la que es seleccionada en el multiplexor Re sult Operationab Operationa b © Victor Grimblatt H. 11 Inputs ALU 1 Bit Carry in a sum b Carry out Outputs Comentarios a b C in C out sum 0 0 0 0 0 0 + 0 + 0 = 00 0 0 1 0 1 0 + 0 + 1 = 01 0 1 0 0 1 0 + 1 + 0 = 01 0 1 1 1 0 0 + 1 + 1 = 10 1 0 0 0 1 1 + 0 + 0 = 01 1 0 1 1 0 1 + 0 + 1 = 10 1 1 0 1 0 1 + 1 + 0 = 10 1 1 1 1 1 1 + 1 + 1 = 11 Cout bCin aCin ab sum abCin abCin abCin abCin © Victor Grimblatt H. 12 ALU 1 Bit © Victor Grimblatt H. 13 ALU 32 Bits © Victor Grimblatt H. 14 Substracción Substraer es sumar la versión negativa del operando Para obtener el complemento a 2 de un número se invierte el número bit a bit y se suma 1 Para lograr la inversión se agrega un multiplexor que elige b o !b © Victor Grimblatt H. 15 Substracción 1 Bit ¿Cómo sumamos 1 a !b Poniendo el carry in en 1 © Victor Grimblatt H. 16 Substracción 32 Bits Se conectan 32 ALUs como ya hicimos Seteando el carry del lsb a 1 se obtiene Sum = a + b + 1 Si utilizamos !b tenemos sum = a + !b + 1 = a + (!b +1) = a + (-b) = a - b © Victor Grimblatt H. 17 Más Funcionalidad La ALU del MIPS require igualmente de un NOR Se tiene que !(a + b) = !a * !b © Victor Grimblatt H. 18 Agregando la Instrucción slt Produce un 1 si rs < rt, y 0 en los otros casos slt seteara todos los bits a cero salvo el último que depende de la comparación La salida para slt es llamada less y se agrega una entrada al multiplexor de salida less vale cero para los 31 bits superiores de la ALU ¿Cómo hacemos la comparación entonces? © Victor Grimblatt H. 19 Agregando la Instrucción slt a < b implica que a – b < 0 El lsb de la operación slt debe ser un 1 si a < b, lo que es lo mismo que decir que a – b es negativo Por lo que ponemos un 1 si a – b es negativo y un cero si es positivo Bastaría conectar el bit de signo de la salida del sumador al lsb para obtener less © Victor Grimblatt H. 20 Agregando la Instrucción slt Desgraciadamente el Result del bit más significativo de la ALU para esta operación no es la salida del sumador Necesitamos una ALU diferente para el bit msb con una salida extra que corresponde a la salida del sumador Como necesitamos un diseño especial para el último bit agregamos las detección de overflow © Victor Grimblatt H. 21 ALU para los otros bits ALU para el bit más significativo © Victor Grimblatt H. 22 ALU 32 Bits © Victor Grimblatt H. 23 Instrucciones de Bifurcación Condicional Estas instrucciones bifurcan si dos registros son iguales o desiguales a = b es lo mismo que a – b = 0 Bastaría con hardware para comprobar que un resultado es igual a cero para verificar la igualdad Con un OR entre las salidas se puede comprobar la igualdad a cero © Victor Grimblatt H. 24 © Victor Grimblatt H. 25 ALU Final Líneas de control Función 0000 AND 0001 OR 0010 add 0110 substract 0111 set on less than 1100 NOR © Victor Grimblatt H. 26 ALU en Verilog – Descripción Comportamental module MIPSALU (ALUCtl, A, B, ALUOut, Zero); input [3:0] ALUCtl; input [31:0] A,B; output reg [31:0] AlUOut; output Zero; assign Zero = (AlUOut == 0); //Zero es verdadero si ALUOut es igual a cero always@(ALUCtl, A, B) begin //evalua los cambios case (ALUCtl) 0: ALUOut <= A & B; 1: ALUOut <= A | B; 2: ALUOut <= A + B; 6: ALUOut <= A - B; 7: ALUOut <= A < B ? 1:0; 12: ALUOut <= ~(A + B); //NOR default: ALUOut <= 0; endcase end endmodule © Victor Grimblatt H. 27 ALU en Verilog – Unidad de Control module ALUControl (ALUOp, FuncCode, ALUCtl); input [3:0] ALUOp; input [5:0] FuncCode; output reg [3:0] AlUCtl; always case FuncCode 32: ALUOp <= 2; //add 34: ALUOp <= 6; //substract 36: ALUOp <= 0; //and 37: ALUOp <= 1; //or 39: ALUOp <= 12; //nor 42: ALUOp <= 7; //slt default: ALUOp <= 15; //should not happen endcase endmodule © Victor Grimblatt H. 28 Convenciones de Diseño Lógico Las unidades funcionales en el MIPS consisten en dos tipos de elementos lógicos que operan sobre datos – combinatorios Elementos que contienen el estado – secuenciales o elementos de estado Elementos Las memorias de datos e instrucciones así como los registros son elementos de estado Un elemento de estado tiene al menos dos entradas y una salida © Victor Grimblatt H. 29 Convenciones de Diseño Lógico Las entradas de un elemento de son el dato y el reloj La salida de un elemento de estado provee el valor que fue escrito en el ciclo anterior Un elemento de estado básico es el FF D El MIPS utiliza otros elementos de estado tales como memorias y registros Se utiliza el término asserted para indicar que una señal está en nivel alto y assert para indicar que debe ser llevado a nivel alto De forma complementaria se usa deasserted y deassert © Victor Grimblatt H. 30 Metodología de Temporización Una metodología de temporización (clocking methodology) define cuando las señales pueden ser leídas y escritas Esto es importante ya que si una señal es leída al mismo tiempo que es escrita, podríamos leer el valor anterior A modo de simplificar utilizaremos una metodología de temporización por canto (edge-triggered clocking methodology) Esta metodología indica que los valores son guardados en un canto del reloj © Victor Grimblatt H. 31 Metodologías de Temporización Solo los elementos de estado pueden guardar valores Las entradas a los bloques combinatorios provienen de elementos de estado y sus salidas van a elementos de estado Las entradas son valores escritos en el ciclo anterior y las salidas pueden ser usadas en el próximo ciclo © Victor Grimblatt H. 32 Metodologías de Temporización Las señales se propagan del elemento de estado 1, a través de la lógica combinatoria, al elemento de estado 2 en un ciclo de reloj El tiempo necesario para llegar al elemento de estado 2 define el largo del ciclo reloj Esta metodología permite la retroalimentación, se lee el valor de un registro, se pasa a través de lógica combinatoria y se escribe el mismo registro en el mismo ciclo reloj © Victor Grimblatt H. 33 Metodologías de Temporización Asumiremos que todas los relojes llegan al mimo tiempo a modo de simplificación De esta forma garantizamos que el sistema funciona correctamente sin carreras (races) siempre y cuando el largo del reloj sea suficiente Ocurre una carrera cuando el contenido de un elemento de estado depende de la velocidad relativa de los elementos lógicos En un diseño por canto, el reloj debe ser lo suficientemente largo para acomodar el camino entre 1 FF, a través de la lógica combinatoria, y otro FF cumpliendo los requisitos de set up © Victor Grimblatt H. 34 Metodologías de Temporización El ciclo reloj tiene que ser al menos de tprop + tcombinational + tsetup en los valores worst case tprop: tiempo de propagación de una señal a través de un FF, llamado igualmente clock-to-Q tcombinational: mayor retardo a través de la lógica combinatoria tsetup: tiempo antes del canto del FF en que la señal debe estar válida © Victor Grimblatt H. 35 Metodología de Temporización Hemos asumido que el thold (tiempo que debe permanecer válida la señal para ser considerada) se cumple siempre lo que es cierto en la mayoría de los casos en circuitos modernos Otro concepto a considerar es el clock skew (diferencia en tiempo absoluto entre el momento en que dos elementos de estado ven el canto del reloj) Esto ocurre ya que la señal de reloj usa en general dos caminos diferentes, con retardos diferentes, para alcanzar dos elementos de estado © Victor Grimblatt H. 36 Metodologías de Temporización Debido a la diferencia en tiempo en que los dos FF ven el canto del reloj, la señal del primer FF puede atravesar la lógica combinatoria antes de que el segundo FF vea el reloj Por esta razón el período del reloj debe ser al menos tprop + tcombinational + tsetup + tskew © Victor Grimblatt H. 37 Tarea Investigue la metodología de temporización por nivel (level-sensitive timing) © Victor Grimblatt H. 38 Construyendo un Datapath (Camino de los Datos) Una forma razonable de diseñar un datapath es examinando los principales componentes requeridos para ejecutar cada clase de instrucciones Miremos que elementos de datapath son requeridos por cada instrucción En primer lugar requerimos de una memoria para almacenar las instrucciones del programa y para entregar estas instrucciones a partir de una dirección Requerimos igualmente de un registro llamado Contador de programa (PC) que es usado para mantener la dirección de la instrucción en curso Necesitamos también un sumador para incrementar el PC a la dirección de la próxima instrucción © Victor Grimblatt H. 39 Construyendo un Datapath El sumador puede ser construido a partir de la ALU que ya diseñamos cableandola de forma adecuada A esta ALU especial la llamaremos Add para indicar que solo realiza funciones de suma © Victor Grimblatt H. 40 Construyendo un Datapath Para ejecutar cualquier instrucción debemos en primer lugar buscar la instrucción de la memoria Se debe igualmente incrementar el PC de 4 para posicionarse en la próxima instrucción © Victor Grimblatt H. 41 Construyendo un Datapath Consideremos una instrucción de formato R Estas instrucciones leen dos registros, realizan una operación en la ALU y escriben el resultado Estas instrucciones son llamadas de tipo R o de tipo aritmético lógico Estas instrucciones incluyen add, sub, and, or y slt Los 32 registros de propósito general del procesador se encuentran en una estructura llamada register file © Victor Grimblatt H. 42 Construyendo un Datapath Un register file es una colección de registros Cada registro puede ser escrito o leído especificando el número del registro El register file el registro de estado de la máquina Como el formato R tiene tres operandos registros debemos leer dos datos del register file y escribir un dato en el register file © Victor Grimblatt H. 43 Construyendo un Datapath Consideremos las instrucciones lw y sw El formato general es lw $t1,offset_value($t2) o sw $t1,offset_value($t2) Se requiere calcular una dirección memoria sumando el registro base ($t2) al valor contenido en el offset (16 bits con signo) Si la instrucción es un store, el valor a guardar debe ser leído de un registro Si la instrucción es un load, el valor leído debe ser guardado en un registro Se requiere tanto la ALU como el register file © Victor Grimblatt H. 44 Construyendo un Datapath Requerimos además una unidad que permita extender el signo en 16 bits © Victor Grimblatt H. 45 Construyendo un Datapath La instrucción beq tiene tres operandos Dos registros que se comparan buscando la igualdad y un offset de 16 bits usado para calcular la dirección de bifurcación Su forma es beq $t1,$t2,offset Para implementar la instrucción se debe calcular la dirección de bifurcación sumando el offset extendido en signo al PC © Victor Grimblatt H. 46 Construyendo un Datapath Hay dos detalles que deben tenerse en cuenta en la instrucción beq ISA especifica que la base de cálculo para la dirección de bifurcación es la instrucción que sigue a la bifurcación. Este valor ya se tienen ya que se calcula PC + 4 al obtener la instrucción ISA establece que el offset es desplazado a la izquierda de 2 bits Además de calcular la dirección de bifurcación, se debe determinar si la próxima instrucción es la que sigue secuencialmente o es la de bifurcación © Victor Grimblatt H. 47 Construyendo un Datapath Cuando la condición es verdadera, el PC toma la dirección de bifurcación y se dice que se toma la bifurcación Si los operandos no son iguales, el PC incrementado reemplaza al PC y se dice que no se toma la bifuracción El datapath debe realizar dos operaciones para las bifurcaciones, calcular la dirección de bifurcación y comparar los registros El datapath incluye un módulo de extensión de signoy un sumador para calcular la dirección Para la comparación se requiere del register file y la ALU © Victor Grimblatt H. 48 Construyendo un Datapath Como la ALU provee una salida que indica si el resultado es cero, basta enviar los dos registros a la ALU y hacer una substracción Si la salida zero es asserted, los dos registros son iguales © Victor Grimblatt H. 49 Construyendo un Datapath Hemos examinado los componentes necesarios para cada una de las instrucciones consideradas por separado El datapath debe tratar de ejecutar las instrucciones en un ciclo reloj Esto implica que los recursos no pueden ser usados más de una vez por instrucción, por lo que cada elemento que se requiere más de una vez debe ser duplicado Requerimos de una memoria de instrucciones separada de la de datos Para permitir compartir los componentes del datapath es necesario poner multiplexores en las entradas © Victor Grimblatt H. 50 Ejemplo Los operaciones tipo R (aritméticas y lógicas) y las de memoria son similares Las principales diferencias son Las instrucciones aritméticas y lógicas usan la ALU con dos registros como entrada. Las instrucciones de memoria pueden usar la ALU para calcular la dirección con el offset extendido en signo como segunda entrada El valor guardado en el registro de destino viene de la ALU (instrucción tipo R) o de la memoria (load) Construya un datapath usando un register file y una ALU para este tipo de instrucciones Agregue los multiplexores necesarios © Victor Grimblatt H. 51 Ejemplo Un solo register file y una sola ALU implica dos fuentes diferentes para la segunda entrada de la ALU Implica igualmente dos fuentes para el dato guardado en el register file Por lo requerimos de un multiplexor en la entrada de la ALU y otro en la entrada del register file © Victor Grimblatt H. 52 Ejemplo Datapath para las instrucciones tipo R y memoria © Victor Grimblatt H. 53 Ejemplo El datapath completo contiene lo siguiente Fetch de instrucciones Instrucciones tipo R y memoria Bifurcaciones © Victor Grimblatt H. 54 Ejemplo © Victor Grimblatt H. 55 Ejemplo A esto se le debe agregar la unidad de control Esta unidad debe ser capaz de recibir entradas y generar una señal de escritura para cada elemento de estado, la selección de cada multiplexor y el control de la ALU © Victor Grimblatt H. 56 Control de la ALU La ALU tiene 4 entradas de control Los bits de control no están codificados Solo usaremos 6 de las 16 combinaciones posibles Líneas control ALU Función 0000 AND 0001 OR 0010 add 0110 sub 0111 slt 1100 NOR © Victor Grimblatt H. 57 Control de la ALU La función NOR es necesaria para otras funciones del MIPS La ALU es usada para calcular la dirección para las instrucciones lw y sw Para las instrucciones de tipo R, la ALU realiza una de las cinco acciones (AND, OR, sub, add, slt) dependiendo del valor del campo function (6 bits) Para beq, la ALU realiza una substracción © Victor Grimblatt H. 58 Control de la ALU Podemos generar una unidad de control de 4 bits de la ALU teniendo en entrada el campo function y dos bits llamados ALUOp ALUOp indica si la operación es una suma (00) para lw y sw, substracción (01) para beq o lo indicado en function (01) © Victor Grimblatt H. 59 Control de la ALU Opcode ALUOp Instrucción Campo Function Acción Control ALU LW 00 Load word XXXXXX suma 0010 SW 00 Store word XXXXXX suma 0010 Branch-equal 01 Branch equal XXXXXX substracción 0110 R-type 10 Add 100000 suma 0010 R-type 10 Substract 100010 substracción 0110 R-type 10 AND 100100 and 0000 R-type 10 OR 100101 or 0001 R-type 10 Set on less than 101010 set less on than 0111 © Victor Grimblatt H. 60 Control de la ALU Hay diferentes formas de implementar este control Es conveniente crear una tabla de verdad que considere las combinaciones de entrada relevantes Esta tabla de verdad muestra los 4 bits de control de la ALU en función de los 8 bits de entrada (6 de function y 2 de ALUOp) 8 entradas producen 256 combinaciones posibles, como solo nos interesamos en algunas de estas combinaciones y sus salidas, siendo las otras don’t care, no se muestran en la tabla Representamos con una x las entradas don’t care A partir de la tabla se construye el circuito correspondiente pasando por una etapa de optimización en primer lugar © Victor Grimblatt H. 61 Control de la ALU ALUOp Campo Función Operación ALUOp1 ALUOp0 F5 F4 F3 F2 F1 F0 0 0 x x x x x x 0010 x 1 x x x x x x 0110 1 x x x 0 0 0 0 0010 1 x x x 0 0 1 0 0110 1 x x x 0 1 0 0 0000 1 x x x 0 1 0 1 0001 1 x x x 1 0 1 0 0111 © Victor Grimblatt H. 62 Control de la ALU © Victor Grimblatt H. 63