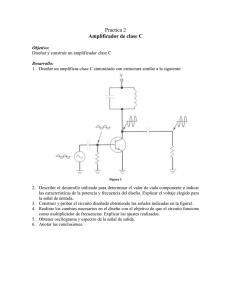

to get the file

Anuncio