TEMA 4 DA2

Anuncio

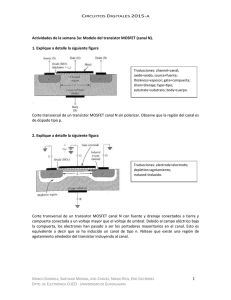

Diseño Análogo 2 – Tema # 4 MOSFET (Metal-Oxide Semiconductor Field-Efect Transistor). Este transistor es muy utilizado en el diseño de circuitos Integrados CI, debido a que son más pequeños que los BJT y su proceso de manufactura es relativamente simple, además su consumo de potencia es menor. En la actualidad se pueden diseñar los CI utilizando solo mosfet o con muy pocos elementos pasivos (RLC), lo que ayuda significativamente a reducir el número de elementos externos y por ende minimizar el área del PCB (Printed circuit board). Estructura de Dispositivo En la figura 4.1 se puede observar como es la estructura física de un NMOS (mosfet de canal N), el cual consiste de un sustrato tipo p que es el soporte de las demás regiones, a este sustrato también se le conoce como cuerpo (Body = B), aquí se generan dos regiones o pozos de tipo n, los cuales son altamente dopados con impurezas pentavalentes. A estos posos se da el nombre de Drenaje (Drain = D) y Fuente (Source = S). En la superficie del sustrato crece una delgada capa de dióxido de silicio (𝑆𝑖𝑂2 ) que tiene un espesor 𝑡𝑜𝑥 (por lo general de 2 a 50nm) y es un muy buen aislante eléctrico, este aislante es el responsable de que en la compuerta (Gate = G) las corrientes sean extremadamente pequeñas, del orden de 10−15 𝐴. Todas estas terminales anteriormente mencionadas (B, D, S y G) están conectadas por medio de una placa metálica para poder realizar la conexión a los circuitos externos. Algunas distancias a tener en cuenta son la distancia entre los posos 𝑛+ 𝐿 = 0.1 𝑎 3𝜇𝑚 y 𝑊 = 0.2 𝑎 100𝜇𝑚 estas distancias están cambiando periódicamente debido a los avances tecnológicos, al ser el mosfet un dispositivo simétrico se pueden intercambiar los terminales Fuente y Drenaje sin modificar sus características. Operación sin voltaje de compuerta Sin voltaje en la compuerta, entre el drenaje y la fuente existe una configuración de dos diodos conectados como se muestra en la figura 4.2 donde no es posible la conducción, en realidad la resistencia entre D-S esta en el orden de 1012 Ω Figura 4.2 Creación de un canal para el flujo de corriente Para hacer esto se introduce un voltaje positivo 𝑣𝐺𝑆 , éste hará que los huecos libres del sustrato sean repelidos hacia abajo, dejando una zona de carencia de portadores o región de agotamiento, puesto que los huecos neutralizadores han sido empujados hacia abajo. Además el voltaje positivo de la compuerta atrae los electrones de las regiones 𝑛+ de la fuente y el drenaje donde abundan, cuando se acumulan una cantidad suficiente de electrones cerca de la superficie del sustrato debajo de la compuerta se Figura 4.1 1 crea realmente un canal que permite el flujo de electrones si se coloca un voltaje entre drenaje y fuente. Como el canal que se genera es de tipo N a este transistor se le denomina MOSFET de canal N o NMOS. Entonces cuando 𝑣𝐺𝑆 = 𝑉𝑡 el canal esta inducido pero la corriente es mínima (insignificante), a medida que 𝑣𝐺𝑆 > 𝑉𝑡 el canal se va haciendo más grande y permite que la conductividad del canal aumente, como se puede ver en la figura 4.5, se puede observar que la respuesta es muy lineal siempre que 𝑣𝐷𝑆 sea pequeño, a la diferencia 𝑣𝐺𝑆 − 𝑉𝑡 se le conoce como voltaje de sobrecarga o 𝑉𝑂𝑉 Figura 4.3 Al valor de 𝑣𝐺𝑆 que se requiere para que los electrones libres formen un canal, se le denomina voltaje umbral 𝑉𝑡 este voltaje obviamente es positivo y suele estar en el orden de 0.5 y 1V Figura 4.5 Aplicación de un 𝒗𝑫𝑺 pequeño Operación a medida que aumenta 𝒗𝑫𝑺 Ahora inducido un canal se aplica un pequeño voltaje positivo 𝑣𝐷𝑆 entre el drenaje y la fuente, como se muestra en la figura 4.4 se genera una corriente 𝑖𝐷 que dependerá de la densidad de electrones del canal que como ya hemos visto dependerá del voltaje 𝑣𝐺𝑆 Para este análisis dejaremos un voltaje 𝑣𝐺𝑆 constante superior a 𝑉𝑡 y se comenzará a aumentar 𝑣𝐷𝑆 Figura 4.6 Figura 4.3 A medida que 𝑣𝐷𝑆 aumenta, éste potencial robará electrones que están en el canal cerca a la terminal de drenaje y éste comenzará a tener una forma 2 triangular, una representación gráfica de cómo se va modificando el canal se muestra en la figura 4.7 Realicemos un análisis del comportamiento físico de los electrones en el canal, cuando se encuentra operando en la región de tríodo, para tal caso 𝑣𝐺𝑆 > 𝑉𝑡 , para generar el canal 𝑣𝐷𝑆 ≤ 𝑣𝐺𝑆 − 𝑉𝑡 para que el canal no se estrangule y si observamos el gráfico se forma un capacitor de placas planas paralelas en donde la capacitancia es 𝐶𝑜𝑥 = Figura 4.7 Si 𝑣𝐷𝑆 ≥ 𝑣𝐺𝑆 − 𝑉𝑡 el canal se estrangula es decir la profundidad del canal se reduce a cero y se dice que el mosfet se satura es decir la cantidad de corriente no aumentará aunque se aumente 𝑣𝐷𝑆 , en la figura 4.8 se muestra como es la corriente en el canal con relación a la variación del 𝑣𝐷𝑆 manteniendo un 𝑣𝐺𝑆 > 𝑉𝑡 . 𝜀𝑜𝑥 𝑡𝑜𝑥 Donde 𝜀𝑜𝑥 = 3.45𝑥10−11 𝐹/𝑚 y 𝑡𝑜𝑥 depende de la tecnología como ya se había mencionado Para encontrar la carga infinitesimal de la capacitancia de la compuerta, se multiplica la capacitancia por el voltaje efectivo entre la compuerta y el canal en el punto 𝑥 ′ Voltaje efectivo es [𝑣𝐺𝑆 − 𝑣(𝑥) − 𝑉𝑡 ] Donde 𝑣(𝑥) es el voltaje del canal en ese punto 𝑑𝑞 = −𝐶𝑜𝑥 (𝑊𝑑𝑥)[𝑣𝐺𝑆 − 𝑣(𝑥) − 𝑉𝑡 ] El menos es debido a la carga negativa del electrón 𝑣𝐷𝑆 genera un campo eléctrico a la carga en dirección negativa de x 𝐸(𝑥) = − Figura 4.8 Obtención de la relación 𝑖𝐷 − 𝑣𝐷𝑆 𝑑𝑣(𝑥) 𝑑𝑥 Este campo hace que la carga del electrón se desplace a una velocidad 𝑑𝑥 𝑑𝑡 = −𝜇𝑛 𝐸(𝑥) = 𝜇𝑛 𝑑𝑣(𝑥) 𝑑𝑥 Donde 𝜇𝑛 es la movilidad superficial de los electrones, este parámetro depende de la tecnología de fabricación. La corriente resultante es 𝑖= 𝑑𝑞 𝑑𝑡 𝑑𝑞 𝑑𝑥 = 𝑑𝑥 𝑑𝑡 = −𝜇𝑛 𝐶𝑜𝑥 𝑊[𝑣𝐺𝑆 − 𝑣(𝑥) − 𝑉𝑡 ] 𝑖𝐷 = −𝑖 = 𝜇𝑛 𝐶𝑜𝑥 𝑊[𝑣𝐺𝑆 − 𝑣(𝑥) − 𝑉𝑡 ] 𝑑𝑣(𝑥) 𝑑𝑥 𝑑𝑉(𝑥) 𝑑𝑥 𝑖𝐷 𝑑𝑥 = 𝜇𝑛 𝐶𝑜𝑥 𝑊[𝑣𝐺𝑆 − 𝑣(𝑥) − 𝑉𝑡 ]𝑑𝑣(𝑥) Figura 4.9 3 Integrando varios miembros de la ecuación de 𝑥 = 0 hasta L y de manera correspondiente de 𝑣(0) = 0𝑉 hasta 𝑣(𝐿) = 𝑣𝐷𝑆 tenemos 𝐿 𝐾 𝑛′ = 𝜇𝑛 𝐶𝑜𝑥 = 450 [ 𝑐𝑚2 𝑉 𝑓𝐹 ] 4.32 [𝜇𝑚2 ] 𝐾 𝑛′ = 450𝑥108 [𝜇𝑚2 /𝑉]4.3210−15 [𝐹/𝜇𝑚2 ] = 194𝜇𝐴/𝑉 2 𝑣 𝐷𝑆 ∫0 𝑖𝐷 𝑑𝑥 = ∫0 𝜇𝑛 𝐶𝑜𝑥 𝑊[𝑣𝐺𝑆 − 𝑣(𝑥) − 𝑉𝑡 ]𝑑𝑣(𝑥) 2 𝑣𝐷𝑆 𝑣(𝑥) 𝑣𝐷𝑆 𝑖𝐷 𝐿 = 𝜇𝑛 𝐶𝑜𝑥 𝑊 [(𝑣𝐺𝑆 − 𝑉𝑡 )𝑣(𝑥) | − | ] 0 2 0 𝑖𝐷 = 𝜇𝑛 𝐶𝑜𝑥 𝑊 𝐿 ((𝑣𝐺𝑆 − 𝑉𝑡 )𝑣𝐷𝑆 − 𝑣𝐷𝑆 2 2 ) Región de tríodo Para encontrar la corriente en la región de saturación es cambiar 𝑣𝐷𝑆 = 𝑣𝐺𝑆 − 𝑉𝑡 puesto que este punto es compartido por la región de tríodo y saturación (punto rojo en la figura 4.8). 𝑖𝐷 = 𝜇𝑛 𝐶𝑜𝑥 𝑊 𝐿 1 𝑖𝐷 = 2 𝜇𝑛 𝐶𝑜𝑥 ((𝑣𝐺𝑆 − 𝑉𝑡 )(𝑣𝐺𝑆 − 𝑉𝑡 ) − 𝑊 𝐿 (𝑣𝐺𝑆 −𝑉𝑡 )2 2 ) 𝑖𝐷 = 𝐾𝑛′ 𝑊 2 𝐿 (𝑣𝐺𝑆 − 𝑉𝑡 )2 𝑖𝐷 = 𝐿 𝐾𝑛′ 𝑊 2 𝐿 ((𝑣𝐺𝑆 − 𝑉𝑡 )𝑣𝐷𝑆 − 𝑣𝐷𝑆 2 2 8 Para el mosfet en la región de tríodo 𝑖𝐷 = 𝐾 𝑛′ 𝑊 𝐿 𝑖𝐷 = 𝐾 𝑛′ 𝑊 pequeño 𝑊 1 100𝜇𝐴 = 2 194𝜇𝐴/𝑉 2 0.8 (𝑣𝐺𝑆 − 0.7)2 𝑉𝐺𝑆 − 0.7 = 0.32𝑉 𝑉𝐺𝑆 = 1.02𝑉 Para estar en saturación la condición es 𝑣𝐷𝑆 ≥ 𝑣𝐺𝑆 − 𝑉𝑡 Por lo tanto 𝑣𝐷𝑆𝑚𝑖𝑛 = 𝑣𝐺𝑆 − 𝑉𝑡 = 0.32𝑉 ((𝑣𝐺𝑆 − 𝑉𝑡 )𝑣𝐷𝑆 − ) Tríodo 𝑟𝐷𝑆 = 𝐿 (𝑣𝐺𝑆 − 𝑉𝑡 )𝑣𝐷𝑆 𝑣𝐷𝑆 𝑖𝐷 = Considere una tecnología de proceso para la que 𝐿𝑚𝑖𝑛 = 0.4𝜇𝑚, 𝑡𝑜𝑥 = 8𝑛𝑚, 𝜇𝑛 = 450𝑐𝑚2 /𝑉 ∗ 𝑠 y 𝑉𝑡 = 0.7𝑉. a) Encuentre 𝐶𝑜𝑥 y 𝐾 𝑛′ . b) Para un MOSFET con 𝑊 ⁄𝐿 = 8𝜇𝑚/0.8𝜇𝑚, calcule los valores de 𝑣𝐺𝑆 y 𝑣𝐷𝑆𝑚𝑖𝑛 necesarios para operar el transistor en la región de saturación con una corriente 𝐼𝐷 = 100𝜇𝐴. c) Para el dispositivo en b), encuentre el valor de 𝑉𝐺𝑆 requerido para hacer que opere como un resistor de 1000Ω para un 𝑣𝐷𝑆 muy pequeño. 𝐶𝑜𝑥 = 𝑡𝑜𝑥 = 8𝑥10−9 2 𝐶𝑜𝑥 = 4.32𝑓𝐹/𝜇𝑚 −3 = 4.32𝑥10 𝐹/𝑚 ) Solo cuando 𝑣𝐷𝑆 es 1 𝑊 𝐾𝑛′ (𝑣𝐺𝑆 −𝑉𝑡 ) 𝐿 Ejemplo 4.1 pag245 3.45𝑥10−11 𝐹/𝑚 2 Donde se puede notar que existe una relación lineal entre el voltaje de drenaje y la corriente que circula por este, a la cual llamaremos 𝑟𝐷𝑆 (𝑣𝐺𝑆 − 𝑉𝑡 )2 Saturación 𝜀𝑜𝑥 𝑣𝐷𝑆 2 Cuando el 𝑣𝐷𝑆 es pequeño el 𝑣𝐷𝑆 2 será mas pequeño y se podrá despreciar teniendo así Donde sí definimos a 𝐾 𝑛′ = 𝜇𝑛 𝐶𝑜𝑥 queda: 𝑖𝐷 = 𝐾 𝑛′ (𝑉𝐺𝑆 − 𝑉𝑡 )2 2 1000 = 1 8 194𝜇𝐴/𝑉 2 (𝑣𝐺𝑆 −0.7) 0.8 𝑣𝐺𝑆 = 1.22𝑉 El mosfet de canal P Opera de la misma manera que uno de canal n con la excepción de que 𝑣𝐺𝑆 y 𝑣𝐷𝑆 son negativos al igual que el voltaje umbral 𝑉𝑡 además la corriente 𝑖𝐷 entra por la terminal de la fuente y sale por el drenaje. Tecnología CMOS Como su nombre lo indica, la tecnología de los MOS complementarios emplea transistores MOS de ambas polaridades, Aunque los 4 circuitos CMOS son un poco más difíciles de fabricar que los NMOS, la disponibilidad de dispositivos complementarios permite muchas opciones para el diseño de circuitos tanto digitales como analógicos, la tecnología CMOS casi ha remplazado a los diseños basados únicamente en transistores NMOS. Más aun esta tecnología está remplazando los circuitos que hace pocos años solo se podían hacer con dispositivos bipolares. En la figura 4.10 se muestra un corte transversal de un chip CMOS que ilustra cómo se fabrican los transistores PMOS y NMOS. Figura 4.12 Características 𝒊𝑫 − 𝒗𝑫𝑺 En la figura 4.13 se muestra un Mosfet de canal n con voltajes aplicados 𝑣𝐺𝑆 y 𝑣𝐷𝑆 aplicados y con las direcciones normales del flujo de corriente Figura 4.13 Figura 4.10 Símbolos del mosfet Si comenzamos a variar ambos voltajes tendremos una familia de curvas de acuerdo a lo analizado que tendrán la forma mostrada en la figura 4.14 En la figura 4.11 se muestran los símbolos de un transistor NMOS en donde el ultimo se supone que el body esta a tierra y por lo tanto no se dibuja, en la figura 4.12 se ilustran son los transistores PMOS y sus diferentes representaciones simbólicas. Es de anotar que la flecha indica la dirección normal de la corriente y la compuerta está aislada con el transistor por medio de un aislante esto se representa por medio de dos líneas verticales que no se tocan similar al símbolo de un capacitor Figura 4.14 Figura 4.11 Como se ve en la figura existen tres regiones de operación: Corte, Triodo y Saturación la última se utiliza para operar como amplificador y los otras dos para interruptor. 5 Corte delimita la frontera entre tríodo y saturación se puede obtener al sustituir 𝑣𝐺𝑆 < 𝑉𝑡 No hay canal por lo tanto 𝑖𝐷 = 0𝐴 𝑣𝐷𝑆 = 𝑣𝐺𝑆 − 𝑉𝑡 Triodo 𝑊 𝑖𝐷 = 𝐾 𝑛′ 𝐿 (𝑣𝐺𝑆 − 𝑉𝑡 )𝑣𝐷𝑆 = 𝐾 𝑛′ ecuación de una parábola 𝑣𝐺𝑆 ≥ 𝑉𝑡 Canal inducido 𝑊 𝐿 𝑣𝐷𝑆 2 Que es la 𝑣𝐷𝑆 ≤ 𝑣𝐺𝑆 − 𝑉𝑡 Canal continúo 𝑣𝐷 − 𝑣𝑆 ≤ 𝑣𝐺 − 𝑣𝑆 − 𝑉𝑡 Reordenando 𝑣𝐺𝐷 ≥ 𝑉𝑡 𝑖𝐷 = 𝐾 𝑛′ 𝑊 𝐿 ((𝑣𝐺𝑆 − 𝑉𝑡 )𝑣𝐷𝑆 − 𝑣𝐷𝑆 2 2 ) 𝐾 𝑛′ = 𝜇𝑛 𝐶𝑜𝑥 Parámetro de transconductancia del proceso si 𝑣𝐷𝑆 es pequeño podemos omitir 𝑖𝐷 = 𝐾 𝑛′ 𝑊 𝐿 𝑣𝐷𝑆 2 2 (𝑣𝐺𝑆 − 𝑉𝑡 )𝑣𝐷𝑆 Esta relación lineal representa una resistencia lineal con valor controlado por 𝑣𝐺𝑆 𝑟𝐷𝑆 = 𝑟𝐷𝑆 = 𝑣𝐷𝑆 | 𝑖𝐷 𝑣 𝐷𝑆 pequeño = Figura 4.15 El circuito a gran señal para la región de saturación es el mostrado en la figura 4.15Y en la figura 4.16 los niveles relativos de los voltajes en las terminales del transistor NMOS 1 𝑊 𝐿 𝐾 𝑛′ (𝑣𝐺𝑆 −𝑉𝑡 ) 1 𝑊 𝐾𝑛′ 𝑉𝑂𝑉 𝐿 Saturación 𝑣𝐺𝑆 ≥ 𝑉𝑡 Canal inducido 𝑣𝐷𝑆 ≥ 𝑣𝐺𝑆 − 𝑉𝑡 Canal estrangulado 𝑣𝐷 − 𝑣𝑆 ≥ 𝑣𝐺 − 𝑣𝑆 − 𝑉𝑡 Reordenando 𝑣𝐺𝐷 ≤ 𝑉𝑡 Figura 4.16 La frontera entre saturación y tríodo esta dado por Resistencia de salida finita 𝑣𝐷𝑆 = 𝑣𝐺𝑆 − 𝑉𝑡 Si remplazamos este valor en la ecuación de la corriente del Mosfet encontraremos la corriente de saturación Cuando el voltaje 𝑣𝐷𝑆 ≥ 𝑣𝐺𝑆 − 𝑉𝑡 el canal no solo se estrangula sino que va disminuyendo su tamaño a medida que 𝑣𝐷𝑆 aumenta como se ilustra en la figura 4.17 𝑖𝐷 = 𝐾𝑛′ 𝑊 2 𝐿 (𝑣𝐺𝑆 − 𝑉𝑡 )2 Esto es una fuente de corriente controlada por el voltaje 𝑣𝐺𝑆 que como se ha estudiado es la base de los amplificadores. Con estas ecuaciones podemos dibujar el gráfico de la figura 4.14 y la curva que 6 Figura 4.17 Donde se denomina a 𝑣𝐷𝑆𝑠𝑎𝑡 = 𝑣𝐺𝑆 − 𝑉𝑡 en este caso la corriente 𝑖𝐷 = Figura 4.18 𝐾𝑛′ 𝑊 (𝑣𝐺𝑆 − 𝑉𝑡 2 𝐿−∆𝐿 )2 Que se puede rescribir como 𝑖𝐷 = 𝐾𝑛′ 𝑊 1 2 𝐿 1−∆𝐿 Donde (𝑣𝐺𝑆 − 𝑉𝑡 )2 𝑟𝑜 = [ 𝐿 En donde el término 1 1− ∆𝐿 𝐿 se puede expandir en 𝜕𝑖𝐷 −1 𝜕𝑣𝐷𝑆 𝑟𝑜 = [𝜆 𝐾𝑛′ 𝑊 series de Mc Laurin 1 1− ∆𝐿 𝐿 = (1 − ∆𝐿 −1 𝐿 0 −2 1 ) = 1 − (− 𝐿) (1 − 𝐿) 1 ∆𝐿 + ⋯ 𝐿 ) 1 2 𝑓′′(∆𝐿) = 𝐿2 (1 − ∆𝐿 −1 ) ∆𝐿 −2 ) 𝐿 1 = 𝐿 (1 − 𝐿 ∆𝐿 −3 𝐿 ) 1 2 𝐿 2!𝐿2 = 1 + ∆𝐿 + ∆𝐿2 … … 𝐾𝑛′ 𝑊 2 𝐿 (1 + Figura 4.19 ∆𝐿 𝐿 ) (𝑉𝐺𝑆 − 𝑉𝑡 )2 Mosfet de canal tipo p En la figura 5,1 se muestra la dirección de las corrientes en un mosfet de canal tipo p =𝜆 𝑖𝐷 = 𝐼𝐷 ) ∆𝐿 = 𝜆′𝑣𝐷𝑆 𝐿 𝑉𝐴 ∆𝐿 −2 Como ∆𝐿 ≪ 𝐿 𝜆′ 𝐷 −1 es decir 𝑖𝐷 = 2𝑛 𝐿 (𝑣𝐺𝑆 − 𝑉𝑡 )2 de donde el nuevo modelo queda representado por ∆𝐿 −1 𝑓 ′ (∆𝐿) = − (− 𝐿) (1 − 𝑖𝐷 = 𝑟𝑜 = 𝜆𝐼 = (𝑣𝐺𝑆 − 𝑉𝑡 )2 ] 𝐾′ 𝑊 𝑓(∆𝐿) = (1 − 𝐿 2 𝐿 𝑣𝐺𝑆 𝑐𝑜𝑛𝑠𝑡𝑎𝑛𝑡𝑒 𝐼𝐷 es sin tomar en cuenta la modulación del canal Donde (1 − ] 𝐾𝑛′ 𝑊 2 𝐿 (𝑣𝐺𝑆 − 𝑉𝑡 )2 (1 + 𝜆𝑣𝐷𝑆 ) Con lo cual se generan la familia de curvas mostrada en la figura 4.18 7 𝑖𝐷 = 𝐾𝑝′ 𝑊 2 𝐿 𝑟𝑜 = [|𝜆| 𝐾𝑝′ 𝑊 𝑟𝑜 = [|𝜆| 1 (𝑣𝐺𝑆 − 𝑉𝑡 )2 o 𝑖𝐷 = 2 𝐿 Figura 4.20 𝐷 2 𝐿 (𝑣𝑆𝐺 − |𝑉𝑡 |)2 −1 )2 (𝑣𝐺𝑆 − 𝑉𝑡 ] 𝐾𝑝′ 𝑊 2 𝐿 𝑟𝑜 = 𝜆𝐼 = 𝐾𝑝′ 𝑊 −1 (𝑣𝑆𝐺 − |𝑉𝑡 |)2 ] |𝑉𝐴 | 𝐼𝐷 Corte 𝑣𝐺𝑆 ≥ 𝑉𝑡 𝑣𝑆𝐺 < |𝑉𝑡 | No hay canal por lo tanto 𝑖𝐷 = 0𝐴 Triodo 𝑣𝐺𝑆 ≤ 𝑉𝑡 o 𝑣𝑆𝐺 ≥ |𝑉𝑡 | Canal inducido 𝑣𝐷𝑆 ≥ 𝑣𝐺𝑆 − 𝑉𝑡 Canal continúo Figura 5.2 𝑣𝐷 − 𝑣𝑆 ≥ 𝑣𝐺 − 𝑣𝑆 − 𝑉𝑡 Reordenando El papel del sustrato o cuerpo 𝑣𝐺𝐷 ≤ 𝑉𝑡 o 𝑣𝐷𝐺 ≥ |𝑉𝑡 | 𝑖𝐷 = 𝐾 𝑝′ 𝑊 𝐿 ((𝑣𝐺𝑆 − 𝑉𝑡 )𝑣𝐷𝑆 − 𝑣𝐷𝑆 2 2 ) 𝐾 𝑝′ = 𝜇𝑝 𝐶𝑜𝑥 Parámetro de transconductancia del proceso si 𝑣𝐷𝑆 es pequeño podemos omitir 𝑖𝐷 = 𝐾 𝑝′ 𝑊 𝐿 𝑣𝐷𝑆 2 Si el sustrato está conectado a la fuente, este no desempeña una labor destacable, mas sin embargo si se aplica un voltaje negativo para los NMOS o positivo para los PMOS este actuara como otra compuerta. 2 (𝑣𝐺𝑆 − 𝑉𝑡 )𝑣𝐷𝑆 Esta relación lineal representa una resistencia lineal con valor controlado por 𝑣𝐺𝑆 𝑟𝐷𝑆 = 𝑟𝐷𝑆 = 𝑣𝐷𝑆 | 𝑖𝐷 𝑣 𝐷𝑆 pequeño = 1 𝑊 𝐾 𝑝′ (𝑣𝐺𝑆 −𝑉𝑡 ) 𝐿 1 𝑊 𝐾𝑛′ 𝑉𝑂𝑉 𝐿 Saturación 𝑣𝐺𝑆 ≤ 𝑉𝑡 o 𝑣𝑆𝐺 ≥ |𝑉𝑡 | Canal inducido 𝑣𝐷𝑆 ≤ 𝑣𝐺𝑆 − 𝑉𝑡 Canal estrangulado 𝑣𝐷 − 𝑣𝑆 ≤ 𝑣𝐺 − 𝑣𝑆 − 𝑉𝑡 Reordenando 𝑣𝐺𝐷 ≥ 𝑉𝑡 o 𝑣𝐷𝐺 ≤ |𝑉𝑡 | 8