Estructura y Organización de Computadores

Anuncio

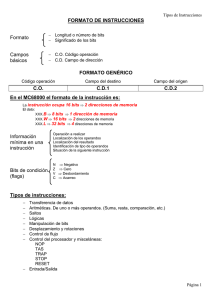

Estructura y Organización de Computadores Año 2013 Sinak #UAHStyle 1. La ruta de datos 1.1. Introducción 1.1.1 La unidad aritmético-lógica La Unidad Central de Proceso o CPU es el conjunto de: - Ruta de datos o unidad de procesamiento - Unidad de control La ruta de datos procesa la información [Ver relación entre la ruta de datos y la unidad de control] [Ver flujo de instrucciones y flujo de datos] CPU Es la encargada de procesar la información. Los componentes de la ruta de datos son: - La ALU - Los elementos de almacenamiento temporal - El registro de estado (Dice como ha sido el resultado, en algunas no existe) Procesa: - Operandos En función de las señales de control ALU Conjunto de operadores, unidades funcionales, unidades de ejecución. #UAHStyle La ALU está formada por un conjunto de: - Operadores - Unidades funcionales - Unidades de ejecución Operador: Circuito capaz de realizar una operación lógica o aritmética Los operadores se caracterizan por: - Numero de operandos: o Monádico o Diádico - Procesamiento: o Serie (bit a bit) o Paralelo (por palabras) - El resultado depende de: o Los operandos (combinacional) o Operandos y el contador de estados (secuencial) - Tecnología (marca la velocidad) -> Retardo Tipo de operandos Según la tecnología empleada (marca el retardo de las puertas) pueden ser - MOS - BIPOLAR NAND, NOR, NOT AND, OR XOR XNOR retardo a 2a 3a El valor de a varía según algunas tecnologías. 1.1.2 Almacenamiento temporal Tanto los operandos como los resultados pueden tener un almacenamiento temporal en la ruta de datos. Acelera el acceso evitando las latencias de memoria (de datos). Puede estar constituido por: - 1 único registro (Acumulador) - Banco de Registros - Sin registros: pila y memoria 1.1.2.1 Acumulador El propio registro acumulador es uno de los operandos de entrada. Corresponde a la arquitectura de las primeras maquinas Almacenamiento temporal breve Reutilización de datos #UAHStyle 1.1.2.2 Banco de Registros Puede ser: - Por su función: o Propósito general o Especifico - Para el programador: o Visibles o Arquitectónicos (el programador no puede acceder a ellos). 1.1.2.3 Sin Registros (almacenamiento en memoria) No hay almacenamiento temporal: todas las variables están en memoria Pila: - El acceso no es aleatorio sino de tipo LIFO Los operandos están en la cima y son sustituidos por el resultado Modo de trabajar de las calculadoras Una ventaja: no se deben especificar operandos (ya que siempre se opera con el de encima de la pila) 1.1.3 El estado Señalan condiciones relativas a la última operación El estado está disponible para la unidad de control y sirve para tomar decisiones. Tomar decisiones: esta es la diferencia entre un computador y una calculadora El estado puede ser más complicado, contiene el contexto de procesamiento. 1.2. Ruta de datos y velocidad de reloj 1.2.1 ¿Quién limita al reloj? Simplificadamente: Flujo de instrucciones: velocidad de decodificación en la unidad de control Flujo de datos (latencia de los operadores y la impedancia de los cambios eléctricos) Velocidad de reloj en la ruta de datos: Retardo de los caminos (multiplexores, buses…) Retardo del operador más usado (objetivo: que realice la operación en un ciclo) 1.2.2 Modos de llevar a cabo una operación - Unidad combinacional: Tiene un tiempo de transferencia de señales. Es casi inmediato. Permite ejecutar varias cosas en paralelo. Es el más rápido y costoso. #UAHStyle - Unidad secuencial: Ejecuta las operaciones en sucesivos pasos de comunicación. Requiere más tiempo. - Microprograma: Mas barato que los anteriores, es más lento, no requiere hardware adicional. Programa (Emulación): Ejecuta el código que reside en memoria principal. Es el más lento - 1.2.3 Operadores típicos Los más rápidos son los operadores lógicos (NOT, OR AND XOR): Se denominan operaciones de bit. Cada bit es tratado de manera individual, menor número de niveles lógicos. Operadores de desplazamiento: Consiste en desplazar los bits de una palabra derecha o a la izquierda. Los Computadores más sencillos solo realizan desplazamientos unitarios, mientras que los complejos hacen muchos. Circuitos desplazadores: - Desplazador combinacional para 1 bit: cualquier longitud de desplazamiento, gran número de puertas lógicas. - Desplazador combinacional basado en multiplexores: Gran área de silicio. Más barato y más lento. - Barrer Shifter: desplaza o rota cualquier nº de bits en una única operación. Gran numero de celdas aunque son pequeñas Operaciones sobre signo: - Etapa de cambio de signo en complemento a 1: #UAHStyle - Cambio de signo en complemento a 2: Se puede conectar en cascada pero cuidado con la propagación de acarreos) - Si = ai XOR (E * Ci) Ci = ai + Ci-1 - - Extensión de signo en diferentes representaciones. Hay tres casos: o Complemento: Se repetirá el bit más significativo del origen para cubrir todas las posiciones adicionales del destino. o Signo magnitud: Hay que desplazar el bit de signo a la izquierda del destino y hay que llenar con ceros el resto de bits adicionales. o En exceso: Hay que añadir ceros a la izquierda. Operaciones aritméticas: Enteros, coma flotante, suma-resta, multiplicación, división y raíz cuadrada #UAHStyle 1.3. El sumador 1.3.1 Sumador elemental El sumador elemental es un circuito combinacional capaz de sumar dos bits más el posible acarreo de la etapa anterior, produciendo el bit suma y el acarreo a la etapa siguiente. - Sumador de 2 niveles lógicos - 3 niveles pero menos puertas (dos semisumadores) - 3 niveles (5 puertas) 3 niveles= 5 puertas. Retardo= 6a (para suma) Retardo= 3a+2a=5a (para acarreo) Se pueden construir varios tipos de sumadores como por ejemplo: - Operador secuencial: Un paso de computación por bit. [pg. 178 Anasagasti] - Sumador paralelo: n bits simultáneamente. 1.3.2 Propagador Propagador de acarreo (RCA) Gran retardo en la propagación del acarreo. (Dibujo de evolución temporal) Evaluación del tiempo de retardo para 32 bits: - Tiempo = 3a + 2(n-1)a + 3a = 68ª - Sea a = 1ns tiempo = 68ns 14 MHz (1/0,00000068) - Niveles = 3 + 2(n-1) = 65 - Sea a = 1ns tiempo = 65ns 15 MHz (1/0,00000065) #UAHStyle Retardo: se suele dar en niveles, se simplifica (niveles = 2n) Área: se suele dar en celdas. Cada celda es un sumador elemental. 1.3.3 Sumador-restador en diferentes representaciones ·Restador paralelo: Modificación del operador de suma A – B-> cambio de signo de B y suma Cambio de signo se puede hacer en cualquier sistema de representación. · Sumador-Restador en binario puro: La representación afecta al desbordamiento: En suma -> el acarreo En resta -> A-B = A + (2n – B) = 2n + A – B A < B negativo no representable; se “come” el acarreo 2n · Sumador-Restador en complemento a 2: La representación afecta al desbordamiento [Ver imagen] ·Sumador-restador en signo-magnitud: S-R sin signo más circuito para tratar signo · Sumador-Restador en exceso: ·Sumador BCD de 1 digito: Sumador hexadecimal + circuito corrector Restar 10 = sumar 6 (complemento a 16) Colocando en cascada podemos operar con n dígitos BCD ·Resta en BCD: Para restar complementar a 9 (más o menos C-1) A – B= A + (10n – B – 1) = 10n -1+ (a-B) = 10n + (A – B) – 1 - Si A – B < 0 -> correcto - Si A – B > 0 -> Hay que recircular #UAHStyle · S-R BCD en aritmética de signo · S-R en coma flotante Se hace con enteros. Los n bits de los operandos se dividen en p bits para la mantisa M y en q bits para el exponente E. Siendo r la base del exponente (normalmente 2), el valor es: Valor= M * rE Las mantisas suelen estar normalizadas. Sean A (MA, EA) y B (MB, EB) normalizados por r=2, p=q=4, mantisa en signo magnitud y exponente en exceso 2q-1=8 A: 0100 1010 0,5 * 22 2 B: 0100 1011 0,5 * 23 4 La suma será: A+B = 0.5*22 + 0.5*23 = 0.5*22 + 0.5*(22*21) = 0.5*22 + 1*22 = 1.5*22 = 6 Pero este resultado no se puede normalizar porque la mantisa es 1,… para normalizar tendrá que ser 0,… Si el exponente crece, la mantisa se divide: A+B=0.5*22 + 0.5*23 = 0.25*23 + 0.5*23 = 0.75*23 = 6 Que en representación de coma flotante será: R 0110 1011 0,75*23 6 Pasos que hay que seguir: - Separar mantisas y exponentes: o Separar mantisas y exponentes y extensión de signo a n bits (bits de guarda) para información que se pierde al hacer las divisiones (desplazamientos) - Restar los exponentes: o Resta de los exponentes para obtener: Exponente mayor que será el del resultado salvo normalización Mantisa que hay que desplazar, que será la de menor exponente. Número total de desplazamientos que se necesita hacer - Alineación de mantisas - Se opera (Suma o resta) con las mantisas: o Realización de la operación de suma o resta y redondeo (quitar bits de guarda) si es necesario. - Normalización del resultado: o Normalización del resultado si es necesario (si el MSB del exponente es 0). 1.3.4 Dígitos de guarda Ya que las operaciones en coma flotante generan más bits de los que caben en la representación se mejora la precisión añadiendo una serie de bits que llamamos dígitos de guarda. #UAHStyle En la resta hace falta un bit retenedor ya que al desplazar a la derecha una mantisa para alinearla podemos perder acarreos de la parte sobrante El bit retenedor será 1 cuando se detecte un 1 en la parte sobrante de la derecha Al desplazar a la derecha el segundo operando perdemos el acarreo de los 4 bits que salen de la representación. El bit retenedor se encargara de marcar este hecho para reflejarlo en el resultado. En general la representación de mantisas dentro de la ALU tiene m+3 bits repartidos de esta forma: 1.3.5 Técnicas de redondeo - La truncación consisten en eliminar los bits de la derecha; siempre da lugar a un - error por defecto El redondeo propiamente dicho consiste en tomar el valor más próximo del resultado obtenido El método por el cual se fuerza el bit menos significativo de la representación (LSB) a 1 es una transacción. Ejemplo: 0,11001 10111 111 0,10001 00010 111 Truncación 0,11001 10111 0,10001 00010 Redondeo 0,11001 11000 0,10001 00011 LSB a 1 0,11001 10111 0,10001 00011 1.4. Acelerador de la suma entera 1.4.1 Introducción ·Propagación de acarreo o RCA Sencillo, ocupa poco pero es lento Un sumador es un circuito combinacional que se puede reducir a una formula lógica en forma de sumas y productos en dos niveles: - Muchas puertas gran área de silicio - Problemas de fan-in, etc. - Imposibilidad de implementación 1.4.2 Anticipador de acarreo (CLA) Funciones lógica: Construimos dos funciones a partir de esta observación (función generación y función propagación) #UAHStyle Planteamiento (II) De la misma manera que existe generación y propagación de acarreo para 1 bit podemos tener generación y propagación para un bloque de m bits. 1.4.3 Anticipador de acarreo por bloques Los operandos entran por la parte superior, viajan hacia abajo para combinarse con el acarreo de entrada c-1 y vuelven a subir para generar los bits de sumas correctos. Ventajas Es más fácil de implementar que el CLA Inconvenientes Ocupa un tamaño proporcional de n·log2n celdas. 1.4.4 Hibrido anticipador-propagador Los operandos entran por la parte superior, viajan hacia abajo para combinarse… [Dibujado en el Hennesy-Patterson] 1.4.5 Salto de acarreo Planteamiento (I): Un sumador con salto de acarreo está a mitad de camino entre no de propagación de acarreo y uno de anticipación en velocidad y coste 1.4.6 Selector de Acarreo Planteamiento: - En el sumador con selección de acarreo se realizan dos sumas en paralelo, una con acarreo de entrada igual a 0 y otra con acarreo de entrada igual 1. Una vez que se conoce el acarreo verdadero se selecciona la suma correcta. - Se conoce como sumador condicional Desventajas: Aumenta el coste de implementación y consumo. La señal selectora de los multiplexores debe atacar a muchos de ellos (fan-out grande. Los multiplexores suelen ser lentos. Mejoras: - Dado que el tiempo de la operación lo marca los bloques … El retardo total será el del primer bloque mas el asociado a las puertas lógicas que hacen pasar el acarreo verdadero a los bloques sucesivos. Dado que esas puertas lógicas introducen un retardo, tenemos tiempo para que los bloques propagadores vayan siendo algo más grandes según bis aproximamos a los bits de mayor peso. Retardo. El retardo viene dado por: - Retardo del primer propagador: 2k niveles. - Red de puertas 2(n/k - 2) niveles - Ultimo multiplexor: 3 niveles. #UAHStyle 1.5 Operación de multiplicación 1.5.1 Introducción a la multiplicación Es una operación compleja y eso tiene su coste en tiempo y en área de silicio Los compiladores intentan sustituir la multiplicación por secuencias de operaciones más sencillas Se suele hacer utilizando un sumador-restador de manera secuencial mediante un algoritmo adecuado. Solamente maquinas muy potentes utilizan un multiplicador combinacional. Algunos procesadores utilizan un diseño hibrido entre multiplicación secuencial y la combinacional. 1.5.2 Multiplicación sin signo Algoritmo de sumas desplazamientos Es una multiplicación binaria sin signo Este algoritmo se basa en el método de multiplicar manualmente. El registro A contiene el multiplicando mientras que el registro P contiene inicialmente el multiplicador P0 El multiplicador se pierde siendo sustituido por el resultado sobre el doble de tamaño de representación. Genera 1 bit del resultado por paso de control. Es intrínsecamente lento. Si evitamos la suma con 0 se hace más rápido pero depende del multiplicador (del numero de 0s que tenga) Tiempo de computo variable: No es bueno para los compiladores, dificulta la segmentación. Algoritmo de sumas y restas Se basa en: sea el número B que contiene una cadena de 1s que van de posición 1 a la 6. 00111110 B = 26 – 21 = 01000000 – 00000010 = 00111110 Por lo que A·26 – A·21 Que NO es un producto sino un conjunto de DESPLAZAMIENTOS Generalizando: Restaremos A·2i cuando nos encontremos el primer 1 de una cadena y sumaremos A·2j cuando se acabe, es decir, cuando alcancemos el siguiente 0. #UAHStyle 1.5.3 Multiplicación con signo La multiplicación es muy sencilla en signo-magnitud Normalmente utilizamos el complemento a 2: - En este caso un método sencillo para trabajar con signo puede ser: o …. Algoritmo de Booth para “sumas desplazamientos” Se trabaja con un algoritmo para datos sin signo. Sin embargo, hay un problema. Ejemplo: - Si multiplicamos 1011 (11) por 1101 (13), obtenemos 10001111 (143) → BIEN. Si el número negativo está en el multiplicador solamente, también sale bien. Pero si interpretamos los dos números como complemento a 2, tendríamos 1011 (-3) por 1101 (-5), obteniendo= 10001111 Por tanto, si tenemos un multiplicador negativo, se obtiene: R* = A * - B= A * (2n - |B|) -> MAL Ya que lo que queremos es: Por tanto, habrá que utilizar una corrección: Es decir: ¡RESUMEN DE LO QUE HAY QUE HACER, SOLO PARA SUMAS DESPLAZAMIENTOS!: Siempre que el bit n-1 de B sea 1, al resultado de la multiplicación normal, se le hace –A*2n-1, es decir, se le resta A desplazado N-1 lugares. #UAHStyle Algoritmo de Booth para “sumas y restas” Vamos a ver este caso con otro ejemplo: Tenemos A = 1101 1101 B = 1000 0011 En una multiplicación SIN signo A = 221 B = 131 A*B = 28951 B = 1000 0011= -20 + 22 - 27 + 28 Sumas parciales sobre 22n A*B = -A * 20 + A*22 – A*28 =28951 FUNCIONA En una multiplicación CON signo A= -35 B= -125 A*B= 4375 B= 1000 0011= -20 + 22 – 27 + 28 Con extensión de signo en todas las sumas parciales 22n A*B = -A*20 + A*22 – A*28 = -4585 MAL Por lo tanto, si aplicamos la corrección de Booth, tenemos que –A*28 = 8960 – 4585 + 8960 = 4375 FUNCIONA En este caso no haría falta, pero si B<0 → B= -20 + 22 - 27, ya que eliminar el peso 28 (que es 2n) es extender el número negativo a 22n, es decir, suponer que contiene 1’s a la izquierda: B= 1111 1111 1000 0011 Multiplicadores combinacionales - Son más rápidos que los métodos basados en algoritmos - Ocupan mas - Segmentables - Por ejemplo: Multiplicador por árbol de Wallace 1.6 Operación de división 1.6.2 División con restauración Circuito divisor con restauración Inicialmente el dividendo esta en R-Q; al final R contiene el resto y Q el cociente Sentido de la puerta OR: Cuando sale un 1 por la izq. se debe contabilizar como cabe aunque la operación de prueba sobre el dividendo parcial genere “no cabe”. #UAHStyle · Se evitan las restauraciones gracias a lo siguiente: Sea DP el dividendo parcial Operación de prueba (DP – B) Restauración si “no cabe” (DP – B + B) · 2 x 2 significa bajar uno mas Nueva operación de prueba (DP – B + B) · 2 - B,…… 1.6.3 División sin restauración No hace falta restaurar, sólo cambiar de operación. - Si no cabe, la siguiente operación de prueba es sumar. - Si sí cabe, la siguiente operación de prueba es restar. Ventaja: El multiplexor, que era lo más costoso, te lo ahorras ya que en el circuito no está. Resultado: Inviertes el bit de mayor peso de cada uno de los resultados parciales. Pasos de computación: n pasos (n bits). 24/10/2011 2 El repertorio de instrucciones 2.1 Principios de diseño 2.1.1 Elementos de una instrucción maquina El repertorio de instrucciones es la interfase entre la capa física y la capa programada Representa el contrato entre el programador y el arquitecto diseñador del procesador Manifiesta la arquitectura software (No tiene que coincidir con la arquitectura física real). El diseño del repertorio de instrucciones responde a las siguientes preguntas Que hacer, con quien registros, codificación · Fases de ejecución de una instrucción #UAHStyle · La elección de las características del repertorio es una de las primeras decisiones a tomar el proceso de diseño de un nuevo procesador. 2.1.2 Tipos de operaciones · ¿Qué hacer? ¿Qué operaciones debe incluir el repertorio para procesar información? Se deben cumplir dos condiciones: - Capaz de realizar una tarea computable dentro de un tiempo finito - Ser eficaz Prescindiendo de la eficacia se ha demostrado que pueden diseñarse repertorio muy reducidos (Maquina de Turing [Escribir, desplazar una posición y leer, parar] y Minsky [Decrementar…]) Una clasificación típica: - Transferencia/movimiento: o Copia información de un elemento de almacenamiento a otro o Trabajan con dispositivos especiales(pila, E/S) o Mueven palabras y fracciones de palabras o Trabajan con 2 operandos - Proceso: o Aritméticas Coma fija Coma flotante o Lógicas o Comparación (resta o AND sin salvar resultado) o Desplazamiento/rotaciones o Trabajan con 3 operandos - Bifurcación/salto/control de flujos: o Modifican la secuencia normal de ejecución de un programa: Reutilizan de código Toma de decisiones Programación modular y estructurada o Dado que dicha secuencia la controla la CP, actúan sobre este operando de manera implícita Se pueden considerar como un caso especial de transferencia donde el operando destino o Clasificación: Saltos: Condicionales: evalúan una condición sobre: el registro de estado, operando explicito incondicionales (se evalúa una condición) Subrutinas: salto incondicional a la dirección de las subrutinas Llamada y retorno de subrutina esta emparejado Puede llamarse desde cualquier posición #UAHStyle - Puede llamar a otro subrutinas Hay que salvar la dirección de retorno para poder retornar a la secuencia principal Es habitual pasar parámetros (En registros, pila…) El conjunto de parámetros mas la dirección de retorno se denomina marco de pila.[Foto de marco de pila en Stallings] Otras (instrucciones de bit…) Comparativa modos de implantar los condicionales [tabla muy bonita y muy grande para copiarla, columnas (tipo, ejemplo, modo de trabajar, pros, contras)] Comentario acerca de las llamadas a procedimientos Transferencia de control de estado: - Antigua moda. Instrucciones de manejo de registro en bloque - Hoy en día cada registro se almacena individualmente Salvaguarda de registro potencialmente sobrescribidles 2.1.3 Las direcciones ¿Con quién? Las operación es se realizan sobre operandos. Los operandos pueden estar en: - Memoria principal - Registro - La propia instrucción El modo de almacenamiento temporal en CPU es un aspecto destacado en el diseño de un procesador [Imagen de modo de almacenamiento temporal en CPU, supuestamente en el Hennesy Patterson] · Pila: Instrucciones de 0 direcciones [En la pg. 398 de Stallings] · Acumulador: Instrucción de 1 dirección ·Banco de registros: Instrucciones de 2 o 3 direcciones Requieren de instrucciones de carga/almacenamiento · Memoria-memoria: Sin almacenamiento temporal Recuento pequeño Formato grande · El almacenamiento temporal en registros es el más utilizado hoy en día #UAHStyle Los procesadores que lo implementa se conocen como maquinas: Registro-registro. Carga/almacenamiento · Los registros son rápidos · Los compiladores lo maneja bien 2.1.4 Factores a considerar en el diseño A saber: Cuantas, que y cuan complejas deben ser Tipo de datos Longitud de la instrucción en bits, número de direcciones, longitud de cada uno de los campos. … Existe una verdadera arquitectura del repertorio de instrucciones (ISA) El ISA tiene un impacto decisivo en dos vertientes - … - … 2.1.5 Endianess Aplaude a la ordenación de los bytes en memoria de un tipo de tamaño multibyte (Figuras sacadas de Wikipedia) BigEndian: Orden de escritura de izq. a der., las cadenas de caracteres se almacenan igual LittleEndian: Orden de los pesos (el menor de dirección más baja) Big-Endian Little-Endian Convenciones de Microsoft. Manejo de procedimientos (Buscar, tiene pinta de importante) 2.2 Modos de direccionamiento 2.2.1 Introducción Posibles ubicaciones: - Propia instrucción - Elementos de almacenamiento (Registros, memoria) #UAHStyle Clasificación: - Inmediato - Directo [Mirar los modos de direccionamiento] IMPORTANTE 2.2.2 Modos de redireccionamiento Directo Absoluto (a registro, a memoria) Directo relativo a registro [implícito, explicito] (La instrucción no contiene la posición del operando sino un desplazamiento respecto a un puntero) Es el más usado, las instrucciones son más compactas, muy útil para manejar estructuras de datos. Indirecto 2.3 Codificación de las instrucciones 2.3.1 Principios Codificación y compatibilidad binaria: Cuando dos maquinas distintas ejecutan el mismo lenguaje maquina se dicen que son compatibles binarias. La codificación tiene importante implicaciones: en cuanto al uso de memoria, en cuanto a….yo que se T.T Las instrucciones de maquinas son AUTOCONTENIDAS e independientes. La secuencia de bits se divide en campos con diferentes tamaños y significados. Esto se conoce como formato Para que sea AUTOCONTENIDA se deben especificar…. 2.3.2 Ortogonalidad Propiedad de un repertorio de instrucciones de un microprocesador. Dicho repertorio será Ortogonal si cada operación se puede realizar con cualquier tipo de operando y cualquier modo de direccionamiento… Solo ha existido una maquina que haya sido ortogonal esa era el VAX. 2.3.3. Criterios de diseño (Según Holmeremu y Bose) Importantes es el TAMAÑO DE CODIGO ESTATICO y REGULARIDAD DE LA DECODIFICACION Longitud de la instrucción (Múltiplo de byte, tamaño de palabra [muy extendido el formato de 32 bits]) 2.3.4 Codificación Veamos los códigos de operación: Con el fin de ahorrar espacio, se usa… Los códigos de mensaje pueden formar parte del OPCODE: Este método… [Mirarte OPCODE, el año pasado preguntó….] #UAHStyle Sean n (tamaño de código de operación), t (numero de códigos que son campos de extensión), m (tamaño del código asicado al campo de extensión de yoquecoñose) Numero de códigos pequeños: p 2n -1 Numero de códigos grandes: g = 2n·t 2.3.5 Formatos Comerciales ·80x86 · VAX · Alpha · PowerPC 2 El repertorio de instrucciones (bis?) 2.4 Planteamiento (Frecuencia de Uso) Importancia de la frecuencia de uso: De los modos de direccionamiento De las operaciones Ayuda a determinar: la anchura de banda requerida en…, …, …. 2.4.2 Modos de direccionamiento Se van a utilizar 3 programas (TeX, Spice y Gcc) TeX: procesador de textos, cadenas de caracteres Spice: simulación Gcc: compilador · Operandos ubicados en memoria (Maquina VAX) [Grafica en el Henessy-Patterson] Comentarios: Es un estudio de Henesy Patterson sobre un VAX (maquina con muchos modos de direccionamiento de memoria) - Relativo a base y a índice y base son casos relativos a… - … · Distribución de inmediatos por dos operandos (maquina MIPS R2000) Comentario: Los inmediatos se suelen usar en comparación La mayor parte de las comparaciones… … · Resumen: En los accesos a memoria el modo más usado es el relativo a registro #UAHStyle 2.4.3 Operaciones Dos tipos de distribuciones: - Uso estático: recuento de operaciones sobre una imagen ejecutable - Uso dinámico: recuento de operaciones en ejecución o No coinciden ya que la traza de ejecución no tiene por que seguir todas las posibles bifurcaciones escritas en el código y repite los bucles gran numero de iteraciones. Menos del 15% de las instrucciones son responsables del 90% de la ejecución. · Comentarios: - Las instrucciones más sencillas (rápidas) son las más usadas: o El arquitecto se ha encargado de conseguir que sean rápidas debido a su frecuencia de uso o 10 instrucciones de x86 son responsables del 96% de la ejecución · Frecuencia de uso de los saltos [en el Hennesy-Patterson] Distancia de salto: - Tamaño del desplazamiento sobre el PC - Con 8 bits es suficiente para la mayor parte de los saltos saltos de longitud de rango +- 128 · Caracterización de los saltos: - Saltos hacia atrás suelen ser bucles o Se toman el 90% de los casos o Conocer esto ayuda a implementar predicciones de salto - Se pueden hacer otras caracterizaciones combinando el destino del salto y el modo de direccionamiento · Resumen: - Muy pocas instrucciones son responsables de la mayor parte de la ejecución de un programa - Las transferencias son la operaciones más abundantes - Los saltos condicionales suponen alrededor del 20% - .. · Llamadas/retornos de procedimientos [en Stallings]: - Se consume mucho tiempo en llamadas/retornos de procedimientos o Aunque el porcentaje de uso entre saltos sea al torno del 15% o No se suelen usar más de 6 argumentos o No se suelen usar más de 6 variables locales o No se hacen secuencias de llamadas muy profundas (alrededor de 5) 2.4.4 Eventos Dinámicos · Distribución del uso dinámico de instrucciones para dos arquitecturas diferentes (memoriamemoria, registro-registro) #UAHStyle Comentarios: - Porcentaje de saltos diferente, aunque es una constante, debido a la diferencia de recuento - En m-m hay menos trasferencia porque las operaciones de procesos llevan… - En r-r … · Distribución de evento dinámicos en maquinas de distintas arquitecturas Comentarios - El flujo de datos en memoria es menor en r-r ya que los datos están en CPU - El recuento es mayor en registro-registro 2.5 CISC vs RISC 2.5.1 Salto semántico Repertorio CISC: - El desarrollo de los lenguajes de programación de alto nivel provoca el denominado salto semántico - Diferencia de complejidad entre las operaciones que pueden representar el lenguaje (sofisticadas) y las que proporciona el computador (primitivas) - El salto semántico se manifiesta en programas muy largos, compiladores muy complejos - Para evitar el salto semántico se diseñan ISAs con: o Muchas operaciones o Muchos modos de direccionamiento o Sentencias HLL implementadas en hardware Secuencias complejas en microcódigo - Los programas de repertorio CISC son mas compactos (imagen ejecutable) o Consumen menos memoria (área de código) - Los estudios acerca de la frecuencia de uso operaciones y modos de direccionamiento DESMIENTEN la eficacia de las características introducidas para evitar el salto semántico [los programas compactos NO son los programas más rápidos] 2.5.2 Conclusiones acerca de la frecuencia de uso Los estudios acerca de la frecuencia de uso de operaciones y modos de direccionamiento desmienten la eficacia de las características introducidas para evitar el salto semántico. 2.5.3 Organización de los registros Ventanas de registro: - Asignación un conjunto pequeño de registros a cada procedimiento (se emplean pocos parámetros y variables….) - Los registro de salida de un conjunto se solapan con los de entrada del procedimiento llamado [figura del Stallings] #UAHStyle - En una llamada a un procedimiento, el procesador conmuta a una nueva ventana de registros, sin necesidad de guardar los registros en la pila Para asegurar cualquier profundidad de llamada, habría que implementar un número ilimitado de registros [Figura redondita tomada del Stallings de algo] - Para las variables globales, se utilizan un banco de registros adicionales que es accesible desde cualquier procedimiento · Banco de Registros: - Es un enfoque … - El esquema fue diseñado por Hennessy - Lo implementan entre otros los procesadores MIPS o Alpha 2.5.4 Filosofía RISC Repertorio limitado y sencillo Operaciones de proceso entre registros (maquinas r-r) Pocos modos de direccionamiento y sencillo: - Se privilegia el acceso a memoria mediante el modo relatico a registro mas desplazamientos - No se direcciona más de un operando de memoria por instrucción - Se deja de usar el indirecta Formato: - Un único tamaño de instrucción, suele ser de 32 bits - Formato regular, campos situados en el mismo lugar siempre Diseño hardware: - Se simplifica la unidad de control control mas rápido - Uso de un gran número de registros de propósito general - Énfasis en la optimización de la segmentación de las instrucciones - Procesamiento de 1 instrucción por ciclo (lectura de operandos ejecución y escritura del resultado en 1 ciclo de reloj) - En cuanto al uso de memoria se intenta evitar: ambigüedades, tal y tal - En cuto a paralelismo… 2.6 Compatibilidad binaria Un procesador es compatible binario con otro si soporta, al menos, el mismo juego de instrucciones que el otro con un formato idéntico o, al menos, coherente. Problemática: - Si los procesadores no son compatibles binarios se debe recompilar todo el software utilizando compiladores nativos - Para un único programa escrito en un lenguaje estándar esto es sencillo #UAHStyle - Una aplicación compleja puede estar constituida por miles de pequeñas piezas de código fuente desarrollada y compilada con herramientas diferentes. Para correr código antiguo en computadores nuevos: - Interprete software - Emulador en microcódigo - Traductor binario - Compilador nativo 3. La unidad de control 3.2 Fases de ejecución de una instrucción Las instrucciones se ejecutan con… Las fases de ejecución son: - Búsquedas (fetch o captación): Traer de memoria la instrucción a ejecutar (apuntada por el CP) - Decodificación: Interpretar la operación a realizar. - Lectura de operandos: Buscar los operandos en función de los modos de direccionamiento - Operación: realizar la operación - Escritura de resultado: escribir el resultado en la ubicación determinada del... Entre las fases fetch y decodificación hay que actualizar el CP. En estas fases son validas aunque la operación a realizar no sea de proceso: - Si es una transferencia la fase de ejecución se reduce a la copia de un dato desde el operando fuente a destino - Si es una bifurcación la evaluación de la condición se suele llevar a cabo durante la fase de decodificación: o Si el salto se toma, se actualiza el contador de programa entre fases o Si el salto no se toma, las fases siguiente no hacen nada 3.3 Operaciones elementales Cada una de las fases de ejecución de una instrucción se descompone en una serie de operaciones más sencillas como…blalblalblalabla. Existen dos tipos: - Operaciones elementales de transferencia. - Operaciones elementales de proceso. Descripción de los elementos hardware: Registros - Elementos de almacenamiento - Dispositivos síncronos #UAHStyle - Activos por flanco (de bajada para nosotros Buffers .Separan los elementos del bus .blablala… Nombrar las señales con una regla de construcción: - Lxx -> cargas - Txx ->transferencias Los elementos de almacenamiento tienen dos bus conexiones al bus: - Una para escribir LOS BUSES NO ALMACENAN INFORMACION Existen diferentes arquitecturas para alimentar la ALU: - Sistema basado en multiplexores - Sistema basado en dos buses Las operaciones elementales de transferencia se encargan de mover datos entre registros Las señales de control involucradas realizan 2 funciones: - Establecer un camino entre el origen y el destino - Copiar un dato en un registro Transferencia entre registros: - Establecer un registro - Salvar en registro 3.3.3 De proceso Las operaciones elementales de proceso se encargan de procesar datos en un operador Las señales de control involucradas realizan 2 funciones: Proporcionar operandos a un operador: Establecer un camino entre los operandos y entradas del operador Las señales… Procesos: - Establecer camino a través de un operador - Salvar en registro La velocidad de reloj la establece el retardo de que el dispositivo que queremos que trabaje…blablablab 3.3.4 Cronogramas (suena apasionante #ironia) #UAHStyle Sea la siguiente ruta de datos: Características de la arquitectura propuesta: - Multiplicidad funcional (paralelismo posible), admite instrucciones de tamaño variable. - Unidad de actualización del contador de programa conectado a la unidad de control. - No es posible trabajar con dos datos de memoria por falta de buses de datos. ¡OJO! Si elimino TBUS se pueden provocar conflictos en el bus. Algunos ejemplos en esa máquina: 1. Fase de búsqueda: Descomposición en operaciones elementales. ACCIÓN Transferir CP a DIR - Establecer camino: TACP - Salvar información: LDIR TIPO Operación elemental de transferencia Transferir contenido de memoria a RI - Establecer camino: TMEM, R/W, IO/M (con esta última se especifica si la dirección es un puntero a memoria o a E/S) - Salvar información: LRI Operación elemental de transferencia. El acceso a la memoria SIEMPRE dura dos ciclos de reloj porque es un acceso lento. En todos los cronogramas la carga se produce al final. #UAHStyle En total consume 3 ciclos, porque el acceso a memoria ocupa 2 ciclos. Si lo hiciésemos con registros activos por flanco de bajada, se haría con 2 ciclos en total. 2. Actualización del contador de programa: Descomposición en operaciones elementales ACCIÓN TIPO Sumar CP con longitud Operación elemental de proceso - Transferir longitud desde UC: DIT - Operación de suma: TR/SM - Salvar nuevo CP: LCP Se puede hacer en un ciclo de reloj. 3. Operación de suma: Descomposición en operaciones elementales ACCIÓN Sumar R1+R2→R3 - Seleccionar R1, R2, R3: SA, SB, SC - Establecer camino con la ALU: TA, TB - Seleccionar operación de suma: SEL - Establecer camino con el banco de registros: TALU - Salvar resultado y estado: LR, LF TIPO Operación elemental de proceso Se puede realizar en un ciclo de reloj 3.4 Caracterización de la UC 3.4.1 Elementos La unidad de control consta de…. T.T - Registros de algo 3.4.2 Funciones La UC es una maquina de estados A cada estado le corresponde activar algunas señales de control (la decodificación no tiene señales de control) #UAHStyle 3.5 El diseño e la UC 3.5.1 Magnitud del problema El diseño de la UC plantea carios retos: - En primer lugar el diseño propiamente dicho: correcto, rápido y fácilmente depurable - El coste - Optimización: o Identificaron de estados adecuada Códigos similares a estados que realicen… o Minimizar el CPI Dado: El repertorio de instrucciones y la ruta de datos La unidad de control indica a la ruta de datos lo que tiene que hacer de noseu… Cada fase de ejecución es también una maquina de estados: - Las fases de lectura de operandos y de escritura de resultados tienen una maquina de estados para cada modo de direccionamiento - La fase de ejecución que tiene la máquina de estados... ¡¡¡EXPLOSION DE ESTADOS!!! (No es coña, lo ponía en las diapositivas) La UC genera señales de control… 3.5.2 Soluciones Dos métodos de diseño: - UC de lógica cableada (circuitos secuenciales): es el circuito más rápido, pero es muy laborioso de diseñar, difícil de depurar. - UC de lógica almacenada: fácil de depurar, simplifica la compatibilidad binaria. Es lento y ocupa mucho sitio Hoy en día todas las UC son cableadas 3.6 Unidad de control cableada Hay tres tipos: - Circuito secuencial - Células de retardo - Contador secuencial 3.7 Control microprogramado Consiste en almacenar las distintas palabras de control correspondientes a cada periodo o fase de ejecución de una instrucción en una memoria D esta forma, generar señales de control es leer posiciones de memoria #UAHStyle Cada palabra de control se llama microinstrucción y por eso las UC diseñadas de esta forma se denominan así. El conjunto de microprogramas que ejecutan las instrucciones e llaman firmware o microcódigo. Una UC microprogramada ha de ser capaz de 3 cosas - Retener en memoria todas las microinstrucciones posibles - Hacer corresponder cada instrucción con su microprograma, es decir, hacer que cada cogido de operación encuentre la dirección donde comienza en memoria el microprograma - Seguir la secuencia del microprograma y encadenar con el siguiente código de operación. 3. 7.1 Formato de las microinstrucciones Esto significa que está desperdiciando mucha memoria (hay muchos 0s). De todas las posibles combinaciones solamente unas pocas palabras tienen un significado real Se denomina Microprogramación horizontal si no se usa codidificación, mientras que llamaremos microprogramación vertical al caso de microinstrucciones codificadas Las microinstrucciones horizontales presentan formatos largos pero son rápidas mientras que las verticales reducen el tamaño de la memoria pero son lentas ya que necesitan descodificación Las señales de control se pueden agrupar en campos: - Señales que gobiernan el acceso al bus de datos - … el acceso al bus de direcciones - … de la ALU - … del banco de registros - …de la memoria - …de la unidad de direccionamiento Señales excluyentes: - Cuando un campo contiene señales que no se pueden activar simultáneamente… Optimización para reducir el CPI: - Hacer varios microprogramas para la misma operación - Añadir control cableado - Hacer varias operaciones elementales en cada microinstrucción Una primera aproximación a la solución del problema sería usar una memoria cuyos punteros estuvieran formados por dos campos: campo de contador de fases, campo código de operación #UAHStyle 7.2 Secuenciamiento Secuenciamiento explicito: - Consiste en incluir en cada microinstrucción la dirección de la siguiente - Los códigos de…. - Inconvenientes: El mayor inconveniente está en la gran cantidad de memoria que emplea - Ventaja: Permite reutilizar secuencias de microprogramas siempre que sean finales… sin necesidad Secuenciamiento implícito: - Consiste en tener ordenadas secuencialmente todas las microinstrucciones… 7.3 Microbifuraciones El mecanismo dependerá del tipo de secuenciamiento utilizado En el secuenciamiento explicito: - Cada microinstrucción lleva la dirección de la siguiente… En el secuenciamiento implícito: - Para poder elegir entre secuencia normal o…. 7.4 Nanoprogramacion Es un sistema que reduce el coste asociado en área de silicio Es una estructura en dos niveles 1. Contiene secuencias de palabras de control que son puntero al segundo nivel 2. Contiene una ordenación arbitraria de palabras de control NO DUPLICADAS Las eficiencias de esta estructura descansan en dos hechos - El numero de palabras de control implementadas debe ser una fracción pequeña del número total de las posibles - Debe darse una cierta redundancia en el uso de las nanoistrucciones [Comparación de tamaños entre microprogramación y nanoprogramacion] A partir de aquí: Segundo Examen 4. La Memoria 4.1 Nociones fundamentales La memoria “alimenta” al procesador durante la ejecución de manera que han de trabajar bien SINCRONIZADOS si se desea un alto rendimiento Procesador Memoria Muchas celdas activas Muy pocas celdas activas #UAHStyle Existe una gran diferencia de rendimiento entre el procesador y la memoria. El sistema de memoria almacena los programas y los datos que requiere el procesador EL programador ve: - Memoria principal: se reserva en memoria al programar - Memoria secundaria: pertenece al sistema E/S y se accede a través del SO de manera transparente. Conviene distinguir la MEMORIA de los DISPOSITIVOS DE ALMACENAMIENTO (Discos duros por ejemplo) que pertenecen al bloque de E/S. La tecnología con la que se realiza la memoria puede cambiar pero siempre requiere elementos capaces de retener uno entre varios estados. El almacén básico es la celda que, cuando codificados en binario, puede retener entre uno o dos estados (bit). Sin embargo, la posibilidad de disponer de tecnologías que sean capaces de conmutar entre dos estados daría lugar a dispositivos de menor tamaño. Normalmente las memorias se referencian por un código que identifica de manera univoca un conjunto de celdas Las celdas se suelen reunir formado una unidad lógica que se conoce como palabra A cada una de ellas le corresponde una posición o dirección. El número de palabras define el número de líneas del bus de direcciones de memoria mientras que el tamaño de la palabra define la longitud del bus de datos. Propiedades de la memoria: - Velocidad - Capacidad de Transferencia - Volatilidad - Necesidad de recuperación 4.1.2 Parámetros: - Capacidad - Organización - Capacidad de direccionamiento - Tiempo de escritura - Tiempo de lectura - Tiempo de acceso - Tiempo de ciclo: el tiempo que tenemos que esperar para volver a hacer una operación de lectura o de escritura - Velocidad de transferencia: tamaño de palabra accedida /tc #UAHStyle 4.1.3 Clasificación - Por su forma de acceso: o Secuenciales o Acceso aleatorio o Por contenido - Por su modo de almacenamiento: o Volátil o No volátil - Por su función o Memoria cache o Memoria nosequé… o …. - Modo de interconexión o Un único puerto o Multipuerta 4.1.5 Las memorias de estado solido RAM, SRAM, EPROM… [Dibujo de una Estructura general de una memoria de semiconductor] Señales de control típicas: - CS o CE: Chip Select o Chup Enable - OE: Output Enable - WE: Write Enable - RAS y CAS: Row Addess Strobe y Coluumn Addres Strobe Cronogramas: - Las especificación de cada memoria deben establecer los márgenes de tiempos para que trabajen concretamente en escritura o lectura RAM - Son memorias en las que se pueden leer y escribir Son de acceso aleatorio Volátiles Estáticas o Dinámicas - Memoria RAM constituida por biestables Rápida pero de elevado consumo energético Ocupa gran área de silicio Sencilla de manejar Tiempo de acceso de más o menos 10 ns SRAM DRAM #UAHStyle - Memoria RAM donde cada bit es un transistor funcionando como un condensador Requiere un continuo refresco para no perder la carga Tiempo de acceso más o menos de 60 ns Ocupa poca superficie de silicio Lenta pero consume poco Multiplicación y refresco la hace más complicada de manejar que la estática Su gran capacidad ha forzado la multiplicación de direcciones para reducir el patillaje (RAS y CAS) - Solo lectura De acceso aleatorio No volátiles o perteneces Existen variantes que permite realizar una escritura inicial ROM “Torre de Babel” #Concepto Aumento de prestaciones: - Solapar etapas de acceso - Acceso privilegiado a bloques - Doblar el reloj (DDR) SSRAM - Memorias SRAM síncronas El tiempo de acceso que se consigue es de 7-12 ns El funcionamiento segmentado está gobernado por un reloj sincronizado con el procesador. EDO (Extended Data Out Dynamic RAM) FPM RAM Direct RDRAM [Mirar los dibujos de las memorias en el Anassagasti] FLASH - Es un memoria RAM no volátil Tiene la particularidad de que no puede ser accedida por palabras sino por bloques Intel fabrica una memoria flash en la que se almacenan dos bits en lugar de uno en cada celda de memoria. 4.1.5 Mapa de Memoria Llamamos mapa de memoria a todo el espacio direccionable por un computador Este espacio viene determinado por el tamaño de las direcciones ya que disponer de una dirección de m bits supone tener un mapa de memoria 2m direcciones #UAHStyle Desde el punto de vista programador, el mapa de memoria se organiza en bytes y a cada byte le corresponde por tanto una dirección. Granularidad Alineamiento: Los lenguajes de programación disponen de directivas para alinear los accesos o sea forzar los punteros emitidos por el procesador sean múltiplos de números enteros de bytes. 4.1.5 Mapa de Memoria (cont.) Ampliación de memoria: - Memoria expandida: o Dirección física de memoria de 20 bits o Se divide en dos campos 15 bits (menor peso) y 6 bits o La tabla almacena un identificador de 11 bits para cada entrada que es una etiqueta de un bloque de memoria expandida o Se reserva en la memoria convencional un espacio de 64KB para 4 bloques de memoria expandida 4.1.6 Verificación de la integridad de datos Un aspecto importante en el diseño de la memoria es el control de errores o verificación de la integridad de datos almacenados. Existes dos formas de conseguirlo - Añadir un bit de paridad por cada 8 bits de datos - Añadir un código de corrección de errores ECC que permite detectar y corregir errores de bits individuales Paridad: Añadimos un bit más que examine la paridad del bit con el que estamos trabajando. ECC (Error correction code) 4.2 Organizaciones alternativas 4.2.1 Memorias Asociativas - Memorias CAM (Content Access Memory) - Memorias de acceso por contenido Celdas de la matriz de búsqueda y celda de matriz de datos [imagen en Anasagasti] Usos típicos: - Tablas de correspondencia - Tablas de traducción de memoria virtual y memoria caché 4.2.2 Memorias multipuerta #UAHStyle Misma latencia de memoria. Mayor ancho de banda. 4.3 Jerarquía de Memoria La memoria es un cuello de botella con dos facetas: - Latencia de memoria (tiempos de acceso son muy grandes) - Ancho de banda (capacidad de transferencia limitada) El problema no tiene una solución fácil: Grande, rápido, barato Dependencia circulares en las opciones de diseño: - A mayor capacidad mayor tiempo de acceso… - … Solución Jerarquía de memoria Organización de memoria en varios niveles: - Cada uno más pequeño, más rápido y más caro por byte que el anterior - Todos los datos de un nivel se encuentran en el inferior. La jerarquía es efectiva por el principio de localidad: - Los programas no acceden al código y a los datos de manera uniforme, aleatoria o equiprobable - Los programas favorecen una parte del espacio de direcciones Localidad temporal: si se referencia un elemento tenderá a ser referenciado pronto Localidad espacial: si se referencia un elemento, los elementos cercanos a él tenderán a ser referenciados pronto En cada momento la jerarquía se gestiona entre 2 niveles adyacentes. La mínima unidad de información es el bloque Acierto (hit) Fallo (miss) éxito en la búsqueda de un bloque en un nivel superior fracaso en la búsqueda Lo importante es el rendimiento (velocidad de ejecución). Tiempos: - Tiempo de acierto: tiempo de acceso al nivel superior - Penalización de fallo: tiempo de reemplazo + tiempo de entrega al dispositivo Tmedio acceso a memoria = tacierto + tfallos · penalización Tm = ta + (1-h) · p #UAHStyle Si la penalización es muy costosa lo que vamos a provocar es que el SO saque ese proceso en ejecución. Dependiendo de los niveles involucrados y del coste temporal de: - Las búsquedas - Los reemplazos - Las transferencias de bloques Su implementación puede ser: HW (caché) o SW (memoria virtual) Las direcciones de memoria se dividen en campos que identifican: - Un elemento de bloque - Identificador de bloque Hay que asegurar la coherencia o consistencia de la información almacenada cuando se escribe en un bloque Todos los datos de un nivel se encuentran en el inferior. Hay que diseñar sistemas que indique la validad o no de un bloque 3.4 La memoria caché 3.4.1 Introducción Es una memoria auxiliar de alta velocidad que se interpone entre la CPU y la memoria principal para acelerar el funcionamiento del procesador La cache está dividida en bloques de longitud fija llamados líneas que contienen temporalmente copias de los bloques de memoria principal. Cada una de las líneas lleva asociada una etiqueta que identifica Dos zonas de memoria: - Las líneas - La tabla con las etiquetas de las líneas o tabla de correspondencia Secuencia de operaciones: - El procesador genera una dirección física de memoria y la envía a caché - La memoria cache traduce la dirección física a dirección caché y comprueba la referencia. 3.4.2 Tipos de organización Organización de caché: #UAHStyle - Correspondencia directa: Cada bloque de memoria principal solo puede cargarse en una línea determinada en la memoria caché. Direcciones de 19 bits que se dividen en tres campos: a. Palabra (8 bits) b. Línea (7 bits) c. Etiqueta (4 bits) Ventajas e inconvenientes: a. Existe una tabla de correspondencias propiamente dicha. b. La comparación de la etiqueta - Totalmente asociativa: un bloque de memoria principal puede colocarse en cualquier línea de la memoria caché. Ventajas e inconvenientes: a. La etiqueta de la dirección debe compararse con todas las posibles entradas de la tabla de correspondencias con el consiguiente retardo b. La comparación se realiza por la búsqueda de… - Asociación por conjuntos: Organización combinación de las dos anteriores que consiste en dividir el primero total de líneas de cache en C conjuntos de V líneas cada uno y aplicar la correspondencia a nivel de conjuntos. Ventajas e inconvenientes: a. El campo conjunto determina aquel sobre el que se ha de buscar asociativamente el bloque solicitado b. … 3.4.2.1 Comparativa de costes y retardos [Formulas anteriores] Sea una memoria principal dividida en B bloques y una memoria caché compuesta de N líneas Si la organización es totalmente asociativo el tamaño será: TAMAÑOasoc_totaL = N (log2B + log2N) Si la organización es asociativa por conjuntos de V vías tendré N/V conjuntos y para cada uno de los la tabla de correspondencia ocupa: V (log2 ((B·V)/N)+log2V) El tamaño total de memoria asociativa: TAMAÑOasoc_totaL = N(log2 ((B·V)/N)+log2V) #UAHStyle El retardo de una memoria asociativa viene dado por la siguiente expresión: RETARDO = lg2B + N 3.4.3 Políticas de reemplazo - Aleatorio - FIFO - LRU El algoritmo que mejor rendimiento presenta es el LRU pero es el más costo de implementar. El tipo de algoritmo tiene mayor importancia en caches pequeñas que en las grandes. 3.4.4 Políticas de escritura Las políticas de escritura, también llamadas políticas de actualización, determinan en que instante se actualiza la información…. Dos posibilidades: - Escritura Directa: escribo en caché y en memoria principal - Postescritura: escribo en memoria principal cuando reemplazo. Se necesita un dirty bit. La escritura directa es más sencilla y garantiza la coherencia en todo momento La postescritura genera menos tráfico en el bus 3.4.4.1 Fallos de escritura Si el acceso a memoria caché es para escritura y el bloque al que queremos acceder no se encuentra nosequenoscuanto… Ante n fallo podemos: - Ubicar en escritura - No ubicar en escritura. La escritura directa suele estar acompañada de no ubicación ya que las posteriores referencias a ese bloque que se deben escribir en memoria principal también y la postescritura suele ubicar el bloque, esperando ser utilizado mas tarde (localidad temporal) Formulas: Acierto (faciertos/naccesos)·100 Fallos (fallos/naccesos)·100 [Formula importante] Tiempo de programa tp = r (CPIejecución + fallos instrucción · pf) · periodo 3.4.5 Rendimiento de la memoria caché #UAHStyle Desagregación (mirar) Fuentes de fallos de caché (las tres C) - Forzosos - Capacidad: cuando la caché no puede contener todos los bloques requeridos por el problema - Conflicto 5. Entrada Salida 5.1 Introducción 5.1.1 Concepto Implementa la comunicación con el exterior. Algunas maquinas tienen un bloque de E/S grande: - Computadores sobremesa, consolas… Mientras que otras lo tienen muy reducido: Supercomputadores dedicados a cálculo intensivo. Cubre otros aspectos: - Comunicación hombre-maquina - Control de procesos - Telemática - Almacenamiento Distinguimos: - Periféricos: dispositivo que implementa un modo especifico de comunicar datos entre - Unidad o modulo de E/S 5.1.2 Elementos ¿Por qué los periféricos no se conectan directamente a los buses? - Gran diversidad de periféricos - La velocidad de transferencia de los periféricos es muy diferente al del procesador - Los formatos de los datos de los dispositivos externos son muy diferentes a los del computador. 5.2 Periféricos Tipos de periféricos: - Comunicación hombre-maquina - Comunicación maquina-maquina o Telemática o Control de procesos - Almacenamiento masivo #UAHStyle Partes de un periférico: - Controlador o Se relaciona con el procesador o CPU o Su misión es doble: Protocolo de transferencia Transferencia propiamente dicha - Dispositivo o Se relaciona con el exterior o Basado en un fenómeno físico o químico transforma en… Operaciones de lectura de E/S: - Requiere un buffer triestado para no cargar el bus de datos - Además pueden tener un registro interno o una memoria buffer Operaciones de escritura E/S: - Requiere un registro donde almacenarse temporalmente hasta que el dispositivo pueda darles curso - Se debe a la lentitud del periférico respecto al procesador - Este registro puede ser una memoria buffer organizada por una cola 5.3. Unidad de E/S 5.3.2 Funciones Control y temporalizarían: - La CPU puede comunicarse con varios periféricos simultáneamente Comunicación con el procesador: - Decodificar las ordenes - Intercambio de datos - Información de estado - Reconocimiento de dirección Comunicación con los periféricos: - Intercambio de órdenes, estado y datos Almacenamiento temporal de datos: - Adaptación de velocidad Detección de errores 5.3.3 Espacio de diseño #UAHStyle Protocolo de transferencia Mapa de E/S: Selección de periférico Sincronización de CPU-Periférico 5.3.4 Protocolos de transferencia - Transferencia Síncrona - Transferencia asíncrona 5.4 Mapa de Entrada/Salida Los dispositivos de entrada/salida se identifican mediante un código que se suelen denominar (dirección o puerto) Cada periférico suele tener un rango de puertos con funciones diversas Las direcciones de los puertos de E/S se emiten por el bus de direcciones De manera análoga al mapa de memoria, el mapa de E/S es el conjunto de puertos que dan acceso al dispositivo periférico. La forma de direccionas puertos de E/S es similar a la de posiciones de memoria: - Si los mapas son comunes, se suelen agrupar los puertos en un rango de direcciones con objeto de no “participar” excesivamente la memoria El mapa de E/S esta desdoblado: No hay una correspondencia univoca entre el elemento accedido en escritura y lectura Los accesos a un puerto de E/S en escritura no tienen porque ser sobre el mismo elemento físico que en lectura, incluso pueden ser más de 2… Depende: - Tipo de accesos (lectura o escritura) y señales de control involucradas - Combinación con valor de un determinado registro de control - Secuencia de accesos Cada periférico suele emplear un rango de puertos de E/S para su control y… 5.6 Sincronización Dos aspectos a tener en cuenta: - Inicio de la transferencia - Transferencia propiamente dicha Tipos de sincronización: #UAHStyle - E/S programada E/S por interrupción Acceso directo a memoria (DMA) 5.6.1 E/S Programada La CPU inicia la transferencia y la lleva a cabo. Existen dos tipos: - Incondicional - Condicional 5.6.2 E/S por interrupción En las transferencias de E/S por interrupción el periférico realiza la petición de servicio. Mirar la secuencia del procesamiento de la interrupción. Tiene dos bloques (una HW y otra SW) Mecanismos de interrupción: Para poder manejar la E/S por interrupción hemos de diseñar mecanismos capaces de gestionar las siguientes situaciones: - Aceptación de interrupciones - Ubicación de la rutina en curso - Identificación de la rutina de servicio CPU con una única línea de interrupción. CPU con varias líneas de interrupción CPU con líneas de petición y de aceptación de la interrupción Encadenamiento de periféricos o Daisy chain Interrupciones vectorizadas Gestión de interrupciones mediante controlador PIC 5.6.3 E/S por DMA En el acceso directo a memoria el controlador del periférico se comunica directamente con la memoria del computador. Este tipo de transferencia de E/S tiene sentido solamente cuando se mueven bloques de datos Requieren una programación previa del controlador de DMA que consume tiempo. Secuencia: 1. El periférico envía una señal HW de solicitud al procesador 2. El procesador termina un ciclo de bus (no la ejecución de una instrucción) antes de responder a la solicitudes de DMA 3. El procesador emita la señal HW de reconocimiento, cede los buses al controlador de DMA y comienza la transferencia de datos. Existen dos formas básicas para realizar el DMA: - Por memoria multipuerta - Por robo de ciclo: o DMA por ráfagas #UAHStyle o o DMA transparente DMA por robo de ciclo 6. Almacenamiento masivo Grabación magnética: - Sobre un soporte adecuado, se deposita un material magnético Es un dispositivo de almacenamiento masivo no volátil Es de acceso aleatorio por bloques y en principio cada bloque tiene el mismo tiempo de acceso Platos finos, recubiertos por un material sensible a alteraciones magnético Cada disco dispone de dos diminutos cabezales de lectura y escritura: - Se encuentra flotando en la superficie - Generan señales eléctricas que alteran los campos - Durante el proceso de.. Las partículas orientadas magnéticamente en un sentido u otro pueden representar dos estados, 0 y 1. Se requiere un proceso de modulación: - Por tanto, es un dispositivo analógico - Se puede almacenar mas información trabajando con múltiples frecuencias - Junto a… La distancia entre el cabezal y el plato del disco también determina a densidad de almacenamiento del mismo, ya que cuanto más cerca este el uno del otro… 6.2.3 Estructura lógica En el caso de los paquetes de discos, las pistas del mismo diámetro en las diversas superficies… Cada plato, cada pista y cada sector llevan un código escrito que los identifica de manera univoca Esta información está grabada y se llama formato de bajo nivel Cada conjunto de datos lleva un identificador único formado por tres códigos (plato, pista, sector). Ahora bien, no todos los fabricantes los organizan de la misma forma La misma capacidad de almacenamiento puede conseguirse con diferentes combinaciones de platos, pistas y sectores. Esto es ello que se conoce como geometría del disco duro. Los sectores suelen agruparse en clusters o unidades de asignación. Un cluster es la mínima unidad de lectura o escritura del disco 6.2.5 Formato de nivel alto #UAHStyle Proceso de lectura de un fichero: - Buscar fichero en la tabla - Leer los clusters donde se ubica - Acceder a los clusters indicados Proceso de escritura de un fichero: - Asignar entrada en la tabla - Buscar clusters libres - Escribir los clusters libres y anotarlos en la tabla Ver divisiones lógicas de alto nivel (S.O.): - Paginas o segmentos de memoria virtual - Cubetas en bases de datos 6.2.6 Tiempo de acceso Tiempo medio de búsqueda + retardo rotacional (latencia) + tiempo de transferencia 6.3 Discos ópticos 7. Representación Visual 7.2 Modo Texto Cada celda presenta un carácter mediante dos bytes: - Byte de carácter - Byte de atributo Paleta de color en modo texto - 8 colores combinación de 3 primarios (cada primario tiene valor 0 o 1) - 8 colores con sobreintensidad que dan lugar a una paleta basada en la anterior pero con tonalidades más claras (solo para el carácter) La pantalla de video que vemos en cada instante esta almacenada en un área de memoria (memoria de video). Por cada celda tenemos 2 bytes. La controladora de video lee la memoria de video cada vez que refresca la imagen del monitor. 7.3 Modo grafico #UAHStyle La codificación del color se funda en la descomposición en colores primarios. La obtención de cualquier color, tanto en video como impresa, se basa en composición de primarios. La codificación de cada color es un problema… 7.3.1 Teoría del color Existen 2 formas de considerar los colores según la fuente de la luz: - Luz reflejada: colores sustantivo - Luz emitida: colores aditivos Sustantivo: hace referencia a la percepción de los colores al reflejarse la luz sobre un objeto, lo que produce que este absorta de ciertas longitudes de onda, reflejando otras, una mezcla va a dar lugar al color final del objeto. Colores primarios: amarillo, cian y magenta Aditivos: Los colores se perciben como longitudes de onda que pasan directamente a nuestros ojos, sin ser reflejadas previamente por ningún cuerpo, como es el caso de la luz directamente percibida de una fuente luminosa (bombilla, pantalla). Colores primarios: Rojo, verde y azul. A partir de la mezcla de colores primarios obtenemos los colores secundarios y mezclando estos obtenemos los terciarios. 7.3.2 Codificación de color La codificación del color se realiza en base a los colores aditivos primarios. RGB. ¿Qué variedad de colores deseamos representar? Profundidad del color A mayor numero de niveles de intensidad mayor variedad de colores. Profundidad de color: - 8 bits - 16 bits - 24 bits 256 colores 65535 colores 16777216 colores Casi todos los periféricos trabajan con color verdadero. Las profundidades de color de 8 y de 16 bits se constituyen con “paletas de color”. Color verdadero: A cada color se le corresponde un código RGB Paletas de color: cada color es un índice de entrada a una tabla (paleta) que devuelve como salida un código RGB. 7.3.3 Resolución Numero de pixels que se pueden distinguir por unidad de superficie Cuanto más pequeño sea el pixel mayor es la calidad de imagen 7.4 Formatos gráficos #UAHStyle Dos enfoques: - Mapa de Bits: gran volumen de información, resolución fija. V e I: carga de almacenamiento grande, carga de computacional grande - Vectorial: Describimos una imagen como una serie de líneas o figuras. V e I: Carga computacional grande, carga de almacenamiento pequeña Los ficheros gráficos se suelen comprimir. Formatos de imagen: - PCX: 3 partes (cabecera 128 bytes, bitmap y paleta) - BMP: Es independiente del dispositivo, admite compresión, admite diferentes de profundidades de color Formatos de video: - MPEG: Visión en tiempo real, solo información captable por el ojo humano, cuadro base y diferencias con el anterior, fácil de transmitir, requieres mucho HW - AVI: Bueno para pequeñas aplicaciones, compresión de CODEC Impresión: a la hora de imprimir hay que efectuar una conversión de la codificación RGB a la codificación CMYK (colores primarios sustractivos). 8. BUSES 8.1 Introducción Dentro de un computador lo importante es mover datos: - Información codificada a nivel de registro. - Buses paralelos (conjunto de líneas cuyos extremos conectan varios dispositivos) Fuera del computador se transfieren mensajes: - Organización en tramas y/o transferencia de cadenas de caracteres - Buses serie: mínimo canal de comunicación del que cuelgan otros dispositivos o Bus USB 8.1.2 Elementos - Líneas de control - Líneas de datos (separadas o multiplexadas) Una transacción de bus típica tendría: 1. Petición de bus 2. Obtención de bus 3. Envío de dirección 4. Envío/recepción de datos 8.1.3 Espacio de diseño La velocidad está limitada por factores físicos: #UAHStyle - Longitud de bus Numero de dispositivos conectados El ancho de banda del bus limita la productividad de los sistemas conectados a el Ancho de banda y acceso rápido pueden ser 2 objetivos que entren en conflicto Dar soporte a dispositivos muy diferentes en latencia y velocidad de transferencia complica el diseño. 8. 2 Tipos de Buses Bus de procesador-memoria Síncrono Entrada/salida Asíncrono Backplane 8.2.1 Bus procesador-memoria Longitud pequeña, de alta velocidad, adaptado a la velocidad a la que trabaja la memoria. Se conoce como bus local o FBS (front side bus) 8.2.2 Bus de entrada-salida Longitud grande, da servicio a dispositivos con ancho de banda muy diferentes, no suelen estar conectados directamente a la memoria (requieren un adaptador de bus [bridge]). 8.2.3 Bus de backplane Están pensados para el procesador, la memoria y los dispositivos E/S coexistan en un único bus. Hay equilibrio de requerimientos. Suelen estar en un chasis (Por ejemplo PCI) 8.2. (cont.) Los buses de entrada/salida y backplane suelen estar estandarizados. Los diferentes tipos de buses se pueden conectar mediante adaptadores adecuados. (Jerarquía de buses). 8.2.4 Bus síncrono Entre las señales de control hay un reloj y el protocolo de comunicación están gobernado por la señal de reloj (bus ISA, PCI) El protocolo lo gobierna un autómata 8.2.5 Bus asíncrono No tiene reloj y por tanto, no sufren problemas de clock skew: Se establece un protocolo de handshaking para coordinar las transferencias de si ya claro…. 8.3 Rendimiento #UAHStyle 8.3.1 Ancho de Banda Depende de: - Anchura del bus de datos - Líneas de direcciones y datos separadas o multiplexadas - Transferencia por bloques Puede afectar al tiempo de respuesta. 8.3.2 Acceso al bus Requiere de la participación de uno o varios maestros (Bus Master) que controlen el acceso y las peticiones de accesos El procesador siempre es maestro y la memoria esclavo No es conveniente que el procesador sea el único maestro: - Ya que se sobrecarga de trabajo - Es necesario establecer un sistema de arbitraje de bus 8.4. Arbitraje de bus Se encarga de gestionar: - Petición de bus - Concesiones de bus - Liberaciones de bus Mediante líneas separadas o dentro de las líneas Tipos: - - - En serie (Daisy Chain): las concesiones se propagan de dispositivo en dispositivo por orden de prioridad. Es un sistema simple pero no garantiza la imparcialidad. Paralelo centralizado: Múltiples líneas de petición a un árbitro centralizado. Si hay muchas peticiones el árbitro puede convertirse en cuello de botella. PCI usa este sistema Distribuido por autoselección: Múltiples líneas de petición o Cada dispositivo pone un código sobre las líneas de petición o Al leer las líneas de petición, los dispositivos conocen quien ha recibido la concesión. El bus NuBus de Macintosh usa este esquema Distribuido por detención de errores: Los dispositivos solicitan el bus independientemente, si se produce una colisión…. Blablablá 8.5 Buses normalizados 8. 6 Papel del sistema operativo #UAHStyle Ejercicios Tema 1 1. Realizar un circuito que convierta los números de 8 bits en signo-magnitud a números en exceso 128. Incluye un circuito que detecte un posible desbordamiento en caso necesario. Signo-magnitud [-127, 127] Exceso 128 [-128, 128] (2n-1) Positivos MSB(s), y el resto igual NegativosMSB(s), y el resto se cambia de signo en C-2 NO HAY DESBORDAMIENTO de Signo-Magnitud a Exceso 128 6. Queremos diseñar un sumador con selección de acarreo de 16 bits.. Podemos usar bloques propagadores de 2, 4 y 8 bits. Construye el mejor sumador posible suponiendo que los conmutadores tienen un retardo equivalente a 2 niveles. Propagadores de tamaño homogéneo K=2 Retardo = propagador + red de puertas + conmutador retardoRCA = 2k + 1 (nivel) retardoRCA Retardok=2 = 2 · 2 + 12 + 2 = 18 niveles 2k nº bloque = = =8 Retardok=4 = 8 + 4 + 2 = 14 niveles Retardok=8 = 16 + 2 = 18 niveles Sumador NO homogéneo 2 4 4 niveles adicionales = 2 8 12 niveles adicionales = 4 8 8 niveles adicionales = K = 2 (x4) K=4 (x2) K = 2 (x2) K=4 (x3) 1 conmutador + 1 red de puertas 1 conmutador + 5 red de puertas 1 conmutador + 3 red de puertas 4 + (6 – 2) · 2 + 2 = 14 niveles 4 + 6 + 2 = 12 niveles 1. Disponemos de un computador de instrucción única, es decir, su repertorio se reduce a la instrucción: resta y salto si negativo. Esta instrucción tiene tres operandos que son, cada uno de ellos, direcciones de una palabra en memoria: rsn a, b, c Su funcionalidad es la siguiente: mem[a] = mem[a] - mem[b]; si (mem[a]<0) entonces ir a c #UAHStyle La instrucción restará el número de la localización de memoria b del número en la localización de memoria en a y situará el resultado en a, sobrescribiendo el valor previo. Si el resultado es mayor o igual a 0, el computador tomará la siguiente instrucción de la localización de memoria inmediatamente posterior a la instrucción actual. Si el resultado es menor que 0, la siguiente instrucción se toma de la localización de memoria c. Este computador no dispone de registros. Escribe un programa para este computador que copie el valor contenido en la localización de memoria a en la localización de memoria b. Mem[a] mem[b] Inicio: rsn temp, temp, +1 rsn temp, a, +1 rsn b, b, +1 rsn b, temp, +1 ;mem[temp]=0 ;mem[temp]= -mem[a] ;mem[b]=0 ;mem[b]= -mem[temp]=mem[a] Inicio: rsn temp, temp, +1 rsn a, b, +1 rsn temp, a, +1 rsn b, temp, +1 2. El formato del repertorio de instrucciones de un procesador se ha diseñado con el objetivo de minimizar el espacio de representación. De esta manera, se han especificado dos formatos para los códigos de operación: uno “regular” y otro “extendido”. El formato “regular” proporciona las operaciones sobre un campo de 6 bits mientras que el “extendido” utiliza 8 campos de extensión, de entre los posibles códigos de 6 bits del formato “regular”, para llamar a un campo código de operación extendido de 3 bits. Sabemos que el formato “regular” se usa aproximadamente un 90% de las ocasiones en los programas de test de los que disponemos. Sabiendo todo esto responder a las siguientes preguntas: a) número de instrucciones del formato “regular” 26 – 8 = 56 operaciones b) número de instrucciones del formato “extendido” 26 – 8 = 56 operaciones c) número total de instrucciones distintas que se pueden codificar con este sistema #UAHStyle 56 + 64 = 120 operaciones d) tamaño del campo código de operación en el caso de utilizar únicamente el formato regular para el número de instrucciones que maneja este procesador [ ] 7 bits e) tamaño medio del formato para las aplicaciones de test 6 · 0,9 + (6 + 3) * 0,1 = 6,3 bits f) tamaño medio si la distribución de instrucciones fuera equitativa = 7,6 bits g) porcentaje de uso del formato “extendido” que hace ineficaz el diseño. 6(1 – x) + (6 + 3)x = 7 bits ; x = =0,33 33% 6. Un procesador ejecuta saltos condicionales (BR cc) utilizando el modo de direccionamiento relativo al PC. Los saltos incondicionales (JMP), sin embargo, solamente admiten el modo de direccionamiento absoluto a memoria. El procesador genera direcciones de 32 bits y los accesos a memoria están alineados a palabras de 32 bits, es decir, los dos bits de menor peso son siempre '00'. El formato de instrucción del salto condicional relativo a PC es el siguiente: 31 30 29 28 27 Operación 6 26 25 24 23 RA 5 22 21 20 19 18 17 16 15 14 13 12 11 10 9 8 7 6 5 4 3 Desplazamiento 21 donde la condición de salto se evalúa sobre el registro especificado en el campo registro (RA). Explíquese por qué el siguiente código hace que el compilador genere error: aquí: BRZ r1, allí ::::::::::::::: ::::::::::::::: allí: ADD r1, r1, r1 #UAHStyle 2 1 0 siendo las posiciones de memoria etiquetadas las siguientes: aquí allí 01 00 00 00h 08 00 00 00h y BRZ es la instrucción de salto si es cero el registro, en este caso r1. ¿Cómo se puede solucionar este problema? (Los 2 bits de menor peso son siempre 0) Realmente tenemos desplazamiento de 23 31 30 29 28 27 26 25 Operación 6 PC 24 23 22 21 20 19 18 17 16 RA 5 15 14 13 12 11 10 9 8 7 6 5 4 3 2 Desplazamiento 21 PC + def Long 222 No puede llegar porque necesita 24 bits de salto. La solución sería usar un JMP. 2. Sobre la ruta de datos de la figura, construye los cronogramas correspondientes a las siguientes operaciones: - r4 ← r5 + [r6 + desplazamiento] - Jxx CP + desplazamiento - r3 ← [r12 + desplazamiento] - [r9 + desplazamiento] ← r7 - r16 ← r10 - r4 ← r5 + [r6 + r7 + desplazamiento] - r4 ← r5 + [r6 + desplazamiento] DIT, TA, SA, MUX, TAEA, LDR (todo esto ha consumido 1 ciclo) TMEN, R/W, IO/M, TA, SA, SEL, TALU, SC, LR, LC (2 ciclos, porque los accesos a memoria cumplen 1 ciclo) #UAHStyle 1 0 00 8. La unidad de control de un procesador es microprogramada. Con el fin de disminuir el coste en área de silicio se barajan 2 posibilidades: realizar nanoprogramación o microprogramación vertical en un único nivel. Asumiendo que el número de señales de control es n = 100, que el número total de palabras de control es k = 830, la tasa de palabras de control no repetidas (ρ) es 2/3 de k y el secuenciamiento del primer nivel de microprogramación de tipo explícito, determinar el factor de compresión de las palabras de control que iguala ambas opciones de diseño. n = 100 K = 830 ( ) ( ( ) ) ( ) ¿c? Si la compresión Es factible de un solo nivel es de 0,76 es igual a si uso nanoprogramacion. 6. La compañía Mintel Limited, líder en el sector de los microprocesadores, está a punto de sacar al mercado un nuevo procesador cuya unidad de control es microprogramada en un único nivel y con secuenciamiento explícito. Uno de sus jóvenes ingenieros, titulado por la Universidad de Alcalá, le ha propuesto al director jefe del proyecto una modificación en dicha unidad de control de manera que se implemente en 2 niveles en lugar de uno. Argumenta que ese cambio hará posible aumentar el tamaño de la caché de instrucciones de primer nivel haciendo que el rendimiento final del producto se vea sensiblemente incrementado desbancando a la competencia, AMB Enterprise, definitivamente. El director del proyecto sabe que su procesador maneja n señales de control diferentes y que k es el número total de microinstrucciones (palabras de control) necesarias para implementar todas las instrucciones del repertorio aunque de ellas solamente 2/3 son distintas entre sí. Está intentando evaluar si la propuesta de su sagaz colaborador es conveniente o no. ¿Crees que nuestro joven ingeniero tiene razón? Justifica tu respuesta cuantitativamente sabiendo que n = 100 y k = 830. n = 100 K = 830 ( ) ( ( ) ( ) ( ) ) #UAHStyle El joven ingeniero tenía razón. #UAHStyle