Universidad Tecnològica de Querètaro

Anuncio

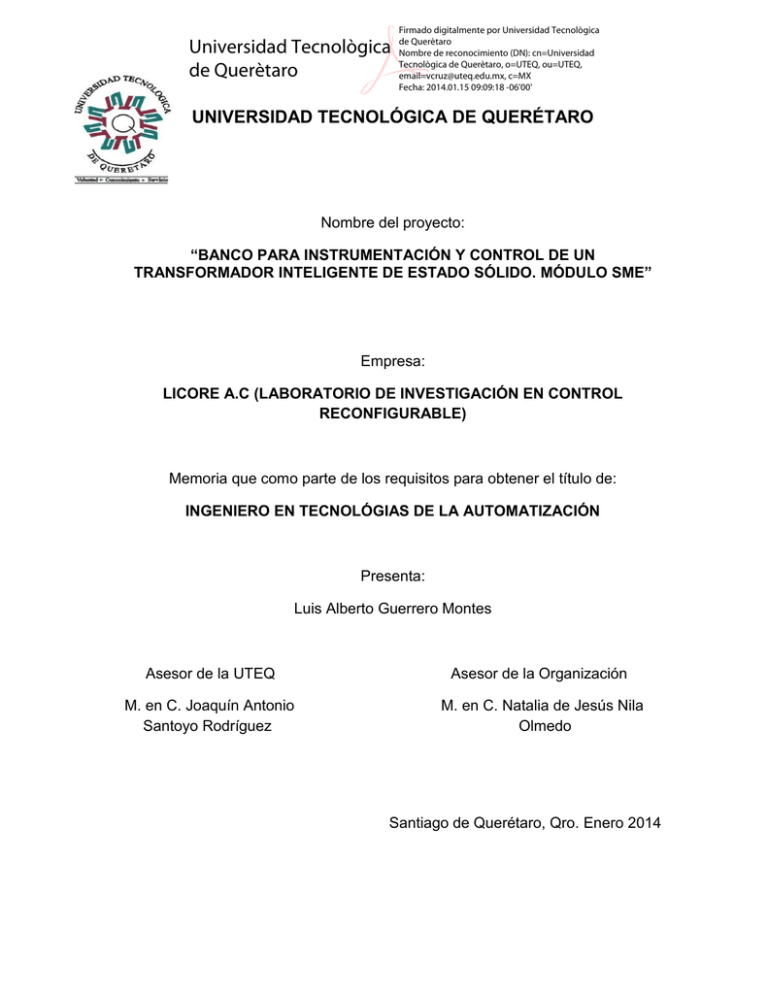

Universidad Tecnològica de Querètaro Firmado digitalmente por Universidad Tecnològica de Querètaro Nombre de reconocimiento (DN): cn=Universidad Tecnològica de Querètaro, o=UTEQ, ou=UTEQ, [email protected], c=MX Fecha: 2014.01.15 09:09:18 -06'00' UNIVERSIDAD TECNOLÓGICA DE QUERÉTARO Nombre del proyecto: “BANCO PARA INSTRUMENTACIÓN Y CONTROL DE UN TRANSFORMADOR INTELIGENTE DE ESTADO SÓLIDO. MÓDULO SME” Empresa: LICORE A.C (LABORATORIO DE INVESTIGACIÓN EN CONTROL RECONFIGURABLE) Memoria que como parte de los requisitos para obtener el título de: INGENIERO EN TECNOLÓGIAS DE LA AUTOMATIZACIÓN Presenta: Luis Alberto Guerrero Montes Asesor de la UTEQ Asesor de la Organización M. en C. Joaquín Antonio S Santoyo Rodríguez M. en C. Natalia de Jesús Nila Olmedo Santiago de Querétaro, Qro. Enero 2014 1 RESUMEN La presente memoria abarca el contenido que se llevó a cabo para realizar un sistema que nos permita monitorear y controlar las variables analógicas y digitales de un transformador inteligente de estado sólido (TIES), para lo cual es necesario diseñar y desarrollar un sistema para intercomunicar dispositivos en el TIES así como analizar el comportamiento del sistema. El proyecto se orientó hacia el control distribuido en la distribución de energía eléctrica en donde se implementó por medio de un sistema de control distribuido aplicado a sistemas embebidos en un dispositivo FPGA utilizando como interfaz de comunicación el Avalon. 2 SUMMARY This document work proposes distributed digital control of a solid state transformer intelligent (SSTI) using a field programmable gate array (FPGA), that allows us to monitor and control analog and digital variables. In particular the generation, transmission and distribution, these are the main parts of modern power system in which the distribution transformers have a key role. These are based on a modular structure is that the most interesting topology because of its superior controllability. The digital implementation is inevitable to achieve higher performances, improved reliability, and an easy development. In addition, with implementing complex control algorithms, multiple interfaces, and a large number of internal variables is a great achievement for this new technology. My experience at LiCORE AC was very comfortable because there I did different activities like the design and programming with FPGA. I also learned how to perform the welding montage surface and development with the news technologies about the solid state transformer. 3 DEDICATORIA El presente trabajo está dedicado principalmente a las dos personas más importantes de mi vida mi padre y mi madre, así mismo a mis hermanos quienes estuvieron al pendiente de mí en esta etapa de mi formación. A ti madre que aunque lamentablemente no estas de cuerpo y alma entre nosotros eres parte fundamental e importante en mi formación la cual he alcanzado hasta el día de hoy. A ti padre por darme todo ese apoyo durante la carrera por madrugar junto conmigo y darme la posibilidad de tener este grado de estudios, por darme tu apoyo incondicional y que a pesar de un par de intentos fallidos jamás dejaste de creer en mí, al contrario me diste alientos suficientes para no decaer ni darme por vencido. Hoy por hoy soy quien soy gracias a ustedes por darme la vida y hacer de mí un hombre de bien, por apoyarme sin importar las circunstancias económicas y familiares. Esto va para ti madrecita hermosa, bien sé que desde el cielo estarás orgullosa de mi como siempre lo he estado de ti por todos tus logros, por cada uno de tus consejos, regaños y enojos. 4 AGRADECIMIENTOS Agradezco a todas aquellas personas que estuvieron conmigo durante este lapso de la ingeniería, a mi hermano José Miguel Guerrero Montes por brindarme un gran apoyo económico por permitirme llegar a su casa y vivir ahí por casi dos años, a los maestros por guiarme y brindarme algunos de sus conocimientos fortaleciendo los míos, por aquellas cargas de trabajo y proyectos pero que gracias a todo esto me voy contento y con grandes conocimientos, a todos y cada uno de mis compañeros por su apoyo físico y moral durante las clases en el aula y la entrega de trabajos finales los cuales siempre eran los más conflictuosos, pero finalmente pudimos lograrlo. 5 ÍNDICE Página Resumen……………………………………………………………………….. 2 Summary……………………………………………………………………….. 3 Dedicatorias……………………………………………………………………. 4 Agradecimientos………………………………………………………………. 5 Índice……………………………………………………………………………. 6 I. INTRODUCCIÓN……………………………………………………… 7 II. ANTECEDENTES…………………………………………………….. 10 III. JUSTIFICACIÓN………………………………………………………. 15 IV. OBJETIVOS……………………………………………………………. 16 V. ALCANCE………………………………………………………………. 17 VI. ANÁLISIS DE RIESGOS……………………………………………… 18 VII. FUNDAMENTACIÓN TEÓRICA……………………………………... 20 VIII. PLAN DE ACTIVIDADES…………………………………………….. 39 IX. RECURSOS MATERIALES Y HUMANOS…………………………. 31 X. DESARROLLO DEL PROYECTO…………………………………… 32 XI. RESULTADOS OBTENIDOS………………………………………… 49 XII. CONCLUSIONES Y RECOMENDACIONES………………………. 51 XIII. ANEXOS………………………………………………………………... 52 XIV. BIBLIOGRAFÍA………………………………………………………… . 59 6 I. INTRODUCCIÓN La energía eléctrica es una fuente de energía renovable que se obtiene mediante el movimiento de cargas eléctricas que se produce en el interior de materiales conductores. El origen de la energía eléctrica está en las centrales de generación, determinadas por la fuente de energía que se utilice. En el ámbito económico y tecnológico, la energía hace referencia a un recurso natural y los elementos asociados que permiten hacer un uso industrial o económico del mismo. Generación, transmisión y distribución son las tres partes principales del sistema de potencia moderna, en la que los transformadores de distribución tienen un papel fundamental [1]. La distribución de la energía es la parte del sistema de suministro eléctrico cuya función es disminuir la intensidad de energía para dar un suministro desde la sub-estación de distribución hasta los usuarios finales. Un transformador transfiere energía eléctrica de un circuito eléctrico a otro, sin cambiar la frecuencia, a través de los principios de la inducción electromagnética. El poder de los transformadores es habilitar la alta eficiencia y larga distancia de transmisión de energía al aumentar la tensión a uno mayor en el lado de la generación. En el lado del sistema de distribución, esta alta tensión se dejó para uso industrial, comercial y uso residencial. 7 La aparición de convertidores de alta potencia hace la red eléctrica moderna más activa de lo que era antes. Una de las líneas de investigación en esta área es el transformador inteligente de estado sólido (TIES) [2,3 y 4] que tiene por objeto sustituir al transformador convencional de 50/60 Hz por medio de alta frecuencia aislado de AC/AC. En [5] se presenta una opinión tecnológica para el desarrollo del TIES de la red de distribución, con especial atención a la siguientes áreas: alta tensión y de potencia de alta frecuencia, dispositivos de alta potencia y transformadores de alta frecuencia, conversor AC/AC de topologías y aplicaciones de transformadores inteligentes de estado sólido en el sistema de distribución. El TIES es esencialmente un circuito electrónico de potencia y una de sus características esperada es su reducción en peso y volumen mediante el aumento de la frecuencia de funcionamiento. Los TIES son uno de los elementos principales de las redes eléctricas inteligentes (REI) [4]. Las REI son sistemas eléctricos que ayudan a mejorar la generación, producción y distribución de energía eléctrica y están fuertemente relacionados con la transición hacia tecnologías más limpias [2,3]. La función de los TIES es habilitar una interfaz flexible, controlable y bidireccional para mejorar la eficiencia y productividad en una red eléctrica. La configuración de control para los TIES es más compleja que algunas otras funcionalidades potenciales de un transformador convencional. Por otro lado, la aplicación de los dispositivos de estado sólido y circuitos hacen que la 8 regulación de voltaje y corriente dé la posibilidad de recordar la amplia aplicación de los dispositivos FACTS (acrónimo del inglés, flexible ac transmission systems). Esto hace prometedoras ventajas como el control de flujo de potencia, bajada de tensión etc., lo cual no es posible para transformadores convencionales [5]. Para realizar un control eficiente en la generación, distribución y consumo de la energía se tomara en cuenta un sistema de control distribuido (DCS por su acrónimo del inglés distributed control system), el cual se refiere a un sistema de control, en donde el controlador no se encuentra en una ubicación central sino que se distribuye en todo el sistema por medio de sub-sistemas. El sistema de los controladores está conectado por redes de comunicación y monitoreo para llevar un control respecto del TIES. Este proyecto propone el monitoreo de las variables corriente y voltaje en el transformador mediante una estructura digital implementada en FPGA (acrónimo del inglés Field Programmable Gate Array). El FPGA tendrá un diseño para integrar un procesador NIOS de ALTERA. En particular, los requisitos importantes para la estructura de control del TIES distribuido debe tener la capacidad para transferir y supervisar un gran número de señales. 9 II. ANTECEDENTES A continuación se presentan diferentes trabajos que anteriormente se han realizado respecto al control distribuido en los TIES. En [6] se presenta un estudio de aplicación en electrónica de potencia del procesador NIOS II, proporcionada por ALTERA para ser implementado en FPGA. El procesador NIOS II ha sido empleado con muy buenos resultados en este proyecto, demostrando ser, junto con DSP y microcontroladores, una alternativa para controlar las aplicaciones en la electrónica de potencia. Las ventajas que ofrece esta opción son la flexibilidad y el paralelismo. En [7] se analiza la aplicación del procesador NIOS II en un convertidor para la corrección del factor de potencia. Este procesador fue proporcionado por ALTERA para ser implementado en FPGA. El FPGA es capaz de realizar un procesamiento en paralelo, modificar el hardware y también ofrece la posibilidad de implementar microprocesadores, que se pueden programar en lenguaje ensamblador o “C” estándar. En [8] se presenta el diseño, implementación y prueba de un controlador industrial multiprocesador basado en un procesador de punto flotante de señal digital (DSP) y un FPGA, que funcionan cooperativamente. Consiste de un USB, ejecutado con un uso mínimo del núcleo DSP y una red de área de controlador, bus que permite el control distribuido. 10 En [9] se presenta el diseño de un control de cadena circular, donde hay una regulación de voltaje A/C de salida y equilibra la distribución de corriente entre los inversores individuales. Se logra por medio de un conjunto de superficies de conmutación y de las leyes de control de deslizamiento correspondientes. Estas leyes de control se han aplicado por medio de un FPGA. Además de una estrategia de gestión de energía para determinar que los inversores se encuentran en ON/OFF de acuerdo a la demanda de energía. En [10] se presentan varios módulos para aplicaciones de electrónica de potencia y también se propuso un sistema de control distribuido autónomo para energía monofásica de inversor, con un controlador de hardware basado en FPGA utilizando un CPU. Se discuten las ventajas del sistema de control de hardware basado en FPGA. En [11] se propone un sistema de control totalmente digital donde dicho sistema se compone de un controlador maestro basado en DSP en combinación con un número múltiple de tarjetas DSP esclavos, tableros FPGA, microcontroladores, un controlador lógico programable (PLC), un ordenador industrial y sus periféricos en la interacción. La topología del controlador propuesto proporciona una mayor fiabilidad, redundancia, modularidad, facilidad de implementación e Inmunidad. 11 En [12] se propone el control digital basado en FPGA para un convertidor elevador de corrección de factor de potencia con el control en modo corriente media. Se presenta el análisis de pequeña señal del circuito de corriente interior y lazo externo de tensión. En [13] se propone una arquitectura flexible de gestión inteligente de la corriente continua en base a módulos bidireccionales controlados digitalmente idénticos que pueden ser configurados mediante software para permitir un diseño sencillo del sistema, la flexibilidad excepcional y la optimización del uso de los recursos disponibles. En [14] se presenta el diseño e implementación de un control digital y un módulo de control para un sistema de alimentación ininterrumpida AC / DC UPS (acrónimo del inglés Uninterrupted Power System). Se desarrolla un hardware y software del sistema. El control digital propuesto y el sistema de monitoreo permite darse cuenta de la complejidad de los algoritmos y de esta manera aumentar la fiabilidad y la eficiencia del UPS. En [15] se presenta un nuevo enfoque para la implementación basada en FPGA de un regulador de corriente predictivo de un convertidor multinivel. Este enfoque también tiene como objetivo reducir la frecuencia de conmutación media y obtener el equilibrio de tensión del punto neutro. El propósito es aplicar el estado de conmutación en el mismo período de muestreo, utilizando el mínimo de recursos del FPGA. 12 En [16] se propone un banco de pruebas de simulación en tiempo real. El núcleo embebido procesador, periféricos y el modelo de convertidor de potencia se implementan en un FPGA. Donde el periodo de muestreo ha sido determinado por medio de simulación de señales mixtas. En [17] se propone el método de aplicación en tiempo real basado en FPGA + DSP y de un espacio vectorial con algoritmo de modulación para un convertidor matricial indirecto. Donde la plataforma de control se construye utilizando el DSP. El método propuesto permite un diseño compacto de bajo costo y fácil implementación. En [18] se implementó un sistema híbrido en donde se utilizó un DSP y FPGA para llevar a cabo el control digital de distribución para un TIES, en donde el DSP realiza principalmente los algoritmos de control en cada periodo de muestreo y estos resultados se transmiten a la lógica diseñados en una FPGA a través de un bus de datos y señales de control. Se concluyó que el hardware DSP basado en un FPGA proporciona suficiente capacidad para desarrollar algoritmos de control avanzados, manejar múltiples señales de interfaz y almacenar un gran número de variables. En [5] se presenta una revisión sistemática de tecnología esencial para el desarrollo de transformadores de estado sólido en el sistema de distribución, sobre todo centrándose en las siguientes cuatro áreas: de alto voltaje y la potencia de alta frecuencia, dispositivos de alta potencia y transformadores de 13 alta frecuencia, el convertidor de AC/AC y aplicaciones de transformador de estado sólido en el sistema de distribución. La Electrónica de potencia de estado sólido se está convirtiendo en una de las tecnologías de apoyo más importantes para la transmisión y distribución eléctrica. Sin embargo, puesto que la utilización de convertidores de potencia en la transmisión y distribución es todavía relativamente baja, la red de energía eléctrica sigue siendo una de las próximas grandes fronteras dónde introducir la tecnología de la electrónica de potencia a gran escala. En lo mencionado anteriormente se habló de lo realizado hasta el momento respecto al control distribuido. Lo que ahora se propone es realizar un sistema digital donde se pueda monitorear señales de control en la distribución los TIES, esto se llevara a cabo implementando un FPGA en conjunción con electrónica de potencia. 14 III. JUSTIFICACIÓN En este trabajo se propone un sistema digital de Arquitectura distribuida para el monitoreo un transformador inteligente de estado sólido (TIES). Se optó por tomar este proyecto ya que actualmente se ha dado un incremento en la generación y distribución de energía eléctrica. Con el desarrollo de este proyecto se verán notables beneficios tanto en el consumo de la energía eléctrica como en su distribución, ya que apoyado de un control distribuido se podrá tener un control más eficiente para poder monitorear en qué lugares hay una mayor demanda de energía y así a su vez enviar una alerta al centro de mando para que desde ahí puedan ampliar o reducir el flujo de energía eléctrica según sea el caso. Con los transformadores que actualmente se cuentan en la distribución de energía es como tener la llave abierta debido a que siempre se está generando energía y no se sabe con exactitud si se utiliza o no, generando gastos innecesarios a las plantas generadoras. 15 IV. OBJETIVOS 4.1 Objetivo general El objetivo general de este proyecto es contar con un sistema que permita monitorear y controlar las variables analógicas y digitales del TIES. 4.2 Objetivos específicos - Diseñar y desarrollar un sistema para intercomunicar dispositivos en el TIES; - Analizar el comportamiento del sistema. 16 V. ALCANCE Se propuso un proyecto el cual consiste en realizar un banco para instrumentación de un transformador inteligente de estado sólido con un módulo – SME. Dicho proyecto se dividió en tres etapas las cuales consisten en lo siguiente: Primera etapa: Sistema digital (tarjeta de adquisición de datos). Segunda etapa: Lógica de control (descripción del módulo general). Tercera etapa: Lógica de comunicación (protocolos, expansión de puertos, configuración y adquisición de datos). El presente trabajo está ubicado en la segunda etapa la cual consiste en desarrollar la lógica de control y realizar pruebas de adquisición de señales digitales y analógicas. En esta etapa se realizara principalmente el control general del sistema el cual se llevara a cabo mediante una máquina de estados general que nos permitirá controlar las secuencias de funcionamiento del sistema de adquisición de datos. 17 VI. MATRIZ DE RIESGOS Ri Tipo Probabilidad de ocurrencia Gravedad Estrategia a seguir No aplica [T] Riesgo Identificado Interno-I, Externo-E, Externo Incontrolable-EI, Externo ControlableEC [P] [G] [E] [NA] DESCRIPCI ÓN Bajo desempeño o rendimiento DETONANT E Cargas excesivas de trabajo E C Alta complejidad del proyecto N/A Puro E I Bajo impacto en el mercado Estudio de mercado deficiente Ri 4 Puro E I Bajo impacto político Estudio de marcado/am biental deficiente Ri 5 Punto critico I Actividad no realizada Ri 6 Operativ o E I Herramientas y equipo de pruebas defectuoso Deserción de personal, falta de equipo y/o materiales Fallas de origen Ri 7 Punto critico I Accidentes por mal Distraccione s / no utilizar Id Ri 1 RIESGO Operativ o técnico T I Ri 2 Técnico Ri 3 ANÁLISIS DE RIESGOS Baja-B, Media-M, Alta-A Baja-B, Media-M, Alta-A Aceptarlo-A, Mitigarlo-M, Resolver-R CONSECUENCI AS Demoras en el tiempo de ejecución del proyecto / retraso en objetivos y metas Demoras en el tiempo de ejecución del proyecto / retraso en el objetivos y metas Bajas probabilidades de comercialización Baja probabilidad de integración al mercado P B ACCIONES DE G E CONTROL M M Reasignar actividades de trabajo ACCIONES PREVENTIVA S Repartir equitativament e las actividades de trabajo ACCIONES CORRECTIVAS Liberar al personal de cargas de trabajo RESPONSA BLES DE ASUMIR EL RIESGO Responsable s técnicos M M R Asesoría externa / cursos y capacitación Asesoría externa / cursos y capacitación Asesoría externa / cursos y capacitación Responsable s técnicos B A R Responsable s técnicos A R Reforzar estudio de mercado y ambiental Responsable s técnicos Afectación al desarrollo del proyecto B A R Realizar extenso estudio de mercado Realizar una extenso en el estudio de marcado y ambiental Integrar personal con alto sentido de compromiso Reforzar estudio de marcado B Reemplazar personal Responsable s técnicos Demoras en el tiempo de ejecución del proyecto B B R Revisar constantement e el estado del equipo y herramientas Reemplazo inmediato del equipo y herramienta defectuoso Responsable s técnicos / LICORE Daños en equipos y M A R Realizar una extensión de estudio de mercado Realizar una extenso en el estudio de marcado y ambiental Integrar personal extra en cada actividad Comprar equipo y herramienta s faltantes / hacer valida la garantía Controles de acceso solo Contar con equipos de Contar con acceso a Responsable s técnicos 18 diseño o mal uso de sistemas y herramientas Estudio técnico deficiente el equipo de seguridad sistemas Personal no calificado Desarrollo deficiente B A para personal autorizado seguridad y capacitaciones telefónico a centros de apoyo R Extender estudio Rehacer Responsable s técnicos R Extender estudio Realizar juntas de seguimiento y de control Realizar juntas de seguimiento y de control Rehacer Responsable s técnicos / LICORE Juntas de seguimiento y control Integrar personal extra al proyecto Responsable s técnicos Ri 8 Técnico I Ri 8 Económi co financier o I Estudio de mercado deficiente Personal no calificado Bajo impacto político B A Ri 9 Operativ os I Retraso en el cronograma de actividades Falta de equipo o materiales / deserción de personal / complejidad del proyecto Aumento en el costo del proyecto B M R 19 Juntas de seguimiento y control VII. FUNDAMENTACIÓN TEÓRICA 7.1 Control distribuido El sistema de control distribuido (DCS) ha sido desarrollado para resolver la adquisición de grandes volúmenes de información, su tratamiento en centros de supervisión y mando y la actuación en tiempo real sobre un proceso a controlar. El sistema está especialmente recomendado para llevar a cabo la supervisión en el control de mando de diferentes TIES, permitiendo a los usuarios disponer de una información procedente de distintos puntos del proceso. A su vez, este sistema dispone de módulos de software para la resolución de problemas específicos dentro de los TIES, como pueden ser el cálculo de rendimientos, cálculo de consumos o el módulo de mantenimiento [19]. Para llevar a cabo un buen control distribuido es necesario contar con sistemas embebidos los cuales nos permitirán un mejor desempeño en todos los módulos que conforman el control. 7.2 Sistemas embebidos Se entiende por sistemas embebidos a una combinación de hardware y software de computadora, o de otro tipo, diseñado para tener una función específica. Es común el uso de estos dispositivos pero pocos se dan cuenta que hay un procesador y un programa ejecutándose que les permite funcionar. 20 Esta combinación de software y hardware puede ser reemplazada en muchos casos por un circuito integrado que realice la misma tarea. Pero una de las ventajas de los sistemas embebidos es su flexibilidad. Ya que a la hora de realizar alguna modificación resulta mucho más sencillo modificar una línea de código al software del sistema embebido que reemplazar todo el circuito integrado. Un uso muy común de los sistemas embebidos es en los sistemas de tiempo real, entendiéndose por sistemas en tiempo real a aquellos sistemas en los que el control del tiempo es vital para el correcto funcionamiento. Los sistemas en tiempo real necesitan realizar ciertas operaciones o cálculos en un límite de tiempo. Donde ese límite de tiempo resulta crucial [20]. 7.3 Estructura de un sistema embebido Las principales características de un sistema embebido son el bajo costo y consumo de potencia. Generalmente, los sistemas embebidos emplean procesadores muy básicos, relativamente lentos y memorias pequeñas para minimizar los costos. En estos sistemas la velocidad no solo está dada por la velocidad del reloj del procesador, sino que el total de la arquitectura se simplifica con el fin de reducir costos. Normalmente, un sistema embebido 21 emplea periféricos controlados por interfaces seriales síncronos, las cuales son muchas veces más lentas que los periféricos empleados en una PC. Los sistemas embebidos deberán reaccionar a estímulos provenientes del ambiente, respondiendo con fuertes restricciones de tiempo en muchos casos, por lo tanto, un sistema se dice que trabaja en tiempo real si la información después de la adquisición y tratamiento es todavía vigente. Es decir, que en el caso de una información que llega de forma periódica, los tiempos de adquisición y tratamiento deben ser inferiores al período de actualización de dicha información. Un sistema embebido puede o no ser de tiempo real dependiendo de los requerimientos específicos de la aplicación que se quiere implementar [20]. 7.4 Componentes de un sistema embebido Un sistema embebido en principio estaría formando por un microprocesador y un software que se ejecute sobre este. Sin embargo este software necesitara sin duda un lugar donde poder guardarse para luego ser ejecutado por el procesador. Esto podría tomar la forma de memoria RAM o ROM, todo sistema embebido necesitara en alguna medida una cierta cantidad de memoria, la cual puede incluso encontrarse dentro del mismo chip del procesador [20]. 22 7.5 Elementos principales del proyecto Los principales elementos que se integraron para el desarrollo de este proyecto son el FPGA DE0-NANO de Altera, Nios II y Avalon Interface mediante una comunicación inalámbrica con el dispositivo Xbee. 7.5.1 DE0-Nano La tarjeta DE0-Nano introduce una gama de tamaño compacto de desarrollo FPGA. Es ideal para su uso con los soft processors embebidos. Sus características principales se mencionan a continuación: Característica de dispositivo Altera Cyclone® IV EP4CE22F17C6N FPGA 153 maximum FPGA I/O pins Estado de la configuración y elementos de configuración Circuito a bordo USB-Blaster para la programación Dispositivo de configuración serie Altera - EPCS16 Encabezado de expansión 23 Dos Cabezales de 40 pines (GPIO) proporcionan 72 I/O, pines de alimentación de 5V, dos pines de alimentación de 3,3 V y cuatro pines de tierra Los dispositivos de memoria 32 MB SDRAM 2Kb I2C EEPROM Entrada del usuario general / salida 8 LEDs verdes 2 pulsadores sin rebote Interruptor DIP de 4 posiciones G-Sensor ADI ADXL345, acelerómetro de 3 ejes con alta resolución (13-bit) Convertidor A / D NS ADC128S022, 8 canales, 12 bits Un convertidor 50 Ksps a 200 Ksps Sistema de reloj A bordo oscilador de reloj 50 MHz 24 Fuente de alimentación USB Tipo de puerto mini-AB (5V) Pin DC 5V para cada encabezado GPIO (2 DC 5V pins) Cabezal de alimentación externa de 2 pines (3,6-5.7V) Incluye un conector USB integrado para la programación de FPGA y la tarjeta se puede alimentar desde este puerto USB o mediante una fuente de alimentación externa. La tarjeta incluye conectores de expansión que se pueden utilizar para conectar varias tarjetas esclavo terasic u otros dispositivos, tales como motores y actuadores. Entradas y salidas incluye 2 pulsadores, 8 indicadores leds y un conjunto de 4 conmutadores DIP [21]. Figura. 7.5.1 Tarjeta DE0-NANO. 7.5.2 Nios II 25 Un sistema soft processor Nios II es equivalente a un microcontrolador que incluye un procesador y una combinación de periféricos y de memoria en un solo dispositivo. Un soft processor Nios II consiste en un núcleo de procesador Nios II, un conjunto de periféricos en chip, la memoria en el chip y las interfaces de memoria fuera del chip, todo implementado en un solo dispositivo de Altera. Como una familia de microcontroladores, todos los sistemas de procesador Nios II usan un sistema de instrucción consistente y modelo de programación [22]. Figura. 7.5.2.1 Diagrama de bloques del Procesador Nios II Core. 7.5.3 Avalon Interface 26 Avalon interface simplifica el diseño del sistema, ya que permite conectar fácilmente componentes en una FPGA Altera. La familia interfaz Avalon define interfaces apropiadas para la transmisión de datos de alta velocidad, leer y escribir registros y la memoria y el control de dispositivos off-chip. Estas interfaces estándar están diseñadas en los componentes disponibles en el software QSYS de altera. También puede utilizar estas interfaces estandarizadas en sus componentes personalizados. Mediante el uso de estas interfaces estándar, se puede mejorar la interoperabilidad de sus diseños [24]. A continuación se presenta un ejemplo gráfico de Avalon Interface en un diseño de sistema con Scatter Gather controlador DMA y procesador Nios II 27 Figura. 7.5.3.1 Aplicación típica Avalon Interface. 28 VIII. PLAN DE ACTIVIDADES Para el desarrollo del proyecto fue necesario desglosarlo en algunas etapas las cuales se fueron desarrollando en serie debido a que para continuar con el proceso primero se tenía que concluir la primera y posteriormente otras se pudieron realizar en paralelo. 8.1 Evaluación de requerimientos En esta primera etapa se realizaron diversas investigaciones en papers con antecedentes relacionados al control distribuido de la energía eléctrica, esto se realizó con el fin de profundizar en los trabajos ya existentes y así de esta manera poder dar una nueva propuesta. 8.2 Diseño y desarrollo Para esta etapa fue necesario realizar el diseño e implementación de un par de tarjetas las cuales servirán para realizar múltiples pruebas del sistema de control, todo esto con el fin de garantizar un sistema funcional. 8.3 Adquisiciones En este apartado se implementaron las tarjetas de adquisición de datos para adquirir los datos desde una fuente de alimentación y algunos sensores de humedad. 29 8.4 Pruebas Para verificar un correcto funcionamiento del sistema se realizaron pruebas con un emulador el cual sustituye el funcionamiento de un ADC. 8.5 Reporte final Después de concluidas todas las etapas se prosigue a realizar un documento en donde se reporten todos los sucesos y actividades realizadas durante el desarrollo del proyecto. Figura. 8.5.1 Diagrama de Gantt de Actividades de trabajo. 30 IX. RECURSOS MATERIALES Y HUMANOS Para el desarrollo e implementación del proyecto ya mencionado se necesitó de los siguientes materiales: Material DE0-Nano Spartan 3 - Xilinx Tarjeta SAD ADC/DAC Tarjeta SAD Sensores Avalon interface Dispositivo XBee Cantidad 1 1 1 1 1 1 Como el proyecto fue dividido en tres etapas, fueron tres personas las encargadas de su desarrollo, estas personas son: Recurso Humano Guadalupe Higinia Serna López Responsabilidad Desarrollo de la tarjeta del sistema de adquisición de datos. Luis Alberto Guerrero Montes Desarrollo de la lógica de control del sistema. Emmanuel Trejo Espinosa Desarrollo de la lógica de comunicación. 31 X. DESARROLLO DEL PROYECTO Hablando en términos generales este proyecto se encuentra enfocado a la generación, transmisión y distribución de energía eléctrica. Debido a que para hablar en general de la energía eléctrica es un tema muy amplio, se llevara hasta lo más particular que en este caso es el área de distribución donde se enfocara el desarrollo del proyecto. Así mismo el control distribuido está dividido en tres estapas las cuales se muestran en la siguiente figura. Figura. 10.1 Esquema general del proyecto. El presente proyecto está ubicado en una etapa en donde se realizará la lógica de control y para lo cual se propuso un sistema de control distribuido aplicado a sistemas embebidos en FPGA. En este caso está basado en los siguientes componentes: PC AVALON INTERFACE 32 DRIVERS FPGA RS232 READ FSM LATCH LARCH’S RAM CONTADOR TIMER ADC/DAC DEMULTIPLEXOR FSM CONTROL RS232 WRITE NIOS II XBee A continuación se menciona una descripción de cada uno de los módulos y componentes que conforman la lógica general de control. 10.1 Pc Es la computadora que se estará utilizando en el sistema para realizar el enlace y mando, la cual estará a cargo de Avalon interface. 33 10.2 Avalon interface Avalon es una interfaz de comunicación creada por ALTERA. Simplifica el diseño del sistema, ya que permite conectar fácilmente componentes en una FPGA de Altera. La familia interfaz Avalon define interfaces apropiadas para la transmisión de datos de alta velocidad, leer y escribir registros, memoria y el control de dispositivos off-chip. Estas interfaces estándar están diseñadas en los componentes disponibles en QSYS. QSYS es una herramienta de integración de sistemas que ahorra mucho tiempo y esfuerzo en el proceso de diseño de FPGA generando automáticamente la lógica de interconexión para conectar la propiedad intelectual y las funciones de los subsistemas (IP). QSYS es la próxima generación de herramientas impulsado por una nueva tecnología FPGA [21]. 34 Figura. 10.2.1 Aplicación típica de Avalon Interface 10.3 Drivers Son las descripciones diseñadas en el FPGA para tener un control de cada uno de los componentes utilizados para llevar a cabo la lógica de control. 10.4 Fpga Es el chip que contiene bloques de lógica cuya interconexión y funcionalidad puede ser configurada mediante le lenguaje VHDL. Tiene la ventaja de ser reprogramable (lo que añade una enorme flexibilidad al flujo de diseño), sus costos de desarrollo y adquisición son mucho menores para pequeñas 35 cantidades de dispositivos y el tiempo de desarrollo es también menor. Es en este dispositivo en donde se implementaran las descripciones de la lógica de control. 10.5 RS232 Read/Write Es un puerto serial, como su nombre lo indica envía su información de manera serial, es decir, como un tren de pulsos, utilizando el protocolo RS-232. Para el envío de información es necesario que tanto el emisor como el receptor estén configurados para trabajar a la misma tasa de transferencia, ya que la comunicación es asíncrona y la señal de reloj no es enviada con la información. Para lograr la sincronización el puerto utiliza un protocolo el cual envía un bit de partida, el cual no es configurable. Lo que sí es configurable es el bit de parada, la paridad y el número de bits. La configuración más utilizada es la 8N1 (8 bits de información, sin paridad y 1 bit de parada). En las comunicaciones asíncronas el estado de reposo (cuando no se transmite nada) se identifica con un "1" (marca). Cuando se recibe un bit de inicio, que es un "0" (espacio), el receptor toma nota que va a comenzar a recibir un dato. Se utilizó una velocidad 9600 Baudios. Baudio se define como el número de veces que cambia la portadora en un segundo. 36 Estos dos módulos fueron utilizados para para realizar la comunicación con el sistema el RS232-RD fue utilizado para llevar a cabo la lectura de datos a la entrada del sistema en donde se va a realizar todo el proceso, mientras que el módulo RS232-WR fue utilizado para que una vez que se hayan tomado y analizado las señales analógicas y digitales estas sean escritas o capturadas a un archivo generado por Math lab. Figura. 10.5.1 Protocolo RS232. 10.6 Fsm latch Es una máquina de estados en la que se lleva a cabo la expansión de puertos para que sea acondicionada al tamaño de bits requeridos para el contador y un timer, que en este caso fueron de 10 bits y 26 bits respectivamente. 37 10.7 Latch’s Es un circuito diseñado en una descripción de FPGA y que se utiliza para almacenar información de sistemas lógicos asíncronos, en este caso son de 10 y 26 bits. Figura. 10.7.1 Diagrama de máquina de estados de la expansión de bits (latch). 38 10.8 Ram Es una memoria de acceso aleatorio o RAM (acrónimo del inglés Ramdon Access Memorry) y que consiste en un conjunto de registros los cuales pueden accederse en forma arbitraria por el usuario y sirve para almacenar datos en forma temporal conforme se desarrolla un proceso determinado [22]. En este caso fue implementada para que almacenara los datos obtenidos del sistema de adquisición de datos y posteriormente enviarlos a un multiplexor en cual se encarga de enviar los datos de 8 en 8 bits, el multiplexor es implementado debido al que le RS232 no puede recibir los 12 bits que salen de la RAM, se implementó el multiplexor como intermediario quien es el encargado de enviarnos los 16 bits pero de 8 en 8, de donde los segundos 8 bits solo se envían los 4 más significativos para complementar los 12 bits reales del sistema de adquisición de datos, pero para complementar los 8 bits y se le concatenan 8 ceros. 10.9 Contador Es un tipo de máquina secuencial muy simple que permite dar una secuencia preestablecida, con la condición de ser consecutiva [22]. Es el encargado de indicar cuantas veces se requiere de una señal, este es controlado a su vez por el timer quien esta preestablecido con un determinado 39 tiempo, esto se lleva a cabo en la etapa de adquisición. En el envió de información se encarga de darnos la cantidad específica de datos requeridos. 10.10 Timer Lleva el control de tiempo, nos indica en que momento tomar una señal requerida. 10.11 Adc/Dac Es una tarjeta que se desarrolló para fines de prueba en la adquisición de señales y en la que se implementó de ADC ADS7886 y el DAC TLV5636. Para esta tarjeta se desarrollaron sus respectivos drivers en descripción de VHDL. 10.12 Multiplexor Este circuito nos permite el paso selectivo de dos señales de 8 bits cada una provenientes de la RAM y las manda al RS232 de escritura. Debido a que la escritura en el RS232 solo nos admite hasta 8 bits se optó por utilizar este circuito. 10.13 Fsm control Es una máquina de estados general. Esta lleva a cabo el control de todo el sistema, es decir controla todos los componentes que conforman al sistema, 40 indicando en que momento se deben de tomar las señales y así mismo indicando en que momento se han terminado de enviar los datos. Figura. 10.13.1 Diagrama de máquina de estados de control. 41 10.14 Nios II Es el procesador que ofrece la compañía Altera para ser usado en sus FPGA’S de las familias Stratix y Cyclone. Es un procesador RISC de 32 bits con arquitectura Harvard. [23] Sus principales características son: El procesador Nios II es un RISC de propósito general con las siguientes características: Conjunto completo de instrucciones de 32 bits, ruta de datos y espacio de direcciones. 32 registros de propósito general. Conjuntos de registros sombra opcionales. 32 fuentes de interrupción. Interfaz de controlador de interrupciones externas para más fuentes de interrupción. Única instrucción de 32 × 32 multiplicar y dividir la producción de un resultado de 32 bits. Instrucciones dedicadas para computación de 64 bits y 128 bits. 42 Instrucciones de coma flotante para operaciones de punto flotante de precisión simple. Única instrucción barril shifter. Acceso a una variedad de periféricos en chip, y las interfaces con los recuerdos off-chip y periféricos. Módulo de depuración asistida por hardware que permite inicio procesador, parada, paso, y traza bajo el control de las herramientas de desarrollo de software Nios II. Unidad de gestión de memoria opcional (MMU) para apoyar los sistemas operativos que requiriere. Unidad de protección de memoria opcional (MPU). Integración con SignalTap II Embedded Analizador lógico de Altera, lo que permite análisis en tiempo real de las instrucciones y de datos, junto con otras señales en la FPGA. Arquitectura del conjunto de instrucciones (ISA) compatibles con todos los sistemas de procesador Nios II. Rendimiento hasta 250 DMIPS. 43 El NIOS II es una familia de procesador integrado versátil que ofrece un alto rendimiento y se ha creado para FPGA. Propicia la flexibilidad en la aplicación del sistema de un procesador como tal: puede elegir el conjunto exacto de CPU, periféricos e interfaces necesarias para la aplicación, aumenta el rendimiento sin necesidad de cambiar el diseño de la tarjeta, acelera las únicas funciones que lo requiera, elimina el riesgo de procesador de obsolescencia, tiene un menor costo total y la complejidad, el consumo de energía y la combinación de muchas funciones en un solo chip [6]. 10.15 XBee El XBee fue diseñado para cumplir con los estándares IEEE 802.15.4 y el único en apoyar con necesidades de bajo costo, bajo consumo de energía de redes de sensores inalámbricos. Este módulo requiere un mínimo de energía y proporciona fiable entrega de datos entre dispositivos. El módulo opera en una frecuencia de 2,4 GHz [25]. Figura. 10.15.1 Dispositivo inalámbrico XBee. 44 10.16 Pruebas Durante el desarrollo del proyecto se realizaron diversas pruebas del sistema con las tarjetas del ADC/DAC y Spartan 3. Estas pruebas fueron realizadas con el fin de tener un sistema funcional y evitar futuros errores. Una vez que se obtuvo toda la lógica de control con sus respectivos módulos se implementó una prueba con un emulador. Este emulador es un equivalente al ADC/DAC se optó por realizar esta prueba para verificar que el sistema estuviera funcionando correctamente ya que en este emulador se incluye una memoria ROM la cual nos almacena valores preestablecidos y posteriormente son los que nos debe arrojar finalmente en la escritura del RS232 y enviarla a Math Lab. 45 Figura. 10.16.1 Pruebas con el SAD. Una vez finalizada esta prueba y comprobando que el sistema funciona adecuadamente se reincorporo el modulo correspondiente al ADC/DAC para realizar las pruebas físicas con señales reales quienes fueron adquiridas desde una fuente de alimentación. 46 Figura. 10.16.2 Esquemático del SAD con ADC/DAC. Al finalizar la etapa de pruebas se prosiguió a implementar el sistema pero ahora implementándolo con la tarjeta DE0-Nano de altera quien a su vez ya incluye un convertidor A/D ADC128S022, 8 canales y 12 bits. La comunicación de esta tarjeta ahora será de manera inalámbrica para lo cual se utilizó el 47 dispositivo XBee. La DE0-Nano obtendrá los datos de un SAD el cual fue diseñado en el software Altium Designer. 48 XI. RESULTADOS OBTENIDOS La figura La figura 11.1 muestra una fotografía de la tarjeta de control principal. Consiste principalmente de la tarjeta de adquisición de datos, el FPGA DE0NANO de Altera y un dispositivo XBee. La placa de control está diseñada para hacer conexiones entre los dispositivos XBee y el FPGA, ambos pueden ser retirados e incorporados de manera independiente sin haber la necesidad de ser soldados directamente a la tarjeta. Este enfoque nos permite grandes ventajas tal como evitar un desperdicio general, es decir en caso de dañarse algún elemento o dispositivo se cambiará únicamente dicho dispositivo dañado y no todo el conjunto de la tarjeta. 49 Figura 11.1 Sistema de control completo. 50 XII. CONCLUSIONES En este trabajo se presenta una arquitectura de control digital distribuido de los TIES mediante el uso de un FPGA. La plataforma de control que se desarrolló permitirá la ejecución de un FPGA para la programación de la totalidad de algoritmos de control, aumentando así la tasa de procesamiento. Con el fin de controlar el TIES, es necesario lograr una distribución óptima en la tarea de mejorar el control de rendimiento del sistema. Por lo tanto, el hardware basado en FPGA proporciona suficiente capacidad para desarrollar los algoritmos de control avanzados, manejar múltiples señales de interfaz y almacenar un gran número de variables del TIES. Una ventaja que podemos obtener de este sistema es que el tiempo de desarrollo para la aplicación de algoritmos complejos e interfaces de hardware pueden reducirse significativamente. El uso de la FPGA en conjunto con Avalon Interface hace un poderoso sistema embebido el cual nos permite tener un mejor control del sistema y mejor aún lo podemos monitorear inalámbricamente mediante el dispositivo XBee. El rendimiento, la utilización y el intercambio de información pueden aumentar mediante esta aplicación. 51 XIII. ANEXOS 52 ANEXO I library IEEE; use IEEE.std_logic_1164.all; use IEEE.std_logic_arith.all; use IEEE.std_logic_unsigned.all; entity complejo is port( rst: in std_logic; clk: in std_logic; NBaud: in std_logic_vector (3 downto 0); Rx: in std_logic; SDR: in std_logic; SDO: in std_logic; DWR: in std_logic_vector (11 downto 0); DIN: out std_logic; RYW: out std_logic; FS: out std_logic; CS: out std_logic; SCLK1: out std_logic; SCLK2: out std_logic; Tx: out std_logic ); end complejo; architecture total of complejo is component RS232RD is port( RST : CLK : Rx : NBaud : Data : out EOR : ); end component; in std_logic; in std_logic; in std_logic; in std_logic_vector(3 downto 0); std_logic_vector(7 downto 0); out std_logic component FSM_latch is port ( clk: in std_logic; rst: in std_logic; RYR: in std_logic; RDY: in std_logic; 53 LD : out std_logic_vector (5 downto 0); SMP: out std_logic ); end component; component Latch1 is port( RST : in std_logic; -- Master Reset CLK : in std_logic; -- Master Clock LD : in std_logic; -- Load: 0= Hold 1= Load DTR : in std_logic_vector (7 downto 0); -- Input Data SPE : out std_logic_vector (7 downto 0) -- Output Data ); end component; component Latch2 is port( RST : in std_logic; -- Master Reset CLK : in std_logic; -- Master Clock LD : in std_logic; -- Load: 0= Hold 1= Load DTR : in std_logic_vector (7 downto 0); -- Input Data SPE : out std_logic_vector (7 downto 0) -- Output Data ); end component; component Latch3 is port( RST : in std_logic; -- Master Reset CLK : in std_logic; -- Master Clock LD : in std_logic; -- Load: 0= Hold 1= Load DTR : in std_logic_vector (7 downto 0); -- Input Data SPE : out std_logic_vector (7 downto 0) -- Output Data ); end component; component Latch4 is port( RST : in std_logic; -- Master Reset CLK : in std_logic; -- Master Clock LD : in std_logic; -- Load: 0= Hold 1= Load DTR : in std_logic_vector (7 downto 0); -- Input Data SPE : out std_logic_vector (7 downto 0) -- Output Data ); end component; 54 component Latch5 is port( RST : in std_logic; -- Master Reset CLK : in std_logic; -- Master Clock LD : in std_logic; -- Load: 0= Hold 1= Load DTR : in std_logic_vector (7 downto 0); -- Input Data SPE : out std_logic_vector (7 downto 0) -- Output Data ); end component; component Latch6 is port( RST : in std_logic; -- Master Reset CLK : in std_logic; -- Master Clock LD : in std_logic; -- Load: 0= Hold 1= Load DTR : in std_logic_vector (7 downto 0); -- Input Data SPE : out std_logic_vector (7 downto 0) -- Output Data ); end component; component count_fijo is generic (n: integer :=10); port ( clk: in std_logic; rst: in std_logic; K: in std_logic_vector (n-1 downto 0); OPC: in std_logic_vector (1 downto 0); eoc: out std_logic_vector (n-1 downto 0); fin : out std_logic ); end component; component TIMER is port( RST : CLK : ENA : OPC : FREC : in TP : out Base frequency ); end component; in std_logic; in std_logic; in std_logic; in std_logic_vector (1 downto 0); std_logic_vector(25 downto 0); -- Bauds by second std_logic -- 55 component RAM is generic( m: integer:= 12; -- No. de bits n: integer:= 10; -- Lineas de dirección k: integer:= 1024 -- No. de localidades ); port( CLK : in std_logic; -- Master clock AE : in std_logic_vector(n-1 downto 0); -- Dirección de escritura AS : in std_logic_vector(n-1 downto 0); -- Dirección de lectura WE : in std_logic; -- Escritura DE : in std_logic_vector(m-1 downto 0); -- Dato de entrada DS : out std_logic_vector(m-1 downto 0) -- Dato de entrada ); end component; component ADC_DAC is port( RST : in std_logic; CLK : in std_logic; SRD : in std_logic; SDO : in std_logic; DWR : IN STD_logic_VECTOR(11 DOWNTO 0); SWR : IN STD_logic; DIN : OUT STD_logic; RYW : OUT STD_logic; FS : OUT STD_logic; CS : out std_logic; SCLK1: out std_logic; SCLK2: OUT STD_logic; RYR : out std_logic; DRD : out std_logic_vector(11 downto 0) ); end component; component Mux_2_1 is port ( E1 : in std_logic_vector (7 downto 0); E2 : in std_logic_vector (7 downto 0); S : in std_logic; Y : out std_logic_vector (7 downto 0) 56 ); end component; component Master is port ( rst: in std_logic; clk: in std_logic; eocc: in std_logic; eoct: in std_logic; smp: in std_logic; rd_dac: in std_logic; rd_wr: in std_logic; ent: out std_logic; sta_dr: out std_logic; opcc: out std_logic_vector (1 downto 0); opct: out std_logic_vector (1 downto 0); str2: out std_logic; sel: out std_logic; wer: out std_logic; rdy: out std_logic ); end component; component RS232WR is port( RST : CLK : STR : DATAWR : NBaud : Tx : EOT : ); end component; in std_logic; in std_logic; in std_logic; in std_logic_vector(7 downto 0); in std_logic_vector(3 downto 0); out std_logic; out std_logic signal data: std_logic_vector (7 downto 0); signal red1, fn_fsm, smp1: std_logic; signal LD1: std_logic_vector (5 downto 0); signal contador: std_logic_vector (9 downto 0); signal conta, conta1: std_logic_vector ( 7 downto 0); signal tim, timer1, timer2, timer3: std_logic_vector (7 downto 0); signal OPC1, OPC2: std_logic_vector (1 downto 0); signal eoc1, Tp1, sel, fin2,rdw, ena1,stawr: std_logic; signal eor1: std_logic_vector (9 downto 0); 57 signal we1,sta1: std_logic; signal de1,ds1: std_logic_vector (11 downto 0); signal dataout: std_logic_vector (7 downto 0); signal ds2: std_logic_vector (15 downto 0); signal tim1: std_logic_vector (25 downto 0); begin OP1: RS232RD port map (rst, clk, Rx, NBaud, data, red1); Op2: FSM_latch port map (clk, rst, red1, fn_fsm, LD1, smp1); Op3: Latch1 port map (rst, clk, LD1(0), data, conta); Op4: Latch2 port map (rst, clk, LD1(1), data, conta1); Op5: Latch3 port map (rst, clk, LD1(2), data, tim); Op6: Latch4 port map (rst, clk, LD1(3), data, timer1); Op7: Latch5 port map (rst, clk, LD1(4), data, timer2); Op8: Latch6 port map (rst, clk, LD1(5), data, timer3); contador<= conta&conta1(1 downto 0); tim1<= tim&timer1&timer2&timer3(1 downto 0); Op9: count_fijo port map (clk, rst, contador, OPC1, eor1, eoc1); Op10: TIMER port map (rst, clk, ena1, OPC2, tim1, Tp1); Op11: RAM port map (clk, eor1, eor1, we1, de1, ds1); Op12: ADC_DAC port map (rst, clk, SDR, SDO, DWR, sta1, DIN, RYW, FS, CS, SCLK1, SCLK2, fin2, de1); Op13: Mux_2_1 port map (ds2(15 downto 8), ds2(7 downto 0), sel, dataout); ds2<="0000"&ds1; Op14: Master port map (rst, clk, eoc1, Tp1 , smp1, fin2, rdw, ena1, sta1, OPC1, OPC2, stawr, sel, we1, fn_fsm); Op15: RS232WR port map (rst, clk, stawr, dataout, NBaud, Tx, rdw); end total; 58 XIV. BIBLIOGRAFÍA [1] J.H.Harlow, Electric power transformer engineering. Boca Raton: CRCpress, 2007. [2] M. McGranaghan, D. Von Dollen, P. Myrda, and E. Gunther, “Utility experience with developing a smart grid roadmap,” in Proc. IEEE PES Gen. Meet. 2008, pp. 1–5. [3] EPRI Intelligrid [en línea]. Disponible: http://intelligrid.epri.com/. [4] Johann W. Kolar, “Intelligent Solid State Transformers (SSTs): A key Building Block of Future Smart Grid Systems”, Swiss Federal Institute of Technology (ETH) in Zurich, Power Electronic Systems Laboratory, [en línea]. Disponible: www.pes.ee.ethz.ch. [5] Xu She, Rolando Burgos, Gangyao Wang1, Fei Wang, Alex Q.Huang, “Review of Solid State Transformer in the Distribution System: From Components to Field Application”, Energy Conversion Congress and Exposition (ECCE), 2012 IEEE, pp. 4077 – 4084, 15-20 Sept. 2012. [6] André Luis Pesco Alcalde, Márcio Silveira Ortmann, Samir Ahmad Mussa, “NIOS II Processor Implemented in FPGA: An Application on Control of a PFC Converter”, Power Electronics Specialists Conference, 2008. PESC 2008. IEEE, pp. 4446 – 4451, June 2008. 59 [7] André L. P. Alcalde, Hari B. Mohr, Deivis Borgonovo, Samir A. Mussa, “EXPERIMENTAL VALIDATION OF THE NIOS II PROCESSOR-FPGA ON THEDIGITAL CONTROL OF PFC CONVERTER”, Power Electronics Conference, 2009. COBEP '09. Brazilian, pp. 895 – 900, Oct. 2009. [8] Emilio J. Bueno, Álvaro Hernández, Francisco J. Rodríguez, Carlos Girón, Raúl Mateos, and Santiago Cóbreces, “A DSP and FPGA-Based Industrial Control With High-Speed Communication Interfaces for Grid Converters Applied to Distributed Power Generation Systems”, Industrial Electronics, IEEE Transactions on (Volume:56 , Issue: 3 ), pp. 654 – 669, March 2009. [9] Rafael Ramos, Domingo Biel, Francesc Guinjoan, Enric Fossas, “Distributed Control Strategy for Parallel-Connected Inverters. Sliding Mode Control Approach and FPGA-Based Implementation”, IECON 02 [Industrial Electronics Society, IEEE 2002 28th Annual Conference of the] (Volume:1 ), pp. 111 – 116, Nov. 2002. [10] Wataru Fujii, Tomoki Yokoyama, “Construction of FPGA Based Hardware Controller for Autonomous Decentralized Control for UPS Application”, Power Electronics and Motion Control Conference, 2006. EPE-PEMC 2006. 12th International, pp. 846 – 851, Sept. 2006. [11] Tevhid Atalik, Mustafa Deniz, Erkan Koç, Cem Özgur Gerçek, Burhan Gültekin, Muammer Ermis¸ Isik Çadirci, “Multi-DSP and -FPGA-Based Fully 60 Digital Control System for Cascaded Multilevel Converters Used in FACTS Applications”, IEEE, pp. 511 – 526, August 2012. [12] Shin-Ju Chen, Sung-Pei Yang, Ruei-Hong Wong, “FPGA-Based Digital Control for Boost Converters with Power Factor Correction”,Industrial Electronics and Applications (ICIEA), 2012 7th IEEE Conference on , pp. 1102 – 1106, July 2012. [13] Miguel Rodr´ıguez, Greg Stahl, Luca Corradini, Dragan Maksimovi´c, “Smart DC Power Management System Based on Software-Configurable Power Modules”, Power Electronics, IEEE Transactions on (Volume:28 , Issue: 4 ), pp. 1571 – 1586, April 2013. [14] Andriy Palamar, Mykola Karpinskyy, Valery Vodovozov, “Design and Implementation of a Digital Control and Monitoring System for an AC/DC UPS”, Compatibility and Power Electronics (CPE), 2011 7th International ConferenceWorkshop, pp.173 – 177, June 2011. [15] Pedro Martín Sanchez, Osmell Machado, Emilio J. Bueno Peña, Francisco J. Rodríguez, Francisco Javier Meca, “FPGA-Based Implementation of a Predictive Current Controller for Power Converters”, Industrial Informatics, IEEE Transactions on (Volume:9 , Issue: 3 ), pp. 1312 – 1321, Aug. 2013. 61 [16] Óscar Lucía, Isidro Urriza, Luis. A. Barragán, Denis Navarro,Óscar Jiménez, José M. Burdío, “Real-Time FPGA-Based Hardware-in-the-Loop Simulation Test Bench Applied to Multiple-Output Power Converters”, Applied Power Electronics Conference and Exposition (APEC), 2010 Twenty-Fifth Annual IEEE , pp. 309 – 314, Feb. 2010. [17] Mahmoud Hamouda, Handy Fortin Blanchette, Kamal Al-Haddad, Farhat Fnaiech, “An Efficient DSP-FPGA-Based Real-Time Implementation Method of SVM Algorithms for an Indirect Matrix Converter”, Industrial Electronics, IEEE Transactions on (Volume: 58, Issue: 11 ), pp. 5024 – 5031, Nov. 2011. [18] S. Hwan Hwang, “Distributed Digital Control of Modular-Based Solid-State Transformer Using DSP+FPGA”, Industrial Electronics, IEEE Transactions on (Volume: 60, Issue: 2 ), pp. 670 – 680, Feb. 2013. [19] Pablo Castillo Rubio, “La estructura de un control distribuido”, [en línea] Disponible: http://www.slideshare.net/ptah_enki/sistemas-de-control- distribuidos. [20] Antonio Nadal Galiana Llinares, “Sistemas Embebidos”, pp. 1 – 30. [21] User Manual “DE0-NANO”. [22] Manual de “Nios II Processor Reference”, Altera. 62 [23] R. de J. Romero-Troncoso, Electrónica Digital y Lógica Programable, Ed. Universidad de Gto, México, 2007. [24] Manual de “Avalon interface specifications”, Altera, 2013. [25] Hoja de datos “XBee”, Modules by Digi International, 2009. 63