ModosDireccionamiento6800 639KB Feb 20 2014 06:55:16 PM

Anuncio

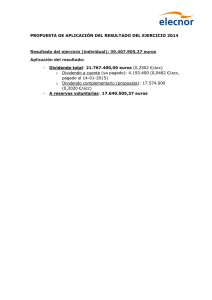

MODOS DE DIRECCIONAMIENTO µP MOTOROLA 6800 Autor: Ing. Julio César Doumecq - @ 2008-2012 Estructura básica de una computadora Estructura interna del µP Motorola 6800 R Descripción de los Registros La ALU (Arithmetic and Logic Unit) puede efectuar operaciones aritméticas y lógicas tales como: • Suma, Resta, Incremento_en_1, Decremento_en_1, Puesta_a_0, Puesta_a_1, Comparación, Rotación, Desplazamiento, AND_lógica, OR_lógica, OR_exclusiva, Complemento_a_1, Complemento_a_2, etc. • Esta unidad procesa 8 bits en paralelo y opera conjuntamente con dos acumuladores (A y B) vía el bus bidireccional de datos/instrucciones también de 8 líneas. • Asociado a ella se encuentra un registro de estados “Code Condition Register" (CCR) o “Registro de Códigos de Condición” de 8 bits llamados "flags" o banderas. • El sentido de cada flag se indica a continuación: El Registro de Códigos de Condición (CCR) b7 b6 b5 b4 b3 b2 b1 b0 1 1 H I N Z V C H : (Half) medio acarreo. Se pone en 1 si en la operación efectuada se produjo un transporte del primer al 2°nibble (bit 3 al bit 4). l : Máscara de interrupciones. Se pone en 1 cuando se está atendiendo una interrupción o si se desea inhibir las "interrupciones enmascarables" que se verán algo más adelante. N : Negativo. Bit de signo. Se pone en 1 si la operación efectuada da resultado negativo. (8°bit del resultado = 1). Z : (Zero) bit de cero. Se pone en 1 si el resultado de la última operación efectuada es cero. V : (overflow) bit de desborde. Se pone en 1 si como resultado de una operación aritmética se excede la capacidad del acumulador en complemento a 2 (resultado mayor de 127 o menor de -128). C : (carry) acarreo o bit de arrastre. Se pone en 1 si como resultado de la operación efectuada se origina un transporte desde el bit más significativo del acumulador. Constituye un 9°bit. Otros Registros accesibles al programador PC : (Program Counter) contador de programa. Es un registro de 16 bits que apunta (contiene la dirección) al primer byte de la próxima instrucción a leer. Su valor se incrementa automáticamente cada vez que la instrucción o sus operandos son leídos (transferidos a la CPU). Este registro barre ordenadamente la secuencia de instrucciones (programa) salvo que una instrucción de salto lo direccione de otra manera. En el 6800 puede direccionar 64 KBytes de memoria. IX : (IndeX Register) registro índice. Es también un registro de 16 bits que se utiliza para efectuar direccionamientos de memoria del tipo "indexado" o como contador. Puede incrementarse, decrementarse, cargarse desde memoria o por programa, almacenarse en memoria, compararse, etc. SP : (Stack Pointer) puntero de pila o "stack". Registro de 16 bits que contiene una dirección de memoria (RAM) en la cual "apilar" o salvar los registros: Acc A, Acc B, CCR, IX y PC cuando el microprocesador debe atender interrupciones o alguna subrutina. Definiciones Instrucción: es una configuración de dígitos binarios que debe ser interpretada por la UC a fin de determinar QUÉ debe hacer (código de operación OP), sobre CUÁLES datos o registros tiene que operar (operando) y CÓMO debe acceder a ellos (direccionamiento). El MC6800 tiene un "set" (conjunto) de 72 instrucciones que con las variantes de direccionamiento posibles totalizan un máximo de197 y que le requieren, según los casos, de uno a tres bytes de programa. Código mnemotécnico o nemónico: es una asignación alfabética simple, representativa de la instrucción codificada. Lenguaje de máquina: lenguaje binario que puede entender una computadora. Programa ensamblador (assembler): programa que permite convertir el programa fuente o programa expresado en código mnemotécnico, a lenguaje máquina. Modos de Direccionamiento (I) Direccionamiento Implícito o Inherente: Se utiliza en instrucciones de 1 Byte que se refieren a los acumuladores o a otro registro de la CPU. Ejemplos: (se indica el código operación OP en hexadecimal, luego el código mnemotécnico y finalmente se explica la operación). ABA Hace Acc A = Acc A + Acc B . Suma los acumuladores. CLRA Hace Acc A = 0. Limpia el acumulador A. DECB Hace Acc B = Acc B - 1 . Decrementa el acumulador B. TSTA Prueba si el Acc A = 0 y pone en consecuencia los bits N y Z del registro de códigos de condición CCR. No afecta los acumuladores. INX Incrementa el registro índice. Hace IX = IX+1 TSX Hace IX = SP+1. Carga el registro índice con el valor del puntero de pila + 1. NOP No opera. Es un retardo de 2 ciclos de reloj. Sirve para rellenar espacios entre instrucciones (ajustar lazos de tiempo) Modos de Direccionamiento (II) Direccionamiento lnmediato: estas instrucciones requieren 2 bytes si involucran a los acumuladores y 3 cuando afectan a IX o SP: el primer byte es propiamente la instrucción y el resto es un número que se OPERA con el registro que corresponda. Modo inmediato ADDB, #$8D hace Acc B = Acc B + $8D. Suma al Acc B el número $8D CMPA, #$56 compara el Acc A con el número $56 y pone el registro CCR en consecuencia EORB #$39 hace Acc B = Acc B OREXC $39 LDX #$483C carga IX con el operando. Hace IX = $483C Modos de Direccionamiento (III) Direccionamiento Directo/Extendido: consiste en dar justamente la dirección donde se encuentra el operando, a continuación del OP. Se requerirán en total 3 bytes si el direccionamiento es Extendido, o sólo 2 bytes si se da por sobreentendida parte de la dirección. Motorola denomina Directo a un direccionamiento en el que se sobreentiende la parte alta de la dirección como 00 (direccionamiento Directo a Página Cero), lo que permite dirigirse mediante un único byte de dirección (luego de la instrucción) a las primeras 256 posiciones de memoria. STAB $FF Guarda el acumulador B en la dirección $00FF ADDA $05 Hace Acc A = Acc A+ ($0005). (M) indica contenido de M. En este ejemplo, suma al acumulador A el contenido de la posición de memoria $0005 y coloca el resultado en A ADDA $1805 Hace Acc A = Acc A+ ($1805) (Extendido) LDX $48 Carga IX con el contenido de $0048 y $0049: IX = (0048)(0049) JSR $0436 Salta a $0436, esto es: guarda en la pila (stack) el valor actual del PC, continúa el programa en $0436 (hace PC = $0436) y cuando encuentra una instrucción 39 (RTS: Return from Subroutine) restituye PC con el valor antes guardado en el stack. Modos de Direccionamiento (IV) Direccionamiento Indexado: requiere 2 bytes; el 1°es el OP y el 2°es un desplazamiento positivo que se suma al IX para dar la dirección del operando. El valor máximo del desplazamiento es de 255 ($FF). Ejemplos: si suponemos que (IX) = $2047 entonces: ADDB $48,X hace Acc B = AccB + ($2047+$48) = Acc B + ($208F) CLR $6A,X pone a 0 el lugar de memoria ($2047+$6A) ($20B1) = 00 LDX $08 hace (IX) = ($204F) ($2050) Carga el byte más significativo de IX con el contenido de $2047+$08 = ($204F) y el menos significativo con ($204F+1) = ($2050) Importante: al ejecutar una instrucción con este modo de direccionamiento no se altera el contenido del registro Indice IX Modos de Direccionamiento (V) Direccionamiento Relativo al PC: el anterior lo era para al registro índice. Motorola utiliza este tipo de direccionamiento sólo en las instrucciones de bifurcación. Las instrucciones con este tipo de direccionamiento requieren 2 bytes, el 2°de los cuales constituye un corrimiento u "offset" en complemento a 2, respecto al contador de programa. De esta manera, se puede bifurcar como máximo hasta 127 lugares hacia adelante y hasta 128 hacia atrás, contados desde el valor del PC luego de leída esta instrucción. Ejemplos: Si a partir de (PC) = $1018 se tiene: BRA $32 Bifurca incondicionalmente (Always) 32 lugares (hexadec.) hacia adelante desde PC=$101A. La próxima instrucción leída será la ubicada en PC=$101A+$32=$104C. BEQ $0F Prueba Z, si es "1" bifurca a $101A+$0F=$1029, si no, sigue el programa con PC=$101A. BPL $D6 Prueba N, si es "0" salta $D6 lugares (en Ca 2), o sea $2A lugares hacia atrás, contando desde $101A => PC = $0FF0. Si el resultado de la operación antes del salto era negativo (N=1) continuará el programa con PC = $101A CONTINUARÁ (en Sistemas Digitales)