LA RUTA DE DATOS EN LOS DSPs

Anuncio

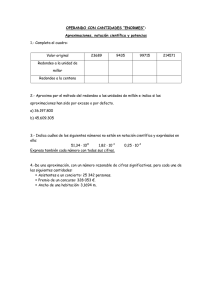

LA RUTA DE DATOS EN LOS DSPs DE COMA FIJA • USUALMENTE INCORPORA: - UN MULTIPLICADOR - UNA ALU - UNO O VARIOS DESPLAZADORES - REGISTROS PARA LOS OPERANDOS - OTRAS UNIDADES ESPECIALIZADAS: Æ LIMITADOR Æ LÓGICA DE REDONDEO Æ ETC... • LA RUTA DE DATOS NO SE EMPLEA PARA EL CÁLCULO DE DIRECCIONES. PARA ESTO SE EMPLEA UNA UNIDAD ESPECÍFICA USUALMENTE DENOMINADA AGU O ARAU. • EN LA RUTA DE DATOS, ASÍ COMO EN LA ESTRUCTURA DE LA MEMORIA, SE PONEN DE RELIEVE LAS GRANDES DIFERENCIAS CONCEPTUALES Y ESTRUCTURALES ENTRE LOS DSPs Y LOS PROCESADORES DE TIPO GENÉRICO. LA SECCIÓN MULTIPLICADORA EN LOS DSPs DE COMA FIJA (I) • DADO QUE LA MULTIPLICACIÓN ES EL TIPO DE OPERACIÓN MÁS FRECUENTE EN EL PROCESAMIENTO DIGITAL DE SEÑALES, SE PROCURA REALIZARLA DE LA MANERA MÁS EFICIENTE POSIBLE • NORMALMENTE, EL RESULTADO DEL PRODUCTO SE OBTIENE EN UN SOLO CICLO DE RELOJ • NO OBSTANTE, EXISTEN DISEÑOS SEGMENTADOS DE LA UNIDAD MULTIPLICADORA LO QUE HACE QUE UNA MULTIPLICACIÓN AISLADA PUEDA REQUERIR MÁS DE UN CICLO DE RELOJ (LATENCIA DE LA MULTIPLICACIÓN) • EN LOS MULTIPLICADORES SEGMENTADOS SOLO SE TARDA UN CICLO DE RELOJ EN PROCESOS DE MULTIPLICACION ITERATIVA. • PARA IMPLEMENTAR LA FUNCIONALIDAD MAC EXISTEN DOS ALTERNATIVAS: Æ MULTIPLICADOR INTEGRADO CON UN SUMADOR, DANDO LUGAR A UNA UNIDAD MULTIPLICADORA-ACUMULADORA Æ MULTIPLICADOR SEPARADO, CON UN REGISTRO ESPECÍFICAMENTE DEDICADO A CONTENER EL RESULTADO DEL PRODUCTO: EN ESTE CASO LA MULTIPLICACIÓN PUEDE VERSE AFECTADA POR LA LATENCIA DE LA ARQUITECTURA LA SECCIÓN MULTIPLICADORA EN LOS DSPs DE COMA FIJA (II) • EN CUANTO AL TAMAÑO DEL PRODUCTO, SE PUEDEN ENCONTRAR DOS SOLUCIONES: Æ OPERANDOS DE n BITS, Y RESULTADO DE 2n BITS ⇒ NO SE INTRODUCE ERROR EN LA OPERACIÓN Æ OPERANDOS DE n BITS Y RESULTADO DE m BITS, SIENDO m < n ⇒ PUEDE INTRODUCIRSE ERROR, PERO RESULTA MÁS ECONÓMICO DE IMPLEMENTAR • ¿CÓMO SE PASA EL RESULTADO DE LA MULTIPLICACIÓN A OTRAS ETAPAS DE CÓMPUTO? Æ SI SE TRATA DE PROCESOS TIPO MAC ITERATIVOS, SE TRABAJA CON LA LONGITUD TOTAL DE PRODUCTO, Y AL FINAL SE REDUCE NORMALMENTE SU TAMAÑO A LA LONGITUD DE PALABRA NATIVA Æ DADO QUE USUALMENTE EL RESULTADO (2n BITS) VA A SER GUARDADO CON IGUAL TAMAÑO QUE EL DE LOS OPERANDOS (n BITS = ANCHURA DE PALABRA DEL DATO NATIVO) SE RECURRE A: • SI SE TRABAJA CON ARITMÉTICA ENTERA: SE DEBE TENER LA SEGURIDAD DE QUE EL RESULTADO PRODUCTO FINAL PUEDE EXPRESARSE CON LOS n BITS ⇒ ES PRECISO LIMITAR EL RANGO DINÁMICO DE LAS SEÑALES DE ENTRADA. OTRA POSIBILIDAD ES ESCALAR EL RESULTADO TOMANDO UNA PORCIÓN MÁS SIGNIFICATIVA • SI SE TRABAJA CON ARITMÉTICA FRACCIONARIA: BASTA TOMAR LOS n BITS SUPERIORES (TRAS UN POSIBLE REDONDEO) Æ POR TANTO, LA ARQUITECTURA SUELE PERMITIR SELECCIONAR PORCIONES DEL REGISTRO ACUMULADOR O PRODUCTO PARA FACILITAR ESTE PROCESO. LOS REGISTROS ACUMULADORES EN LOS DSPs • SU MISIÓN ES CONTENER EL RESULTADO DE LAS OPERACIONES TIPO MAC Y DE OTRAS OPERACIONES. • EN LOS DSPs SUELEN ENCONTRARSE 2 E INCLUSO MÁS ACUMULADORES • UN SOLO ACUMULADOR PUEDE RESULTAR EN UN CUELLO DE BOTELLA DE LA ARQUITECTURA: DADO QUE ACTÚA TANTO COMO ORIGEN COMO DESTINO DE LAS OPERACIONES, PUEDEN REQUERIRSE FRECUENTES CARGAS Y ALMACENAMIENTOS DE SUS VALORES • SU TAMAÑO SUELE SER 2n+g SIENDO n LOS BITS NATIVOS Y g UNOS BITS DE GUARDA. CON LOS g BITS DE GUARDA SE CONSIGUE REALIZAR HASTA 2g ACUMULACIONES SIN QUE SE DÉ LUGAR A REBOSAMIENTO • LOS DSPs QUE INCORPORAN ESTOS g BITS DE GUARDA SUELEN HACER g=4 O g=8 • LOS DSPs QUE NO LOS INCORPORAN PUEDEN PRECISAR QUE: Æ LA SEÑAL DE ENTRADA SEA ESCALA ANTES DE SER SUMADA AL ACUMULADOR ⇒ DESPLAZAMIENTO A LA DERECHA CIERTO NÚMERO DE BITS. Æ ESTO SE PUEDE HACER POR PROGRAMA (CONSUMO DE TIEMPO), PERO ES MEJOR POR HARDWARE ⇒ EMPLEO DE DESPLAZADORES (ESCALADORES) LOS DESPLAZADORES Ó ESCALADORES EN LOS DSPs DE COMA FIJA (I) • EN EL CÓMPUTO NUMÉRICO PUEDE APARECER EL PROBLEMA DE QUE EL RESULTADO PUEDA EXCEDER LA CAPACIDAD NUMÉRICA DADA • PARA ABORDAR ESTE PROBLEMA SE PUEDE OPTAR POR DISMINUIR EL RANGO DINÁMICO DE LAS SEÑALES DE ENTRADA • PARA ELLO SE SOMETE A LOS DATOS A UN ESCALADO: SE LES DIVIDE POR UN FACTOR 2m ⇒ SE DESPLAZA EL DATO ARITMÉTICAMENTE A LA DERECHA m BITS • EL INCONVENIENTE ES QUE ESTO IMPLICA UNA PÉRDIDA DE PRECISIÓN: DISMUNUYE MAGNITUD REPRESENTADA PRECISIÓN = MAGNITUD DEL ERROR DE CUANTIFICACIÓN PERMANECE IGUAL • OTRO INCONVENIENTE ES LA DISMINUCIÓN DEL RANGO DINÁMICO • AL DISEÑAR UN PROGRAMA DE APLICACIÓN ES MUY IMPORTANTE DETERMINAR SI ES PRECISO REALIZAR ESTE ESCALADO Y EN QUÉ MAGNITUD Æ HERRAMIENTAS DE SIMULACIÓN LOS DESPLAZADORES O ESCALADORES EN LOS DSPs DE COMA FIJA (II) • EL USO DE BITS DE GUARDA EN LOS ACUMULADORES NO IMPLICA LA ELIMINACIÓN DE LA NECESIDAD DE ESCALAR: SI SE TIENEN 4 BITS DE GUARDA, AL LLEVAR EL RESULTADO A OTRA ETAPA DE CÓMPUTO ES PRECISO ESCALAR CON UN FACTOR DE 2-4 • FUNCIONALIDAD DE LOS DESPLAZADORES: Æ DESPLAZAMIENTO UNA VEZ A LA DERECHA (x2-1) O A LA IZQUIERDA (x2+1): ESTRUCTURALMENTE SIMPLE PERO POCO EFICIENTE SI EL FACTOR DE ESCALADO HA DE SER MAYOR Æ DESPLAZAMIENTO MÚLTIPLE A DERECHA (x2-m) O IZQUIERDA (x2+m), SIENDO m EL FACTOR DE DESPLAZAMIENTO (ESTRUCTURA : DESPLAZADORES DE TAMBOR) Æ ACTÚAN, DE MANERA TRANSPARENTE, EN LOS PROCESOS DE TRANSFERENCIA DE DATOS • LOS DESPLAZADORES PUEDEN UBICARSE DE MODO QUE REALICEN UN PRE-ESCALADO O UN POST-ESCALADO • LOS DESPLAZAMIENTOS UNITARIOS A DERECHA E IZQUIERDA PERMITEN ADEMÁS AJUSTAR EL RESULTADO AL FORMATO DEL TIPO DE ARITMÉTICA EMPLEADA(1), CASO DE NO SER LA EMPLEADA POR LA LÓGICA MULTIPLICADORA(2): ENTERA(2) Æ DESPLAZAMIENTO A LA IZQUIERDA ⇒ FRACCIONARIA(1) FRACCIONARIA(2) Æ DESPLAZAMIENTO A LA DERECHA ⇒ ENTERA(1) • LOS DSPs PUEDEN DISPONER DE MÚLTIPLES DESPLAZADORES UBICADOS EN LOS LUGARES OPORTUNOS PARA FACILITAR SEGÚN QUÉ PROCESOS ALGORÍTMICOS. LA GUARDA DE UN RESULTADO • DADO QUE LOS OPERANDOS SON DE n BITS Y EL RESULTADO SE SUELE OBTENER EN AL MENOS 2n BITS SURGE EL DILEMA DE CÓMO GUARDARLO EN MEMORIA. PUEDEN SEGUIRSE LOS SIGUIENTES CAMINOS: 1 GUARDAR LA DOBLE PALABRA COMPLETA, PARA MANTENER LA PRECISIÓN. ESTO PUEDE REQUERIR VARIOS CICLOS DE RELOJ EN LUGAR DE UNO SÓLO. ADEMÁS HABRÁ SECCIONES DE LA ALU QUE, AL PODER TRABAJAR SÓLO CON n BITS, HARÁN NECESARIO RECURRIR A ALGORITMOS DE PRECISIÓN EXTENDIDA. 2 GUARDAR EL DATO SOMETIDO A UN ESCALADO. CUANDO SE OPERA CON ARITMÉTICA ENTERA SE GUARDA SÓLO LA PARTE ALTA CON O SIN REDONDEO 3 GUARDAR EL DATO SIN ESCALADO. EN LA ARITMÉTICA ENTERA LOS n BITS MENOS SIGNIFICATIVOS BASTARÁN SI SE TIENE LA CERTEZA DE QUE LOS OPERANDOS VAN A ESTAR LIMITADOS A VALORES QUE SE SABE NO VAN A GENERAR RESULTADOS QUE EXCEDAN DE LA PALABRA NATIVA (LA PARTE ALTA SERÁN UNA MERA EXTENSIÓN DEL BIT DE SIGNO) 4 GUARDAR EL DATO SIN ESCALADO. EN LA ARITMÉTICA FRACCIONARIA BASTARÁ GUARDAR LA PALABRA DE MAYOR PESO CON O SIN REDONDEO EL REBOSAMIENTO Y LA SATURACIÓN DE UN RESULTADO • AL OPERAR ARITMÉTICAMENTE, SE PUEDE PRODUCIR UN REBOSAMIENTO DE LA CAPACIDAD DE REPRENTACIÓN NUMÉRICA: 11011101 +0 1 0 0 1 0 1 1 100101000 • SI NO SE TRABAJA CON PRECISIÓN EXTENDIDA, EL RESULTADO SERÁ ERRÓNEO • PUEDE PLANTEARSE LA CONVENIENCIA DE QUE EN ESTOS CASOS EL RESULTADO SE ADAPTE A LA MÁXIMA MAGNITUD (`POSITVA O NEGATIVA) REPRESENTABLE. EN EL EJEMPLO SERÍA ASUMIENDO VALORES SIN SIGNO: 11111111 • CON ESTE CRITERIO EL RESULTADO (RESULTADO SATURADO) SIGUE SIENDO ERRÓNEO PERO RESULTA MÁS CERCANO AL VALOR CORRECTO • EN CIERTOS ALGORITMOS O PROCESAMIENTOS TRABAJAR CON ESTE CRITERIO PUEDE RESULTAR DE UTILIDAD • SE PUEDE DISEÑAR UNA LÓGICA (LÓGICA DE SATURACIÓN) QUE AL DETECTAR UN REBOSAMIENTO ADAPTE EL RESULTADO, SI ASÍ SE DESEA, A SU VALOR SATURADO • SI SE TRABAJA CON ACUMULADORES CON BITS DE GUARDA, PUEDE SUCEDER QUE NO HAYA REBOSAMIENTO, PERO AL TRANSFERIRSE EL RESULTADO SE CONSIDERE QUE SÍ LO HAY: ES EL CASO EN QUE LOS BITS DE GUARDA SON SIGNIFICATIVOS. EN ESTE CASO SE REALIZA LA SATURACIÓN OPORTUNA (EL ACUMULADOR PERMANECE INVARIANTE, PERO EL DATO SE SATURA) EL REDONDEO DE UN RESULTADO • AL TRANSFERIR EL RESULTADO DEPOSITADO EN UN ACUMULADOR (AL MENOS DE DOBLE TAMAÑO DE LA PALABRA NATIVA), SI SE OPTA POR TOMAR SÓLO LA PARTE MÁS SIGNIFICATIVA (SEA REPRESENTACIÓN EN COMA FIJA FRACCIONARIA O ENTERA) CABE PLANTEARSE CÓMO SOLUCIONAR EN LO POSIBLE LA PÉRDIDA DE PRECISIÓN RESULTANTE • EXISTEN DOS POSIBILIDADES: 1 TRUNCACIÓN, SIN MÁS, DEL RESULTADO 2 TRUNCACIÓN, CON REDONDO DE LA PORCIÓN TOMADA • LA TRUNCACIÓN INTRODUCE UN ERROR ADICIONAL EN LA SEÑAL TRATADA. SE TRATA DE UN DESPLAZAMIENTO DE LA SEÑAL DADO QUE EL VALOR TRUNCADO SIEMPRE ES INFERIOR O IGUAL AL ORIGINAL NO TRUNCADO. • EL REDONDEO PERMITE MINIMIZAR ESTE ERROR • TÉCNICAS DE REDONDEO EN COMA FIJA: Æ REDONDEO AL VALOR MÁS PRÓXIMO Æ REDONDEO CONVERGENTE • EL REDONDEO PUEDE HACERSE POR PROGRAMA PERO RESULTA MUCHO MÁS ADECUADO HACERLO POR HARDWARE Æ DISPOSICIÓN EN LA ESTRUCTURA DE LOS DSPs DE UNA LÓGICA DE REDONDEO TÉCNICAS DE REDONDEO: REDONDEO AL VALOR MÁS PRÓXIMO • CONSISTE EN SUMAR AL BIT MENOS SIGNIFICATIVO DEL VALOR TRUNCADO EL BIT MÁS SIGNIFICATIVO DE LA PARTE ELIMINADA (O LO QUE ES LO MISMO, SUMAR AL VALOR ORIGINAL LA MITAD DEL PESO DEL BIT DEL PUNTO DE TRUNCAMIENTO): EJEMPLO: 1 0 0 1 0 1 0 1 1 0 1 0 1 1 0 12 Æ 1 0 0 1 0 1 1 02 1 0 0 1 0 1 0 1 0 0 1 0 0 1 0 12 Æ 1 0 0 1 0 1 0 12 punto de truncamiento 1 0 0 1 0 1 0 1 1 0 1 0 1 1 0 12 +0 0 0 0 0 0 0 0 1 0 0 0 0 0 0 02 1 0 0 1 0 1 0 1 0 0 1 0 1 1 0 12 +0 0 0 0 0 0 0 0 1 0 0 0 0 0 0 02 1 0 0 1 0 1 1 0 0 0 1 0 1 1 0 12 1 0 0 1 0 1 0 1 1 0 1 0 1 1 0 12 punto de truncamiento punto de truncanmiento • EL VALOR REDONDEADO UNAS VECES ES MENOR PERO OTRAS MAYOR QUE EL ORIGINAL: EN BUENA MEDIDA LOS ERRORES, SEGÚN EL CASO, SE COMPENSAN AUNQUE NO EXISTE LA GARANTÍA DE QUE LO SEAN TOTALEMENTE • EL INCONVENIENTE DE ESTE MÉTODO ES QUE SE INTRODUCE UN EFECTO DE ASIMETRÍA EN REDONDEOS REPETIDOS: EL VALOR MEDIO SIEMPRE SE REDONDEA POR EXCESO ⇒ SE INTRODUCE UN SESGO POSITIVO. TÉCNICAS DE REDONDEO: REDONDEO CONVERGENTE • AUNQUE EL EFECTO DE ASIMETRÍA QUE RESULTA DE UN REDONDEO AL VALOR MÁS PRÓXIMO ES DESPRECIABLE, EN ALGUNAS APLICACIONES (IIR Y FILTROS ADAPTATIVOS POR EJEMPLO) SÍ QUE PUEDE LLEGAR A SER PROBLEMÁTICO • LA TÉCNICA DE REDONDEO CONVERGENTE INCIDE EN SOLUCIONAR EN LO POSIBLE ESTE PROBLEMA • LA TÉCNICA ES IDÉNTICA A LA DE REDONDEO AL VALOR MÁS PRÓXIMO, EXCEPTO EN EL CASO EN QUE LA PARTE ELIMINADA POSEE SU BIT MÁS SIGNIFICATIVO A 1 Y EL RESTO A 0 (CASO DE VALOR INTERMEDIO) • EN ESTE CASO SE OPERA CON EL SIGUIENTE CRITERIO: Æ SI EL BIT MENOS SIGNIFICATIVO DE LA PARTE CONSERVADA ES UN 0, ENTONCES SE REDONDEO POR DEFECTO (TRUNCAMIENTO) Æ PERO SI ESE BIT ES UN 1 ENTONCES SE REDONDEA POR EXCESO (SE LE SUMA AL VALOR LA MITAD DEL PESO DE ESE BIT) • EJEMPLOS: 1 0 0 1 0 1 0 0 1 0 0 0 0 0 0 02 +0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 02 (*) 1 0 0 1 0 1 0 0 1 0 0 0 0 0 0 02 punto de truncamiento 1 0 0 1 0 1 0 1 1 0 0 0 0 0 0 02 +0 0 0 0 0 0 0 0 1 0 0 0 0 0 0 02 1 0 0 1 0 1 1 0 0 0 0 0 0 0 0 02 punto de truncamiento (*) el resultado con un redondeo al valor más próximo sería 10010101 Obsérvese que el redondeo convergente, para el caso intermedio, redondea al valor par más cercano