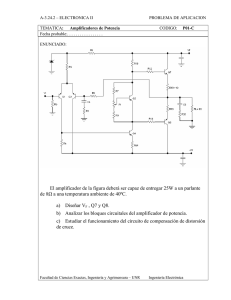

Universidad de Costa Rica Facultad de Ingeniería Escuela de Ingeniería Eléctrica IE – 0502 Proyecto Eléctrico [Estudio e implementación de un amplificador de audio de tipo AB] Por: [David José Pérez Arroyo A74837] Ciudad Universitaria Rodrigo Facio Diciembre del 2011 i [Estudio e implementación de un amplificador de audio de tipo AB] Por: [David José Pérez Arroyo] Sometido a la Escuela de Ingeniería Eléctrica de la Facultad de Ingeniería de la Universidad de Costa Rica como requisito parcial para optar por el grado de: BACHILLER EN INGENIERÍA ELÉCTRICA Aprobado por el Tribunal: ______________________________ Ing. José Miguel Páez Profesor Guía ____________________________ ____________________________ Ing. Ignacio Ramírez Antillón Ing. Mauricio Espinoza Profesor lector Profesor lector ii DEDICATORIA A mi familia que siempre me apoyó en los momentos más complicados que surgieron durante la realización del proyecto; y a toda las demás personas que contribuyeron a este proyecto por más pequeño que fuese su aporte. iii RECONOCIMIENTOS A Don José Miguel Páez por toda su amabilidad y disponibilidad para apoyar el desarrollo de este proyecto. A Don Ignacio Ramírez por su ayuda en la realización de este proyecto, especialmente por sus aportes en el capítulo 2. A Mauricio Espinoza por su amabilidad para atenderme toda vez que le fui a consultar. En resumen muchas gracias a los miembros del tribunal. iv ÍNDICE GENERAL ÍNDICE DE FIGURAS .................................................................................................... VII NOMENCLATURA ........................................................................................................... IX RESUMEN ........................................................................................................................... X CAPÍTULO 1: INTRODUCCIÓN ................................................................................ 1 1.1 OBJETIVOS ....................................................................................................................... 3 1.1.1 Objetivo general ................................................................................................... 3 1.1.2 Objetivos específicos ............................................................................................ 3 1.2 METODOLOGÍA ................................................................................................................ 4 CAPÍTULO 2: HISTORIA Y CONCEPTOS TEÓRICOS ........................................ 5 2.1 ANTECEDENTES ............................................................................................................... 5 2.2 CLASES DE AMPLIFICADORES .......................................................................................... 6 2.3 CLASE AB ........................................................................................................................ 7 2.3.1 Circuito de Pre-Polarización ................................................................................. 7 2.3.2 Transistores Thermal Track: ................................................................................. 9 CAPÍTULO 3: ANÁLISIS DEL AMPLIFICADOR DE POTENCIA 11 3.1 ANÁLISIS CUALITATIVO DEL AMPLIFICADOR .................................................................. 12 3.1.1 Fuentes de corriente ............................................................................................ 12 3.1.2 Etapa de entrada.................................................................................................. 13 3.1.3 Etapa de amplificación de tensión (VAS) .......................................................... 15 3.1.4 Etapa de salida (OPS) ......................................................................................... 17 3.2 ANÁLISIS CUANTITATIVO DEL AMPLIFICADOR................................................................ 19 3.2.1 La impedancia de entrada del amplificador ........................................................ 19 3.2.2 LSVG .................................................................................................................. 20 3.2.3 CMRR ................................................................................................................. 20 3.2.4 Potencia .............................................................................................................. 21 CAPÍTULO 4: AMPLIFICADOR EXPERIMENTAL ............................................ 22 4.1 EL ESPEJO DE CORRIENTE ............................................................................................... 23 4.2 FUENTE DE CORRIENTE DEL VAS ................................................................................... 24 4.3 ETAPA DE SALIDA .......................................................................................................... 26 4.4 GANANCIA DE TENSIÓN ................................................................................................. 27 4.5 BARRIDO DE FRECUENCIA .............................................................................................. 31 4.6 IMPEDANCIA DE ENTRADA: ............................................................................................ 33 CAPÍTULO 5: CONCLUSIONES Y RECOMENDACIONES ............................... 35 5.1 CONCLUSIONES .............................................................................................................. 35 5.2 RECOMENDACIONES....................................................................................................... 36 v BIBLIOGRAFÍA ................................................................................................................ 37 APÉNDICE I ....................................................................................................................... 39 1.1 Clase A: .............................................................................................................. 39 1.2 Clase B ................................................................................................................ 40 1.1.1 Configuración en simetría complementaria........................................................ 41 1.1.2 Distorsión de cruce por cero: .............................................................................. 42 APÉNDICE II ..................................................................................................................... 43 2.1 Distorsión Armónica: ......................................................................................... 43 2.2 Retroalimentación:.............................................................................................. 44 2.3 Retroalimentación en el amplificador de potencia ............................................. 46 APÉNDICE III.................................................................................................................... 49 ARQUITECTURA DEL AMPLIFICADOR ..................................................................................... 49 3.1 ETAPA DE ENTRADA ....................................................................................................... 51 3.1.1 Espejo de Corriente: ........................................................................................... 52 3.1.2 Fuentes de Corriente ........................................................................................... 53 3.1.3 Amplificador diferencial (Par diferencial) ......................................................... 56 3.2 ETAPA DE AMPLIFICACIÓN DE VOLTAJE (VAS). ............................................................. 62 3.2.1 VAS: ................................................................................................................... 63 3.2.2 Configuraciones típicas del VAS ....................................................................... 64 3.3 ETAPA DE SALIDA .......................................................................................................... 67 3.3.1 Tipo de distorsiones ............................................................................................ 68 3.3.2 Análisis de una etapa de salida simple ............................................................... 77 APÉNDICE IV .................................................................................................................... 80 4.1 ANÁLISIS EN DC: ........................................................................................................... 81 4.1.1 Fuente de corriente ............................................................................................. 81 4.1.2 Amplificador Diferencial .................................................................................... 85 4.1.3 Etapa de amplificación de potencial: .................................................................. 90 4.2 ANÁLISIS EN PEQUEÑA SEÑAL: ....................................................................................... 93 4.2.1 Etapa de entrada.................................................................................................. 95 4.2.2 Etapa de amplificación de tensión: ................................................................... 102 4.3 ETAPA DE SALIDA: ....................................................................................................... 105 4.4 DISEÑO DE LA FUENTE DE ALIMENTACIÓN ................................................................... 108 vi ÍNDICE DE FIGURAS Figura 2-1: Diferentes Clases de Operación para un Amplificador de potencia[3] ...................................... 6 Figura 2-2: Circuito de pre-polarización [5] ............................................................................................. 7 Figura 2-3: Uso de diodos en el circuito de Pre-Polarización [5] ................................................................ 8 Figura 2-4: Dispositivo Thermal Track [8] ................................................................................................ 9 Figura 2-5: Dispositivo Thermal Track [9] ............................................................................................... 10 Figura 3-1: Amplificador en estudio [9] .................................................................................................. 11 Figura 3-2: Fuentes de Corrientes [9] ..................................................................................................... 12 Figura 3-3: Etapa de entrada [9] ............................................................................................................ 13 Figura 3-4: VAS ..................................................................................................................................... 15 Figura 3-5: OPS ..................................................................................................................................... 17 Figura 4-1: Espejo de corriente .............................................................................................................. 23 Figura 4-2: Fuente de corriente experimental ........................................................................................ 23 Figura 4-3: Fuente de corriente del VAS ................................................................................................. 24 Figura 4-4: Fuente de corriente experimental ........................................................................................ 25 Figura 4-5: Tensión Base emisor simulada y experimental ...................................................................... 26 Figura 4-6: Comparación de tensiones entre el transistor y el diodo ........................................................ 27 Figura 4-7: Ganancia de tensión simulada .............................................................................................. 28 Figura 4-8: Ganancia de tensión experimental ....................................................................................... 29 Figura 4-9: Desfase entre las señales de entrada y salida ........................................................................ 30 Figura 4-10: Barrido en frecuencia simulado .......................................................................................... 31 Figura 4-11: Barrido de frecuencias obtenido experimentalmente .......................................................... 32 Figura 4-12: Circuito para obtener la impedancia de entrada experimentalmente ................................... 33 Figura 4-13: Impedancia de entrada experimental ................................................................................. 34 Figura 5-1: Esquemático de un amplificador Clase A [5] .......................................................................... 39 Figura 5-2: Concepto base para el funcionamiento de la clase B [3] ......................................................... 40 Figura 5-3: Configuración en Simetría complementaria [7] ..................................................................... 41 Figura 5-4: Distorsión por cruce por cero [5] .......................................................................................... 42 Figura 5-5: Tipos de retroalimentación:[10] ........................................................................................... 45 Figura 5-6: Arquitectura de 3 etapas [10] ............................................................................................... 49 vii Figura 5-7: Etapa de entrada típica.[11] ................................................................................................. 51 Figura 5-8: Espejo de corriente [12] ....................................................................................................... 52 Figura 5-9: Fuente de corriente constante [10] ....................................................................................... 53 Figura 5-10: Fuente de corriente Mejorada [10] ..................................................................................... 55 Figura 5-11: Configuración típica del amplificador diferencial [12] .......................................................... 57 Figura 5-12: Corrientes de un par diferencial en función del voltaje diferencial [12] ................................. 58 Figura 5-13: Antes y después de la incorporación de RE. [11] .................................................................. 61 Figura 5-14: Pares de retroalimentación complementaria [11] ................................................................ 61 Figura 5-15: Operación del VAS [11] ...................................................................................................... 63 Figura 5-16: Diferentes configuraciones del VAS .................................................................................... 65 Figura 5-17: Tipos de EF [10] ................................................................................................................. 72 Figura 5-18: Topologías en paralelo: ...................................................................................................... 75 Figura 5-19: Etapa de salida en análisis .................................................................................................. 77 Figura 5-20: Circuito equivalente con el modelo de gran señal ................................................................ 78 Figura 5-21: Circuito con resistencias reflejadas en la base ..................................................................... 78 Figura 5-22: Amplificador de potencia [9] .............................................................................................. 80 Figura 5-23: Amplificador de potencia ................................................................................................... 81 Figura 5-24: Fuente de corriente ........................................................................................................... 82 Figura 5-25: Simulación de la fuente de corriente ................................................................................... 83 Figura 5-26: Simulación de la fuente de corriente restante ..................................................................... 84 Figura 5-27: Etapa de entrada. .............................................................................................................. 85 Figura 5-28: Etapa de entrada, en análisis .............................................................................................. 86 Figura 5-29: Simulación etapa de entrada, en análisis............................................................................. 89 Figura 5-30: Etapa de amplificación de tensión ...................................................................................... 90 Figura 5-31: Simulación de la etapa de amplificación de tensión ............................................................. 92 Figura 5-32: Impedancias de las fuentes de corriente constante ............................................................. 94 Figura 5-33: Pequeña señal para el amplificador diferencial.................................................................... 96 Figura 5-34: Pequeña señal espejo de corriente. .................................................................................. 100 Figura 5-35: Pequeña señal del VAS. .................................................................................................... 102 Figura 5-36: Etapa de salida ................................................................................................................ 105 Figura 5-37: Etapa de salida simplificada.............................................................................................. 106 Figura 5-38: Topología a usar para el diseño de la fuente de alimentación............................................. 108 Figura 5-39: Salida del circuito............................................................................................................. 109 viii NOMENCLATURA NFB: Retroalimentación Negativa LF: Bajas Frecuencias HF: Altas Frecuencias VAS: Etapas de amplificación de Voltaje OPS: Etapa de salida CC o CDOM: Capacitor de Polo Dominante EF: Emisor seguidor ix RESUMEN En el presente proyecto se seleccionó y analizó una topología de un amplificador de potencia clase AB. Para esto se requirió de una extensa revisión bibliográfica, de la que se obtuvo los conocimientos necesarios para realizar un estudio a fondo del amplificador, esto para entender el comportamiento general del circuito, para hacer que su implementación fuera más sencilla. Más detalladamente, se analizó cada una de las 3 etapas que componen un amplificador de audio. Se buscó conocer el funcionamiento de cada una de éstas, las ventajas obtenidas de la topología en uso (comparándolas con otras topologías existentes), los problemas más comunes a las que son propensas y como evitarlos o disminuirlos. Se comparó el comportamiento obtenido experimentalmente, con el comportamiento descrito en la teoría y en las simulaciones realizadas. Midiendo parámetros importantes de cada etapa, especialmente las corrientes a la que son polarizados cada transistor. Los cuales están muy apegados a los valores teóricos. Se hizo uso de transistores de última generación hechos especialmente para las aplicaciones de audio, los cuales dan como resultado una distorsión muy baja de la señal de salida. Esto siendo posible gracias a la integración de un diodo al chip del transistor, reduciendo así la distorsión de cruce. Se obtuvo un amplificador de potencia de una gran eficiencia y rendimiento sonoro. Su capacidad se pudo experimentar en el laboratorio, concluyendo su gran desempeño a pesar de que se tuvo que limitar la alimentación del circuito debido a las características del equipo en uso. x Capítulo 1: Introducción El presente trabajo consta de cinco capítulos y cuatro apéndices. El primer capítulo presenta la introducción, objetivos y metodología del proyecto. El segundo capítulo expone un poco de historia (desde los avances más importantes del siglo XX en el campo de la electrónica analógica hasta el concepto de amplificación), los tipos de amplificadores de potencia, la clase AB y por último se presentan los transistores “Thermal Track”. El tercer capítulo muestra el amplificador de potencia en estudio. La primera sección presenta las etapas que lo componen, se determina el tipo de topología de la etapa, sus ventajas, y algunos aspectos destacables de cada una. La segunda sección expone y comenta los parámetros del amplificador, obtenidos por el análisis matemático realizado en el apéndice IV, presentando las ventajas de cada uno de estos. El cuarto capítulo exhibe los parámetros del amplificador obtenidos, tanto en la medición experimental realizada, como en la simulación correspondiente; realizando además una comparación entre datos. El quinto capítulo muestra las conclusiones y las recomendaciones a las que se llegó después de terminar el proyecto. En el primer apéndice se amplía el tema relacionado con el segundo capítulo, entiéndase los tipos de amplificadores además de la clase AB (estudiada en este proyecto), sus ventajas, desventajas y características importantes de cada uno. 1 En el segundo apéndice se explican los conceptos de estabilidad, distorsión y retroalimentación del amplificador. Se quiere hacer hincapié en que los temas no eran parte de los objetivos del proyecto pero, se optó por realizar una investigación general sobre los problemas que sufren este tipo de amplificadores de audio. En el tercer apéndice se exponen todos los conceptos teóricos de la composición de un amplificador de audio. Se detallan la arquitectura de tres etapas, la función de cada una de las etapas, sus ventajas, desventajas y tipos de configuraciones disponibles. Y por último el cuarto apéndice presenta todo el análisis matemático realizado para obtener los datos del capítulo cuatro, además del cálculo de la fuente de alimentación. 2 1.1 Objetivos 1.1.1 Objetivo general • Desarrollar un amplificador de audio tipo AB. 1.1.2 Objetivos específicos • Seleccionar y analizar una topología de un amplificador de audio tipo AB, basándose en los conocimientos adquiridos en los diferentes cursos de la carrera. • Implementar un amplificador de audio básico de buena calidad. • Diseñar la fuente de alimentación necesaria para alimentar al amplificador de potencia. 3 1.2 Metodología Para completar satisfactoriamente el presente proyecto se optó por dividirlo en tres etapas. La primera etapa consistió en una revisión bibliográfica con el fin de obtener los conocimientos necesarios para la realización del proyecto. Se buscó entender la funcionalidad de las tres etapas que componen un amplificador de potencia, sus diferentes topologías, las ventajas y desventajas de cada una de estas; con el fin de entender el circuito en general. La revisión bibliográfica consistió en la visita a las bibliotecas de la universidad y una búsqueda extensiva en la red mundial de información (en Ingles “World Wide Web”). Se quiere hacer Hincapié en los puntos 10 y 11 de la bibliografía, donde se pudo encontrar mayor información acerca del tema buscado. La segunda etapa del proyecto consistió en el análisis matemático del amplificador a estudiar. Para esta etapa se pusieron en práctica los conocimientos adquiridos en la primera etapa del proyecto así como también, los conocimientos obtenidos en cursos anteriores de la carrera, en especial el curso de Electrónica I ya que, el circuito en estudio estaba hecho principalmente de transistores. La última etapa consistió en la implementación experimental del circuito, trabajo de laboratorio. En esta etapa se probaron los conocimientos obtenidos en las dos anteriores etapas, porque se debía tener un conocimiento amplio del circuito para poder solucionar los problemas que surgieran durante la implementación. 4 Capítulo 2: Historia y Conceptos Teóricos 2.1 Antecedentes Fue a mediados del siglo XX que se descubrió uno de los inventos más importantes en la historia de la electrónica, el transistor. Este fue desarrollado en los Laboratorios Bell de la AT&T en Nueva Jersey en diciembre de 1947, por William Bradford Shockley en conjunto con John Bardeen y Walter Houser Brattain. El transistor se considera como el mayor invento del siglo XX, pues es un dispositivo electrónico básico que dio lugar a los circuitos integrados y demás elementos de alta escala de integración. Desde su invención se ha utilizado como herramienta para solucionar diferentes problemas electrónicos. Entre los más importantes se encuentra la amplificación de las señales. Una definición elemental de amplificación fue dada por William Shockley: "1Si usted toma un fardo de heno y lo ata a la cola de una mula y a continuación le prende fuego, y compara luego la energía disipada a partir de entonces por la mula con la energía disipada antes por usted en frotar el fósforo, entenderá plenamente el concepto de amplificación". En palabras más científicas, el concepto de amplificación tiene que ver no solo con la capacidad para aumentar de tamaño una señal eléctrica (ya sea voltaje o corriente) sino con la capacidad de entregarla a otra instancia (denominada carga) con más energía de la que tenía originalmente. Existen diferentes tipos de amplificación. Estos se dividen según el tipo de señal recibida en la entrada y el tipo de señal amplificada en la salida. Por ejemplo, los amplificadores de tensión reciben una señal de tensión en la entrada y en la salida dan la misma señal de entrada, solo que amplificada. Existen otros tipos de amplificadores como los de corriente, los transconductancia, los de potencia, etc. 1 David A. Kaplan. (1999). “Los Silicon Boys”, pág. 56 5 Los amplificadores de potencia son aquellos que, aparte de suministrar una mayor tensión, proveen también una mayor corriente (amplificación de tensión y amplificación de corriente y, por ende, amplificación de potencia). Usualmente son utilizados en el campo del audio, debido a que su amplificación de voltaje se encarga de aumentar la señal de entrada (señal de audio) y su amplificación de corriente dará la corriente necesaria para alimentar los altavoces (Bobinas), los encargados de generar el sonido. Este tipo de amplificador posee varias clases de configuraciones, cada una con sus ventajas y desventajas con respecto a la otra. 2.2 Clases de Amplificadores Los amplificadores de potencia se clasifican en función del punto de trabajo en que se polarizan los dispositivos de potencia (transistores), y en la fracción del ciclo de señal durante las que conducen, como consecuencia de ello. En la figura 2-1 se observa los diferentes tipos de operación. [3] Figura 2-1: Diferentes Clases de Operación para un Amplificador de potencia[3] 6 2.3 Clase AB La clase AB, tiene todas las características de la clase B detalladas en el apéndice I. La única diferencia es que integran al circuito una de las tantas soluciones al problema de la distorsión de cruce por cero. El método para evitar gran parte de la distorsión es hacer funcionar los elementos activos de modo que las corrientes I1 eIi2 no sean nulas dentro de un poco más de los 180º, o sea, un poco más de un semi-ciclo. En otras palabras, el dispositivo se polariza en la zona lineal pero en un punto Q muy próximo al extremo de respuesta lineal. En esta configuración se sacrifica la disipación de una pequeña cantidad de potencia cuando opera sin señal, a cambio de evitar la zona muerta de respuesta. [3] 2.3.1 Circuito de Pre-Polarización Para reducir esta distorsión se necesita incluir, en la configuración básica del amplificador, un circuito de pre-polarización. La función es montar la señal de entrada sobre componentes de potencial directo de +0,7V y -0,7V para el par de transistores. De manera que estos Vi > 0,7V empiecen a conducir para tensiones de Vi > 0 y Vi < 0 y no y Vi < 0,7V como el circuito original. En la figura 2-2 se muestra el concepto de una red de polarización. Figura 2-2: Circuito de pre-polarización [5] 7 Una de las soluciones más simples para obtener las componentes de tensión en DC, sería la utilización de fuentes independientes, con estos valores. Pero esta solución no es práctica. La utilización de divisores de voltajes resistivos es una de las soluciones más pensada. Pero debido a que las uniones base-emisor de los transistores varían su tensión de encendido al variar la temperatura, lo cual no ocurre con el potencial en las resistencias, haciendo de ésta una solución defectuosa. La solución más frecuente es el uso de diodos montados sobre el disipador de los transistores, para acoplarlos térmicamente a las uniones base-emisor y para compensar las variaciones de los voltajes de las uniones debido a los cambios de temperatura. En la figura 2-3 se puede observar la red de polarización hecha a partir de diodos [5] Figura 2-3: Uso de diodos en el circuito de Pre-Polarización [5] 8 Los diodos acoplados al disipador tienen ciertas desventajas, ya que el disipador no cambia su temperatura de manera inmediata; entonces habrá lapsos de tiempo en que el transistor aumenta su temperatura y el diodo no. Provocando que vuelva aparecer la distorsión de cruce. En la actualidad existen dispositivos creados específicamente para evitar este problema. Seguidamente se detalla uno de estos dispositivos, los transistores “Thermal Track”, componentes de última generación. 2.3.2 Transistores Thermal Track: La familia de transistores ThermalTrak, se desarrolló especialmente para las aplicaciones sonoras. Debido a los problemas que se presentaban en el periodo de “warmup” o tiempo de calentamiento, la ON semiconductor ha ideado una solución muy innovadora. Ha integrado al mismo dispositivo una tecnología de diodo ultra-rápido, para la detección de cambio de temperatura, logrando así una alta fidelidad sonora. En la figura 2-4 se puede observar el esquemático de los dispositivos “ThermalTrak” [8]. Figura 2-4: Dispositivo Thermal Track [8] 9 Las ventajas de integrar el diodo a un mismo dispositivo, no sólo es la precisión a los cambios de temperatura sino, además la reducción de los componentes en el circuito, ya que elimina circuitos de compensación. Un buen parámetro para medir los transistores de potencia es la variación de hFE (constante de amplificación) en función de la corriente de colector. Por ejemplo, si comparamos el transistor de la serie 2N6031, de On semiconductors, especializado en el manejo de altas potencias, con el transistor Thermal Track NJL1302D, se puede ver claramente la superioridad de este último. Pues para cambios en la corriente entre los 0,5 y 3 amperios, el hFE del 2N6031 varía entre 75 a 120, mientras que el NJL1302D, para los mismos valores de corriente, el hFE es prácticamente lineal. En la figura 5-10 se visualiza mejor la comparación anteriormente hecha. [9]. Figura 2-5: Dispositivo Thermal Track [9] Esta característica es de suma importancia para tener valores fijos del hFE, ante cambios de la corriente de colector por causas externas no deseadas. En conclusión el uso de esta familia parece llevar a muy buenos resultados auditivos. Es por estas razones que se ha decidido utilizar esta nueva y novedosa tecnología, para el desarrollo de este proyecto, implementando un amplificador de potencia de clase AB en base a ellos. 10 Capítulo 3: Análisis del amplificador de Potencia El presente capitulo realiza la justificación del uso de la arquitectura del amplificador de potencia seleccionada, así como de cuáles son las ventajas de los diferentes tipos de etapas escogidas. Seguidamente se presenta en la figura 3-1 el amplificador en estudio: Figura 3-1: Amplificador en estudio [9] Como se puede apreciar en la figura 3-1, el amplificador en estudio es de la topología de tres etapas mencionada en el apéndice II; configuración que es considerada como una de las mejores topologías para los amplificadores de audio. 11 Además en la figura 3-1 se puede observar las 3 etapas debidamente identificadas y las fuentes de corriente que polarizan la etapa de entrada y el VAS. Seguidamente se pretende justificar el uso de este tipo de etapas 3.1 Análisis cualitativo del amplificador 3.1.1 Fuentes de corriente La figura 3-2 muestra el tipo de fuente de corriente utilizados en el amplificador: Figura 3-2: Fuentes de Corrientes [9] Es una fuente de corriente constante de doble transistor la cual tiene la función de polarizar la VAS. Esta se compone por los transistores TR8 y TR9 en conjunto con C3, R9 y R5. Este tipo de fuente es muy usada y brinda menos variaciones de tensión que otros tipos de configuraciones como las que usan diodos, la idea es que la tensión base-emisor de TR8 sea igual a la tensión en R20, logrando una corriente aproximadamente constante ante variaciones de la carga. La caída en R19 se puede considerar despreciable para efectos prácticos, aunque esto dependerá si el valor de la resistencia es muy alto. Para mayor detalle sobre las fuentes de corriente referirse al apéndice III. 12 Los restantes componentes, TR4, R10, R13 y C4 conforman una segunda fuente de corriente. La idea de implementar una fuente sobre otra fuente de corriente es aprovechar el potencial constante de la primera para generar otra corriente. Esta fuente aprovecha el potencial constante del emisor-colector del transistor TR8. Para mayor detalle referirse al apéndice IV. 3.1.2 Etapa de entrada La figura 3-3 presenta el tipo de etapa de entrada en estudio: Figura 3-3: Etapa de entrada [9] 13 En la figura 3-3 el circuito ubicado en el lado izquierdo del transistor TR1 es un filtro paso banda. El circuito tiene la función de filtrar las frecuencias no audibles, por ende no es necesario amplificarlas. El rango usual del filtro paso banda es [20 Hz-20KHz] que son aquellas frecuencias que son audibles por el oído humano; aunque en la actualidad se ha demostrada que si se extiende este rango a [20 Hz-200KHz], las frecuencias mayores a 20KHz proporcionan una mejor ubicación de los sonidos, dándole profundidad al sonido. Del lado izquierdo del TR7 se puede ver la red de retroalimentación, la encargada de sensar la corriente de salida y transformarla en una tensión de retroalimentación. Al tener una retroalimentación global se tendrá ventajas en la reducción de la distorsión armónica, la reducción de la impedancia de salida, el aumento del rechazo de la alimentación (PSRR) y una mejor estabilidad; remitirse al apéndice II para obtener mayor detalle sobre los beneficios de la retroalimentación global en un amplificador de potencia. Las resistencias R6 y R14 dan una retroalimentación local al circuito brindando todas las ventajas del uso de la retroalimentación negativa, además dan la posibilidad de usar una mayor corriente de cola, esto con el objetivo de disminuir la distorsión de altas frecuencias atribuida a las no-linealidades de los transistores. Las resistencias R11 y R12 su función es dividir de igual manera la corriente de cola en las dos piernas del amplificador diferencial. La incorporación de un espejo de corriente garantiza la equidad de corriente en las dos piernas de la etapa de entrada, brindando así la cancelación del segundo armónico obteniendo así una reducción de la distorsión en altas frecuencias, además proporciona un menor DC offset debido a la desigualdad en las corrientes de base que fluyen a través de resistencias de entrada y de retroalimentación. 14 Por último la utilización de los pares de retroalimentación complementaria (CFP por sus siglas en ingles), garantiza una muy buena linealidad del circuito ya que aumenta el factor de retroalimentación local. Además tiene un buen equilibrio entre el ruido y la linealidad producido por los CFP; esto se puede observar por el valor de las resistencias R7 y R15. Se puede garantizar que la etapa de entrada en estudio tendrá muy buena linealidad y una muy baja distorsión a altas frecuencias; concluyendo que la etapa de entrada está maximizada. Para mayor detalle sobre la composición de la etapa de entrada referirse al apéndice III. 3.1.3 Etapa de amplificación de tensión (VAS) En la figura 3-4 muestra la configuración utilizada para la etapa de amplificación de tensión: Figura 3-4: VAS 15 La VAS es de tipo Darlington, lo que significa que tendrá una menor distorsión con respecto a las demás configuraciones detalladas en el apéndice III. El aumento del β por el uso de la topología Darlington y el uso de la fuente de corriente logrará aumentar la ganancia de lazo abierto, provocando mejor estabilidad. Además el uso de la fuente de corriente aumenta la impedancia de colector efectiva en el transistor lo que lleva consecuentemente a una mayor ganancia de tensión. Refiérase al apéndice III para mayor detalles el VAS. El capacitor C6 es el encargado de manejar la estabilidad del circuito. Su función es evitar una oscilación de Nyquist; haciendo que la frecuencia PI disminuya. El método de estabilidad se conoce como compensación de Miller de polo dominante. Referirse al apéndice II para mayor detalle sobre la estabilidad del circuito. Concluyendo el VAS en estudio logra solucionar problemas de estabilidad del circuito, dando mayor capacidad de corriente, logrando un alta amplificación de tensión y una muy baja distorsión debido a la NFB local. 16 3.1.4 Etapa de salida (OPS) Lla figura 3-5 muestra la OPS en análisis: Figura 3-5: OPS 17 En la figura 3-5 se observa la etapa de salida de clase AB y de tipo emisor seguidor (EF, por sus siglas en inglés “Emitter follower”) usando transistores en paralelo. Por ende esta etapa tiene una distorsión de cruce muy baja; ya que el rango de tensión de cruce de una OPS en EF es muy amplio en comparación con otras topologías analizada en el apéndice III. El problema del seguimiento térmico se resuelve con la utilización de los transistores “Thermal Track”; además reduce también la distorsión de cruce, debido al diodo integrado al circuito integrado. Para mayor detalle de estos dispositivos consultar el capítulo anterior. Aunque este tipo de OPS no tiene una red de desconexión, como el otro tipo de seguidor emisor detallado en el apéndice III, no tiene problemas con la distorsión de conmutación debido que los valores de las resistencias de emisor son muy bajos; ofreciendo una vía de descarga de menor impedancia de las cargas almacenados en las bases transistores. Con respecto a la distorsión provocada por las grandes señales, mejor conocida como caída de beta; el uso de transistores en paralelo ayudar a dividir equitativamente la corriente entre los dos transistores, reduciendo este tipo de distorsión. El uso de transistores en paralelo aumenta la capacidad de potencia de salida del amplificador. Para mayor detalle sobre las distorsiones que afectan a la OPS y sus diferentes soluciones referirse al apéndice III. La función del capacitor C10 se relaciona con la conducta de los diodos en corriente alterna, ya que se comportan como una resistencia dinámica por estar polarizados y como las bases de los transistores están unidas, se coloca el C10 para minimizar las diferencias de éstas. Concluyendo se puede decir que se tiene una OPS con valores muy bajos de distorsión y muy buena capacidad de potencia. 18 3.2 Análisis cuantitativo del amplificador En la presente sección se exponen los parámetros del amplificador, obtenidos a partir del cálculo teórico, expuestos en el apéndice IV. Después de un análisis del amplificador en DC (para obtener los puntos de operación de cada transistor) y en AC (pequeña señal) se han obtenido los siguientes parámetros, impedancia de entrada, ganancia de tensión de señal grande (LSVG, por sus siglas en inglés “Large Signal Voltage Gain”) relación de modo común (CMRR, por sus siglas en inglés, “Common Mode Rejection Radio”) y potencia disipada en los transistores de salida. A continuación se presentan los valores: 3.2.1 La impedancia de entrada del amplificador La impedancia de entrada del amplificado obtenida de los cálculos realizados en el apéndice IV fue: Z i ≈ 32 kΩ ( 3.2.1-1) Se debe anotar que la impedancia de entrada debe ser grande para poder limitar la corriente que recibe de la fuente de audio. Por lo que una impedancia de entrada de 32K cumple con lo requerido. 19 3.2.2 LSVG Se recuerda que el parámetro LSVG es la relación entre el cambio en la tensión de salida con respecto a cambios en la tensión de entrada. Lo que da a conocer cuánto es aproximadamente la ganancia de potencial en el modo común y el modo diferencial. Este parámetro usualmente tiene valores muy grandes. A continuación se muestra el resultado obtenido del análisis del apéndice IV: Vo = 501kVD + 32VA ( 3.2.2-1) Como se puede ver en este parámetro la ganancia de tensión es muy alta, como se espera que sea para este tipo de amplificador. Se menciona además que los cambios en la componente de modo común de la señal de entrada serán muy poco amplificados, mientras que los cambios en la componente en modo diferencial serán altamente amplificados. 3.2.3 CMRR La relación de rechazo de modo común es un indicador sobre el valor de la ganancia de modo común ya que, se busca tener esta ganancia lo más bajo posible en el amplificador. Se busca que la ganancia del circuito sea, en su mayoría diferencial, porque la ganancia en modo común tiene efectos negativos sobre el amplificador, el más importante es la ampliación del ruido. Seguidamente se presenta el resultado del cálculo: A CMRR = 20 ⋅ log D AA 501k 20 ⋅ log = 84dB 32 ( 3.2.3-1) Como se observa en la figura (3.2.3-1) se tiene un valor alto del CMRR, por lo que se garantiza que la ganancia sea principalmente diferencial. 20 3.2.4 Potencia Con respecto a la potencia disipada en los transistores, se realizó un análisis de la potencia máxima teórica que podría disipar los transistores, despreciando varias caída de tensión en las resistencias por su valor tan pequeño; la idea fue poner un tope máximo de disipación, que nunca se pudiera alcanzar. Seguidamente se presenta el valor obtenido, para mayor detalle consultar apéndice IV: PT ,Max = 17.25W Esta potencia es la máxima teórica que disiparía cada uno de los cuatro transistores de salida, es pequeña por que se usan transistores en paralelo. 21 Capítulo 4: Amplificador Experimental El presente capitulo tiene como objetivo dar a conocer algunos de los parámetros obtenidos experimentalmente. Se realizaron comparaciones entre los valores obtenidos por la medición experimental y por las simulaciones realizadas. Primeramente se quiere hacer hincapié en las limitaciones que se tuvieron a la hora de implementar el circuito • El circuito se implementó en una tarjeta de prototipos, esto ya que es más fácil de implementar; pero esto conlleva un problema debido a que la tarjeta de prototipos tiene una limitación de corriente de típicamente 1A, aunque hay datos que reflejan que podría manejar hasta 3A. • La alimentación del circuito no se pudo llevar a la diseñada [+55V,-55V], esto debido a las limitaciones de las fuentes de tensión usadas; por eso se trató de obtener el valor más cercano a la tensión diseñada, se pudo manejar una alimentación de [+30V,-30V]. • Las fuentes de tensión tenían una limitación de corriente la cual provocó una limitación en la amplitud de la señal de entrada ya que, si se tenía un valor muy alto en la señal de entrada, las fuentes no podían entregar la corriente necesaria. A continuación se presentan los datos experimentales y se comparan con los obtenidos en las simulaciónes realizada en OrCad. 22 4.1 El espejo de corriente Los valores de corriente obtenidos de la simulación se presentan en la figura 4-1: Figura 4-1: Espejo de corriente Mientras que el valor obtenido experimentalmente se presenta en la figura 4-2: Figura 4-2: Fuente de corriente experimental 23 La figura 4-2 muestra el potencial entre las resistencias de las sendas piernas de corriente. Si se recuerda que ambas resistencias tienen un valor de 68Ω , se puede obtener la corriente por ellas aplicando la ley de Ohm; se obtiene, entonces, una corriente de 3.15mA y 3.02mA . Si se comparan los resultados obtenidos se observa una corriente muy similar en el espejo de corriente, lo cual concuerda con la teoría; pero el valor de esta corriente es de casi el doble de la simulada, esto se debe a las diferencias entre los Betas (HFE) de los transistores y al uso de un tipo diferente en los transistores de la etapa de entrada y la fuente de corriente. Se puede concluir que la etapa de entrada está funcionando como lo estipula la teoría. 4.2 Fuente de corriente del VAS En la figura 4-3 se presenta la simulación obtenida de la fuente de corriente que alimenta la etapa de amplificación de tensión. Figura 4-3: Fuente de corriente del VAS 24 Recordando que la corriente que fluye por la resistencia R22 en la figura 4-3 se dirige a la etapa de salida del amplificador, más específicamente a polarizar los diodos (circuito de polarización de la OPS) y luego entra al VAS. Seguidamente se presenta en la figura 3-4 los valores obtenidos experimentalmente Figura 4-4: Fuente de corriente experimental En la figura 4-4 se aprecia el potencial de la resistencia R22 y R23 de la figura 3-1; conociendo que su valor es 100Ω , se puede obtener su valor de corriente el cual ronda los 12mA . Comparando los resultados obtenidos experimentalmente y simuladamente se comprueba que la implementación fue todo un éxito. Pudiendo decir que tanto la etapa de entrada como la etapa de amplificación de tensión se mostraron debidamente polarizadas. 25 4.3 Etapa de salida Con respecto a la etapa de salida se presenta en la figura 4-5, el valor de la tensión base emisor obtenida experimental y simuladamente: Figura 4-5: Tensión Base emisor simulada y experimental Como se puede comparar en la figura 4-5 el valor experimental es muy cercano al valor obtenido en la simulación; ya que el valor experimental es prácticamente 500mV y el experimental es de 533mV , dando un porcentaje de error de 6.6%. De lo anterior se concluye que los transistores de la etapa de salida funcionaron correctamente. 26 Seguidamente se presenta en la figura 4-6, las tomas de los valores del potencial BaseEmisor y la tensión de diodo. Recordando que como los transistores “Thermal Track” integran un diodo en el circuito integrado, se realizó el sensado de temperatura de manera mucho más rápida y eficiente; por lo que estas dos tensiones tendieron a ser muy similares. Figura 4-6: Comparación de tensiones entre el transistor y el diodo Como muestra la figura 4-6 las tensiones son muy parecidas. Se obtiene un porcentaje de error menor al 2%; por lo que se puede decir que el diodo tiene una reacción muy rápida y precisa del sensado de temperatura en el transistor. 4.4 Ganancia de Tensión A continuación se presenta el valor obtenido simuladamente de la ganancia de tensión del circuito, poniendo como entrada una sinodal de 100mV de amplitud y 1Khz de frecuencia. 27 Figura 4-7: Ganancia de tensión simulada En la figura 4-7 se observa que con una entrada sinodal de 100mV amplitud y 1Khz de frecuencia se obtiene una señal de salida de amplitud cercana a 3V de amplitud con a misma frecuencia. Lo que da una ganancia potencial de aproximadamente 28 dB. 28 Seguidamente se presenta la toma obtenida experimentalmente sobre la ganancia de tensión: Figura 4-8: Ganancia de tensión experimental Como se puede apreciar en la figura 4-8, al alimentar el amplificador con una señal de entrada con una amplitud de 100mV y 1Khz se obtiene una señal de salida de amplitud 2.6V a la misma frecuencia que la entrada. Comparando las figuras 4-8 y 4-7 se puede observar que los datos obtenidos experimentalmente están acordes con los simulados; dándole validez a los datos obtenidos en el laboratorio. 29 Con respecto al desfase entra las señales de entrada y salida se presenta la figura 4-9 a continuación: Figura 4-9: Desfase entre las señales de entrada y salida La figura 4-9 deja claro que las dos señales están en fase. Por ende se concluye que en el amplificador no hay un desfase entre la señal de entrada y la señal de salida. 30 4.5 Barrido de frecuencia Se presenta el barrido de frecuencia del amplificador de potencia obtenido por medio de la simulación: Figura 4-10: Barrido en frecuencia simulado Como se puede apreciar en la figura 4-10 la forma del gráfico es de un filtro paso banda, acorde a la teoría. La idea de este filtro es atenuar las frecuencias no audibles para el oído humano. Para el amplificador en estudio se amplió un poco el rango de frecuencias de [20200K], esto para darle profundidad al sonido. 31 Se presenta ahora el barrido de frecuencias obtenido experimentalmente: Figura 4-11: Barrido de frecuencias obtenido experimentalmente Comparando las figuras 4-11 y 4-10 se aprecia la similitud entre éstas, por lo que su respuesta en frecuencia es muy similar a la deseada. Se resalta que el amplificador implementado fue todo un éxito, ya que a través de las diferentes pruebas realizadas, su comportamiento siempre estuvo muy similar al comportamiento deseado. 32 4.6 Impedancia de entrada: Para la medición de este parámetro se utilizó el siguiente esquemático presentado en la figura 4-12: Figura 4-12: Circuito para obtener la impedancia de entrada experimentalmente La idea es poner en serie un potenciómetro con el amplificador, esto para alimentar el circuito con una señal de entrada, generalmente sinodal, de frecuencia adecuada; para seguidamente medir la tensión obtenida en el amplificador (RX_Amplificador en la figura 4-12) al variar el potenciómetro. Entones, cuando se obtiene una señal con la mitad de la amplitud de la señal de entrada, se tiene el valor de la impedancia de entrada del amplificador en el potenciómetro. Al realizar el procedimiento detallado anteriormente se obtuvo el siguiente resultado, presentado en la figura 4-13. 33 Figura 4-13: Impedancia de entrada experimental La señal de entrada fue una sinodal de frecuencia mayor a 200Hz, aproximadamente 330Hz y de amplitud 20Vp-p; por lo que al obtener una señal de 10Vp-p se logró un valor de 12.67K Ω . El valor experimental varia con respecto al obtenido analíticamente, ya que es prácticamente el doble del parámetro experimental; error que se puede atribuir a la serie de aproximaciones realizadas para facilitar el cálculo del apéndice IV. Pero es un valor muy cercano al expuesto en la revista de donde se obtuvo el amplificador en estudio, concluyendo que su implementación fue muy exitosa. 34 Capítulo 5: Conclusiones y recomendaciones 5.1 Conclusiones • Los amplificadores de potencia de clase AB, a pesar de su antigüedad en el mercado, siguen siendo una de las clases más implementadas por lo fabricantes. De esta clase surgieron clases posteriores, que en realidad son mejoras a la clase AB, que dan como resultado un amplificador de audio de muy buena calidad sonora; concluyendo que la clase AB es la base de donde evolucionaron otras. • La topología de tres etapas de un amplificador de potencia es una de las más utilizadas e implementadas, ya que de éstas se pueden obtener destacables ventajas en lo que se refiere a estabilidad del circuito, una muy buena lineabilidad, una muy baja distorsión, una muy buena eficiencia, entre otras. • Los transistores “Thermal Track” son una solución muy innovadora al problema de la distorsión de cruce. Logrando que la tensión entre ánodo-cátodo del diodo sea de un valor muy cercano a la tensión base-emisor del transistor. Consiguiendo así que la distorsión sea despreciable, dando como resultado un buen rendimiento en el campo fiabilidad del amplificador. • Se logró implementar un amplificador de audio de un comportamiento muy fiel a la teoría. Esto se refleja en los valores obtenidos experimentalmente, los cuales coinciden con lo expresado en la teoría y en las simulaciones. 35 5.2 Recomendaciones • En la implantación del circuito se debe tener sumo cuidado a la hora de alambrarlo. Debido que su gran tamaño aumenta la complejidad, haciéndose más difícil de analizar a la hora de encontrar errores. Se recomienda hacer uso de una tarjeta de prototipos de buen tamaño y hacer un buen completo de ella. • Cuando se realicen medidas al circuito verificar que ningún componente este generando algún corto, debido a que se puede generar un pico de corriente que puede alterar o afectar el funcionamiento de algún componente, especialmente a los transistores de propósito general. • Recordar siempre limitar la corriente de corto circuito en las fuentes del laboratorio. Esto porque, de lo contrario cuando se produzca algún corto se puede generar la perdida de algún componente. Mientras que una limitada corriente de corto circuito puede evitar la pérdida de algún componente, al surgir algún altercado. • Cuando se le introduzca la señal de entrada al amplificador, se debe conocer de antemano un aproximado de cuanta corriente de salida se va a obtener. Esto para evitar el sobrecalentamiento del conductor (que deber de ser de un calibre adecuado) , una disipación de potencia muy alta en los transistores (altas temperaturas) de la etapa de salida y para evitar daños físicos a la tarjeta de prototipos. 36 Bibliografía [1]”Electronic Circuits Design For Beginners” en: http://knol.google.com/k/electroniccircuits-design-for-beginners-chapter-8#. Consultado en Agosto 23, 2011. [2]David A. Kaplan. (1999). “Los Silicon Boys”. EMECE Editores. [3]José María Drake Moyano. (2005). “Amplificadores de potencia”. UNIVERSIDAD DE CANTABRIA. [4]J. I. Huircan. (2005). “Amplificadores de Potencia, Conceptos básicos ”. [5]Foros De Electrónica. “Diseño de Amplificadores de Potencia” en: http://www.forosdeelectronica.com/f31/diseno-amplificadores-potencia-12212/. Consultado en Agosto 23, 2011. [6] Boylestad, R. (1997) Electrónica: Teoría de Circuitos. 4ª edición. Prentice Hall. [7] Schilling, D. (1991) “Circuitos Electrónicos: Discretos e Integrados.” 1ª edición. McGraw-Hill. [8]Mark Busier. (2005) APPLICATION NOTE “ThermalTrakt Audio Output Transistors”. ON Semiconductor. [9] Nueva Electrónica. “Amplificador Estero 110W” Volumen Nº 300. (2010). [10] G. Randy Slone. (1999). “High-Power Audio Amplifier Construction Manual”. 1ª edición. McGraw-Hill. [11] Douglas Self. (2006) “Audio Power Amplifier Desing Handbook”. 4ª Edición. Newnes. 37 [12] Gustavo A. Ruiz Robredo. (2001) “ELECTRONICA BASICA PARA INGENIEROS ”. 1ª edición. Servicio de Reprografía Facultad de Ciencias Universidad de Cantabria. [13]Paul R. Gray /Robert G. Meyer. (1955). “Análisis y Diseño de Ciruitos Integrados Analogicos”. 3 edición. Prentice Hall. [14] Hojas del fabricante, encontradas en el catalogo de Datashhet en: http://www.datasheetcatalog.com/. Consultado en Agosto 23, 2011. 38 Apéndices Apéndice I 1.1 Clase A: Un amplificador de potencia estará funcionando en clase A, cuando la tensión de polarización y la amplitud máxima de la señal de entrada posean valores tales que, la corriente por el colector fluya continuamente en todos los dispositivos de salida; durante todo el ciclo de la señal. O sea, los transistores siempre estarán consumiendo corriente. El transistor se polariza en una zona de respuesta lineal, con capacidad de responder a señales de cualquier polaridad. [4] Su principal ventaja es su operación lineal, por consecuencia su distorsión armónica es una de las más bajas en los amplificadores de potencia. Esta se manifiesta en una alta fidelidad sonora de la señal de entrada. En contra parte, su principal desventaja es la alta disipación de temperatura. Esta causa la eficiencia más baja en todos los tipos de amplificadores de potencia; eficiencia máxima que ronda el 50%. A continuación en la figura 5-1 se presenta un circuito de un amplificador de potencia Clase A: Figura 5-1: Esquemático de un amplificador Clase A [5] 39 1.2 Clase B La clase B tiene la característica de que la corriente sólo fluye en un semi-ciclo de la onda de entrada, donde es amplificada. Durante el otro medio ciclo, la señal no es amplificada. Para conseguir un aumento considerable del rendimiento, se configura para que los elementos activos (Transistores) trabajen en un semi-ciclo de la onda cada uno, es decir, conduzcan 180°. A esta forma de trabajo también se le conoce como Push-Pull. La idea es trabajar con un par de transistores que se complementen mutuamente. El punto Q se ubicará aproximadamente en el punto de corte en ambas rectas de carga, la de corriente continua y la de señal de entrada. Las ventajas que ofrece el funcionamiento en clase B son un menor consumo de corriente y un mayor rendimiento de aproximadamente un 78.5%. Figura 5-2: Concepto base para el funcionamiento de la clase B [3] En la figura 5-2 se observa el concepto básico de la clase B. Donde la suma de las corrientes de los 2 transistores, da la amplificación de la corriente de entrada. 40 1.1.1 Configuración en simetría complementaria Figura 5-3: Configuración en Simetría complementaria [7] En la figura 5-3 se muestra un amplificador de clase B en simetría complementaria. Esta configuración no precisa el uso de transformadores. Ventaja de gran importancia, debido a que le quita peso al circuito y abarata el costo. Se usan transistores NPN y PNP para que cada uno de ellos conduzca en un semi-ciclo. Cuando la tensión de la señal de entrada es positiva, T1 (NPN) conduce, mientras que T2 (PNP) está en corte. Cuando la tensión es negativa se intercambian los papeles. La corriente en la carga tendrá la siguiente forma: [7] I L = I C1 − I C 2 ( 1-1) Sus ventajas con respecto a otras configuraciones son la eliminación del transformador y no necesita señales de entrada desfasadas 180º. Entre sus desventajas es el uso de dos fuentes de alimentación una positiva y otra negativa. 41 1.1.2 Distorsión de cruce por cero: En los circuitos prácticos, no se usa el verdadero funcionamiento en clase B debido a la excesiva distorsión que puede producirse. Los transistores no son lineales cerca del corte de corriente debido al umbral de tensión que poseen. Esto se produce por la tensión base emisor de los transistores. Recordando que los transistores están conformados de un par de diodos y que tienen que superar un potencial de aproximadamente 0,7v para conducir. Como esta tensión depende de la señal de entrada Vi, durante todo el tiempo en que la señal, tenga un valor menor a 0,7v, los transistores Q1 y Q2 estarán en la zona de corte, generando en la salida una tensión de cero volts, y produciendo una distorsión en el cruce por cero y por ende distorsión en la señal. [5] Figura 5-4: Distorsión por cruce por cero [5] Debido a este problema, los amplificadores clase B tuvieron que migrar a otro tipo de clase. Para solucionar este problema, se creó la clase tipo AB 42 Apéndice II 2.1 Distorsión Armónica: La distorsión armónica se define como cualquier deformación, o coloración, causados por la generación artificial de los armónicos. Se supone que la distorsión armónica siempre será asociada a las no-linealidades del circuito. La distorsión armónica se produce cuando la señal de salida de un sistema no equivale a la señal que entró en él. Esta falta de linealidad afecta la forma de onda, porque el equipo ha introducido armónicos que no estaban en la señal de entrada. Puesto que son armónicos, es decir múltiplos de la señal de entrada, esta distorsión no es tan disonante y es más difícil de detectar. En todo sistema de audio siempre se produce una pequeña distorsión de la señal, dado que todos los equipos actuales introducen alguna no linealidad. [10] La distorsión armónica no siempre implica pérdida de calidad. De hecho, la distorsión se considera un efecto de sonido imprescindible para ciertos géneros musicales (básicamente rock) y así, se suele saturar artificialmente la señal básica producida por ciertos instrumentos (como guitarras eléctricas). En este sentido, la distorsión apareció en la música primero como consecuencia indeseada de la saturación de las etapas del sistema de amplificación, y después se crearon unidades de efecto que producían artificialmente ese efecto, con independencia del equipo utilizado. Al hablar de distorsión armónica, normalmente se hace referencia a la llamada distorsión armónica total (THD, por sus siglas en inglés “Total Harmonic Distortion”), que es precisamente, la cantidad de armónicos que el equipo introduce y que no estaban en la señal original. Para normalizar las medidas. La distorsión armónica total nunca debe estar por encima del 1%. De estarlo, en lugar de enriquecer la señal, la distorsión empieza a desvirtuarla y el sonido resultante empieza a dejar de parecerse al original, aunque se utilizan distorsiones superiores con objetivo artístico. 43 En el amplificador típico la THD se piensa a menudo que se debe simplemente a la naturaleza de la clase-B de la etapa de salida, ya que pierde linealidad cuando el factor de retroalimentación cae al aumentar la frecuencia. Esto es, sin embargo, es cierto cuando todas las demás fuentes de distorsión han sido eliminadas. En la gran mayoría de los amplificadores comerciales, la realidad es más compleja, ya que las etapas de pequeña señal (las primeras dos etapas) puede generar distorsiones importantes por su cuenta. 2.2 Retroalimentación: El uso de la retroalimentación negativa en los amplificadores es de suma importancia ya que, trae una serie de beneficios muy importantes. La retroalimentación negativa estabiliza la ganancia del amplificador contra los cambios en los parámetros de los dispositivos activos, debido a las variaciones del potencial de alimentación, cambios en la temperatura o envejecimiento de los dispositivos. Además permite al diseñador modificar las impedancias de entrada y salida del circuito en cualquier forma. También reduce la distorsión de la forma de onda de la señal que produce. Algunas de las desventajas que trae la retroalimentación negativa son: reduce la ganancia del circuito, por lo que a menudo se compensa añadiéndole una etapa adicional, un preamplificador. Y por último la tendencia que ocurran oscilaciones en el circuito, se le debe tener suma atención para evitar la inestabilidad, usualmente se le agregan capacitores que ayuden a la compensación del circuito, para mejorar la estabilidad. [13] A continuación se detallan los diferentes tipos de retroalimentación que se dan en este tipo de arquitectura. 44 Figura 5-5: Tipos de retroalimentación:[10] En la figura 5-5 se han representado a la arquitectura de tres etapas, cada una con la simbología de amplificador operacional; donde la etapa de entrada se ha representado por el rótulo A1, la etapa de amplificación de tensión con A2 y finalmente la etapa de salida con A3. La figura 5-5, prácticamente se da entender por sí sola, pero para no dejar ninguna duda se explicara a continuación. La figura 5-15 (a) muestra la retroalimentación local, la cual se lleva a cabo de manera aislada entre la misma etapa. La figura 5-15 (b) muestra que una retroalimentación global es cuando, se toma la salida del circuito total (etapa de salida), conformado por las tres etapas, y se retroalimenta a la entrada del mismo (etapa de entrada). Y por último en la figura 5-15 (c) se muestra que una retroalimentación anidada se da cuando, se toma la salida del circuito total y se retroalimenta a la entrada de las dos etapas anteriores. Esta última no se utiliza en la mayoría de amplificadores de audio. [10] 45 2.3 Retroalimentación en el amplificador de potencia El uso principal de la retroalimentación negativa (NFB por sus siglas en inglés “Negative Feed-Back”) en los amplificadores es la reducción de la distorsión armónica, la reducción de la impedancia de salida, y el aumento del rechazo de la alimentación (PSRR). En el control de la distorsión del amplificador, hay dos principales armas. La primera es hacer que la linealidad de los circuitos sea la mejor posible antes de cerrar el lazo de retroalimentación. Esto es incuestionablemente importante, pero debido a la dificultad de obtener algunos parámetros en las diferentes etapas de amplificación, se convierte en una solución poco manejable, además la experiencia ha demostrado que este enfoque es de poca efectividad. La segunda y más usada es la aplicación de la retroalimentación negativa tanto como sea posible, manteniendo la estabilidad del amplificador. En circuitos simples, nada más se aplicaba la retroalimentación negativa y ese era el final del asunto. En un amplificador de potencia típico, que normalmente se constituye de varias etapas, habrá etapas que pueden provocar un cambio de fase, y si se llegara a cerrar simplemente el lazo traería en su peor caso grandes oscilaciones, ya que en vez de obtener una señal de error, constituida de la resta entre la señal de entrada y la retroalimentada, se tendrá una suma entre ambas, si hay un cambio de fase de 180º. Asunto serio, ya que no sólo se quemará los altavoces conectados, pero también puede destruir los dispositivos de salida por el sobrecalentamiento. 46 La señal obtenida en la salida de la etapa de entrada, se invierte en relación con la señal de entrada del amplificador. La etapa de amplificación de tensión (VAS por sus siglas en ingles,”Voltage Amplifier Stage”) la invierte de nuevo, volviendo a una cercana condición de fase cuando se aplica a la etapa de salida (OPS por sus siglas en ingles “Output Stage”). La OPS es un amplificador no inversor, por lo que la señal retroalimentada tomada de la OPS se considera que esta en fase cuando se aplica a la entrada inversora del amplificador diferencial de entrada. Refiriéndose a la figura 3-1, supongamos que el polo dominante del capacitor CC se elimina del circuito y la señal de salida no se retroalimenta. En estas condiciones, la ganancia de tensión de lazo abierto en bajas frecuencias del amplificador de potencia es el producto de la etapa de transconductancia de entrada y la transimpedancia del VAS (ganancia de tensión no se produce en el OPS). Este será un factor de ganancia muy alta, pero es difícil de predecir ya que aproximadamente un tercio del cálculo depende del beta del transistor del VAS, el cual puede cambiar muy fácilmente. Como en cualquier circuito amplificador, la ganancia de tensión de lazo abierto puede variar con respecto a la frecuencia. El rango de frecuencia donde la ganancia de lazo abierto del circuito se mantiene constante se llama la región de baja frecuencia. La región encima de esta, donde la ganancia disminuye de forma constante por un valor de 6 dB por octava, se conoce como la región de alta frecuencia. La frecuencia de ruptura en la que el amplificador pasa de región de baja frecuencia a la región de alta frecuencia se denomina frecuencia de polo dominante, normalmente abreviado como PI. . 47 El factor que controla la frecuencia de PI es la capacitancia de Miller de las etapas que contienen transistores. Sin la ayuda de CC, el factor de ganancia de tensión interactúa con el efecto de la capacitancia de Miller en las frecuencias altas produciendo una ganancia de tensión y cambio de fase suficiente para causar una oscilación sostenida, si se incorpora cualquier retroalimentación. La oscilación auto-sostenida resulta de un cambio de fase excesivo en el lazo de retroalimentación que coloquialmente se conoce como la oscilación de Nyquist. La corrección de los problemas de cambio de fase y por lo tanto de estabilidad se llama estabilidad de Nyquist; la función principal del capacitor de compensación CC es disminuir la frecuencia PI para que, la ganancia de tensión caiga por debajo la unidad antes de provocar un cambio de fase suficiente para inducir la oscilación. Una buena estabilidad es el resultado consecuente. Este método de compensación que se conoce como compensación de Miller polo dominante. La cantidad de retroalimentación negativa aplicada debe ser maximizada en todas las frecuencias de audio para obtener una muy buena linealidad, y el único límite es obtener una estabilidad confiable en altas frecuencias. En teoría de control clásica, la estabilidad de un lazo se indica por su margen de fase y su margen de ganancia. Estos conceptos no son muy útiles en el trabajo de amplificadores, donde muchas de las constantes de tiempo significativas son vagamente conocidas. En la práctica, se deberá consultar diferentes criterios para determinar un factor de retroalimentación que de una estabilidad fiable. Usualmente cuando se utiliza la convencional arquitectura de 3-etapas, 30 dB en la retroalimentación globales a los 20 kHz es segura. 48 Apéndice III Arquitectura del amplificador En la presente sección se desarrollará un análisis y la teoría de la composición de un amplificador de audio. Los amplificadores de potencia (audio) tienen diferentes arquitecturas. Estas han venido mejorándose para obtener resultados cada vez más satisfactorios en el campo del audio, como lo son la eficiencia, la distorsión de altas frecuencias, linealidad, estabilidad, entre otras. Muchos experimentos e investigaciones se han hecho para el desarrollo de la mejor topología de amplificador de audio, y una de las clásicas y todavía en uso, sin lugar a dudas, es la topología de tres etapas desarrollado por el Sr. Lin, de la RCA en 1956. La cual se muestra de manera simplificada en la figura 5-6 [10] Figura 5-6: Arquitectura de 3 etapas [10] 49 La primera etapa es un amplificador de transconductancia, que recibe una señal de tensión en la entrada y la amplifica en una señal de corriente, la cual se aplica a la entrada de baja impedancia de la segunda etapa (VAS). Esta primera etapa casi siempre está compuesta de un amplificador diferencial, debido a la conveniencia de tener una entrada de inversión para la aplicación de una retroalimentación negativa. La primera etapa que comúnmente se llama la etapa de entrada. La segunda etapa es un amplificador de transimpedancia. Se recibe la señal de corriente de la etapa de entrada y la convierte en una señal de tensión de alto nivel, proporcionando además una óptima estabilidad. Como una cuestión de convención, la segunda etapa recibe automáticamente un gran factor de retroalimentación negativa local y esta ventaja aumenta la linealidad de la señal (para más información referirse al apéndice II). La segunda etapa es comúnmente conocida como la etapa de amplificación de tensión (VA o VAS). La tercera etapa es un amplificador de corriente. Recibe la señal de alto potencial de la etapa de VAS y proporciona una ganancia de tensión cercana a la unidad y alta corriente de salida, la cual alimenta el altavoz. Conocida comúnmente como la etapa de salida (OP u OPS). [10] 50 3.1 Etapa de entrada En la presenta sección se detallara la composición de una etapa de entrada actual. Se pretende dar una idea de la utilidad de sus componentes, analizándolos por separado. Figura 5-7: Etapa de entrada típica.[11] En la figura 5-7 se presenta una etapa de entrada típica de un amplificador de audio. Se pueden distinguir tres componentes de esta. Primeramente la parte de mayor importancia es el amplificador diferencial. Los otros dos componentes la fuente de corriente y el espejo de corriente se colocan para mejorar la funcionalidad del primero. Se detallara a continuación cada una de las partes analizándolas por separado para poder entender su función en conjunto. 51 3.1.1 Espejo de Corriente: Un espejo de corriente es una configuración con la que se pretende obtener una corriente constante, esto es, una fuente de corriente. La forma más simple de una fuente de corriente está formada, por un resistor y dos transistores que tienen la misma tensión VBE. Figura 5-8: Espejo de corriente [12] Tal como se muestra en la figura 5-8, el transistor Q1 está operando en modo diodo (voltaje colector-base sea cero) y por ello en numerosas ocasiones se puede ver representado según el esquema de la figura 5-8(b). Ambos circuitos se comportan como una fuente de corriente de valor Io. Para mayor detalle sobre su análisis referirse a punto 13 de la bibliografía. 52 3.1.2 Fuentes de Corriente Son circuitos usualmente hechos a base de transistores; son ampliamente utilizadas en circuitos electrónicos integrados como elementos de polarización y como cargas activas en etapas amplificadoras. Un ejemplo de una fuente de corriente simple el espejo de corriente, analizado anteriormente. Las fuentes de corrientes en polarización resultan más insensibles a variaciones de las tensiones de polarización y de la temperatura, y son más económicas que los elementos resistivos en términos de área de ocupación, especialmente cuando las corrientes son bajas. En el audio se usan como complementos y mejoras del par diferencial. Seguidamente se estará comentando las configuraciones más usadas en el campo de audio.[11] Figura 5-9: Fuente de corriente constante [10] 53 La Figura 5-9 ilustra una forma más común de la fuente de corriente constante. Incorpora un par diodos polarizados directamente en serie DI y D2, como los elementos de regulación de tensión. Dl y D2 suministran el flujo de corriente directa de la resistencia RS. La corriente de emisor del transistor Q1 es: [11] VD1 + VD 2 − VBE 0.7 + 0.7 − 0.7 7 = = ≈ 4.6mA RE 150 1500 (3.1.2-1) Como se ilustra en la figura 5-9, el potenciómetro VR1 y la resistencia R1 representan la carga variable de la fuente corriente constante. Las variaciones de la corriente de salida de la fuente (Corriente de colector Q1) son muy pequeñas; esto porque la corriente de colector es prácticamente igual a la corriente de emisor; y esta sólo dependerá del valor de RE. [11] El valor de la resistencia de RE puede ser alterado para proporcionar casi cualquier corriente deseada, con un valor mínimo práctico de aproximadamente 50 ohms (donde la relación RE / Ic se convierte en no-lineal). RE también se puede sustituir por un potenciómetro (conectado como reóstato) en caso de necesitar cambiar la corriente de salida de la fuente de corriente constante, de forma sencilla. Aunque la fuente de corriente constante de la figura 5-9 está diseñado para utilizar la caída de tensión de los dos diodos, pero se puede utilizar cualquier elemento que proporcione una tensión de constante, como LED, o diodos zener. En caso de la selección del transistor se puede utilizar cualquier tipo de BJT, siempre que las condiciones del circuito no excedan los parámetros del transistor. [11] 54 Figura 5-10: Fuente de corriente Mejorada [10] La figura 5-10 representa un enfoque diferente para la construcción de una fuente de corriente constante, se incorporan un transistor más y varias resistencias. Cuando la fuente alimentación se aplica por primera vez, el flujo de corriente fluye por RC2, RC1, la unión base-emisor de Ql, y RE. Cuando el flujo de corriente a través de RE crea una caída de tensión suficiente para encender Q2 (alrededor de 0,67 voltios), Q2 empieza a dar corriente a RC2 y RC1. La corriente de colector de Q2 empieza a "robar" el flujo de corriente de la base de Ql, esto se da en proporción a la caída de tensión en RE. Si la tensión en RE trata de aumentar, el Q2 robara más corriente de la base de Q1, manteniendo la tensión constante de RE. Si ocurre lo contrario y el voltaje de RE trata de caer, Q2 robará menos corriente de Q1 logrando una vez más, que la tensión en RE se mantiene constante. En efecto, la caída de tensión en RE está firmemente regulada para ser aproximadamente igual a la de Vbe de Q2. La caída de tensión en RB puede considerarse insignificante a efectos prácticos. [11] 55 La fuente de corriente constante de la figura 5-10 es un diseño mucho mejor que el anteriormente detallado. La acción del transistor dual reduce en gran medida las pequeñas variaciones en la regulación de la tensión inherente a los diodos polarizados directamente o diodos zener. Desde la perspectiva del diseño, los valores de componentes para la fuente de corriente de la figura 5-10 son fáciles de determinar. La tensión de la fuente, entre la suma de las resistencias RCl y RC2 da una corriente de aproximadamente la mitad de la corriente deseada en la salida de la fuente de corriente constante. El cálculo de la RE es el mismo que el descrito para el circuito de la figura 5-9. El valor de la RB es no crítico y puede permanecer en torno al 1 k para casi cualquier aplicación de entrada. Los valores prácticos de la Cl capacitor puede variar de 2,2uA a alrededor de 47 uA. [11] 3.1.3 Amplificador diferencial (Par diferencial) Es el circuito más importante de la etapa de entrada. Los anteriores circuito analizados, complementan el trabajo del par diferencial. En la figura 5-11 se muestra un amplificador diferencial típico. 56 Figura 5-11: Configuración típica del amplificador diferencial [12] Las ecuaciones que muestran la relación entre las corrientes de salida y la tensión diferencial están dadas por [13]: ic1 = ic 2 = iEE Vid − VT 1+ e iEE 1+ e Vid VT (3.1.3-1) Note que para diferencias de tensiones de entrada mayores a varios cientos de milivolts, las corrientes de colector se convierten en independientes dado que toda la corriente estará fluyendo en uno de los transistores. Sólo para diferencias de tensión menores a alrededor de 50 mV, el circuito se comportará en forma aproximadamente lineal. 57 En las anteriores expresiones puede verse claramente que las corrientes de colector dependen directamente de la corriente fijada por la fuente (IEE) y de la diferencia de tensión aplicada a las bases (tensión diferencial de entrada). Si la señal diferencial es nula ambas corrientes son idénticas e iguales a la mitad de la corriente fijada por la fuente (IEE). [13] Figura 5-12: Corrientes de un par diferencial en función del voltaje diferencial [12] En las curvas de transferencia de la figura 5-12 se puede observar que las características son lineales en una zona centrada alrededor del punto de trabajo, en el cual la pendiente es máxima. Esta pendiente define la ganancia de transconductancia efectiva del amplificador que depende del valor de la corriente IEE suministrada por la fuente de corriente constante y queda determinada por la siguiente expresión: m = Gm = αF I EE 4VT con αF ≈ 1 (3.1.3-2) 58 Con la finalidad de aumentar el rango de tensión de entrada en el cual el par acoplado se comporta de manera similar a un amplificador lineal, frecuentemente se incluyen resistores de degeneración en serie con los emisores de los transistores. Además este es un ejemplo de una retroalimentación local, por lo cual da todas las ventajas de la retroalimentación negativa. [13] Las ventajas del uso de un par diferencial en la etapa de entrada de un amplificador es por lo general el bajo offset en DC, debido a la cancelación de las tensiones VBE. Además tiene la ventaja importante de que su corriente estacionaria no tiene que fluir a través de la red de realimentación. El par diferencial tiene la gran ventaja de que su característica de transferencia es matemáticamente muy predecible. La corriente de salida está relacionada con la diferencia de tensión de entrada, relación que se puede ver en la ecuación 3.1.3-1. Además el exacto balance DC del par diferencial es esencial para los amplificadores de potencia; ya que las desviaciones más pequeñas de Ic en el par afectan gravemente la cancelación del segundo armónico.[11] Es por estos motivos que se usan los espejos de corriente, ya que la corriente de la fuente de corriente constante se divide por igual entre las dos piernas del espejo de corriente (es decir, fuerza a las dos corrientes de colector ha estar muy cerca de la igualdad, dando la cancelación correcta del segundo armónico). En otras palabras, un espejo de corriente equilibra el flujo de corriente eléctrica a través de dos vías de corriente desequilibrada. También hay menos DC offset debido a la desigualdad en las corrientes de base que fluyen a través de resistencias de entrada y de retroalimentación 59 Pero si al incluir un espejo de corriente se siente que la distorsión de alta frecuencia necesita una mayor reducción. La no-linealidad del transistor puede atribuirse a la nolinealidad de la resistencia interna del emisor Re; por lo que se puede reducir el valor de esta, mediante el aumento de la corriente de cola y por ende la corriente de colector. Se debe tener en cuenta que al aumentar la corriente de cola aumenta la ganancia, pero al aumentar la ganancia podría verse afectada la estabilidad del circuito, por lo que es conveniente volverla a su valor inicial (de lo contrario el capacitor del VAS tendría que ser aumentado en forma proporcional para mantener la estabilidad). Esto se logra agregando la resistencia de degeneración, para que sustituya la parte que falta de la resistencia interna del transistor. En resumen lo que se hace para reducir aún más la distorsión es aumentar la corriente de los emisores, pero esto afectaría a la ganancia, por lo que se agregan resistencias externas para volver a tener la Re original, la relacionada con la ganancia deseada. [11] La resistencia interna de un transistor usualmente cumple con esta ecuación: Re = 25 IC con I C en mA (3.1.3-3) En la figura 5- se muestra un ejemplo de lo comentado anteriormente. Ya que inicialmente (a) se tiene I c = 1.35mA, Re = I c = 600 µA, Re = 25 ≈ 42 Ω . 0.6 Y al aumentar 5-13(b) 25 ≈ 20Ω, por lo que el valor de la resistencia de degeneración 1.35 será de RE = 22Ω . 60 Figura 5-13: Antes y después de la incorporación de RE. [11] Si se busca mejorar aun más la linealidad, existen varias técnicas, de las cuales una de la más usada debido a su menor complejidad y resultados es la de pares de retroalimentación complementaria (CFP por sus siglas en inglés). Cada vez que sea necesario incrementar la linealidad de un circuito, a menudo es un buen método incrementar el factor de retroalimentación local, ya que este tiene poco efecto sobre la estabilidad global del lazo. Un método fiable es reemplazar los transistores de entrada con unos CFP, como se muestra en el escenario de la figura 5-14. [11] Figura 5-14: Pares de retroalimentación complementaria [11] 61 Un compromiso necesario en el circuito de CFP, es el valor de Rc, que establece la proporción de la corriente remanente que pasa por los dispositivos NPN y PNP a cada lado del escenario. A mayor valor de Rc da una mejor linealidad, pero más ruido, debido a la menor corriente de colector en los dispositivos NPN que son las entradas de la etapa de entrada, 2,2k es un buen compromiso. [11] En conclusión la etapa de entrada constituida por un par diferencial no sólo proporciona la forma más sencilla de hacer un amplificador acoplado en DC con una tensión offset pequeño pero también puede cancelar totalmente la distorsión del segundo armónico que sería generado por una etapa de entrada de un solo transistor. Una condición esencial para esto es que el par debe estar perfectamente equilibrado, por lo que la elección de los componentes asociados a este fin debe ser de suma importancia. 3.2 Etapa de amplificación de voltaje (VAS). Como su nombre lo indica, la VAS es el responsable de toda la ganancia de tensión dentro de un amplificador de potencia. La VAS recibe una señal de corriente amplificada de la etapa de entrada y la convierte en una tensión de gran señal que se aplicará a la OPS. A medida que aumenta la frecuencia por encima del PI, la impedancia de entrada y salida del VAS comienza a caer como cae la reactancia capacitiva del capacitor de polo dominante. La disminución de la impedancia del VAS tiene un efecto mínimo en la capacitancia de Miller dentro de las etapas de entrada y salida, forzando al capacitor de polo dominante a convertirse en la principal influencia capacitiva en todo el amplificador. Por lo tanto, las variables de compensación para estabilidad de Nyquist y linealización óptima se reducen a los efectos combinados de la transconductancia etapa de entrada, la ganancia de tensión de la VA, y el valor de un capacitor (el de polo dominante CC). 62 Asumiendo que la etapa de entrada se ha llevado hasta sus límites, una compensación óptima y linealización se simplifica a dos variables: la ganancia de potencial del VAS y el valor del condensador de polo dominante. La ganancia de tensión debe ser tan alta como sea posible, sin añadir complejidad innecesaria o inestabilidad al circuito. El valor óptimo de CC es elegido para proporcionar una buena estabilidad y el máximo aprovechamiento de la NFB global. Una etapa VAS bien diseñada contribuyen relativamente poco con la distorsión total de un amplificador, la principal razón es porque en bajas frecuencias (LF, por sus siglas en inglés “Low Frequency”), la retroalimentación global linearizará todo el amplificador, mientras que en altas frecuencias (HF, por sus siglas en inglés “High Frequency)” el VAS es linealizado por NFB local a través del capacitor de polo dominante (Conocido como CC o CDOM). 3.2.1 VAS: La figura 5-15 da una idea del funcionamiento del VAS: Figura 5-15: Operación del VAS [11] 63 G representa una fuente de corriente cuyo valor es controlado por la tensión diferencial entre Rin y Rf2, y representa la transconductancia diferencial de la etapa de entrada, donde la Rin será el potencial de entrada y Rf2 la tensión retroalimentado. Luego F representa el transistor del VAS, que es una fuente de corriente produciendo una corriente beta veces lo que fluya a través del amperímetro VA. El valor de la beta, representa la ganancia de corriente, como es usual, modelando la relación entre la corriente de colector y la corriente de base. Rc representa la impedancia total de colector del VAS, un valor típico es de 22 k. El total de la ganancia de tensión claramente depende linealmente de beta. La derivación que se da en el circuito a través de CDOM representa la retroalimentación local, la cual establece la ganancia esencial en HF que controla la estabilidad de Nyquist. La ganancia en LF por debajo de la frecuencia de polo dominante sigue siendo variable (y por lo tanto también el polo dominante), pero en última instancia, es de poca importancia si existe un adecuado factor de retroalimentación para la linealización total en HF relacionado con el valor de CDOM esto ya que, será muy poco probable que haya problemas en LF, donde la ganancia es mayor. 3.2.2 Configuraciones típicas del VAS En la presente sección se describirán tres tipos de configuraciones típicas de un VAS. Cada una de estas busca un objetivo en común, el aumentar la ganancia de lazo abierto del VAS, solo que cada una de estas lo hace de un forma diferente. Es importante que la ganancia local de lazo abierto del VAS sea alta, para que el VAS puede ser linealizado. Una forma de asegurar la suficiente ganancia del lazo es el uso de una carga activa para aumentar la impedancia de colector efectiva en el transistor y así aumentar la ganancia de tensión en bruto. Para esto se puede usar la técnica del bootstrapping o una fuente de corriente, aunque la fuente de corriente es más confiable, y es la opción habitual para los amplificadores de alta fidelidad o profesional. 64 Figura 5-16: Diferentes configuraciones del VAS En la Figura 5-33 (a) VAS con una carga de la fuente de corriente: Este circuito representa un diseño muy común, con una fuente de corriente constante, en lugar de una resistencia pasiva. La fuente de corriente actúa como una resistencia activa y proporciona un máximo aprovechamiento del parámetro beta del transistor mientras se aumenta la capacidad de generación de corriente del VAS. La desventaja de este circuito es que el transistor debe ser capaz de manejar alto voltaje (capaz de soportar la suma de los voltajes alimentación), y sería preferible contar con un factor de ganancia más alta que la que pueda proporcionar un solo transistor. Figura 5-33 (b) bootstrap en el VAS Bootstrapping es otra técnica de carga activa, comparable a la utilización de una fuente de corriente constante. Es menos costoso que incorporar una fuente de corriente, pero es más difícil de optimizar. Bootstrapping requiere la retroalimentación de voltaje de la OPS, en consecuencia, está a merced de las variaciones resultadas en la salida por desviaciones en la impedancia de los altavoces. 65 Figura 5-33 (c) Darlington VA etapa: Esta configuración ayuda a disminuir la distorsión del VAS, aunque ya es muy poco influyente, pero es una forma de mejorar aun más el amplificador. La configuración utiliza una fuente de corriente constante, como la configuración de la figura 5-33 (a). Tiene la ventaja de mejorar la retroalimentación local que se da a través de CC, esto porque, si se recuerda la ganancia de lazo abierto del amplificador es el producto de la transconductancia la etapa de entrada, el beta del transistor del VAS y la impedancia de colector Rc: Lf gain = gm × β × Rc (3.2.2-1) Los dos últimos factores representan la ganancia de VAS y por lo tanto la cantidad de NFB local, entonces esta puede ser aumentada mediante el aumento de cualquiera de los dos. Tenga en cuenta que siempre que el valor del CDOM sigue siendo el mismo, el factor de retroalimentación global en HF no ha cambiado y la estabilidad que no se ve afectado. El beta eficaz del VAS puede aumentar considerablemente mediante la sustitución del transistor del VAS con un Darlington, en otras palabras, poner un emisor-seguidor antes. Agregar una etapa extra al amplificador requiere de un análisis ya que, si la adición de esta introduce un cambio de fase extra, la estabilidad en lazo global puede sufrir; pero en este caso, la nueva etapa se encuentra dentro del lazo (CDOM) y hay poca probabilidad de que se dé este problema. El transistor del VAS, es capaz de suministrar más corriente al OPS. La resistencia en el emisor del transistor seguidor es para, la estabilización en DC, con valores típicos que van desde alrededor de 1 k a 100 ohmios. En esta sección se muestra cómo los arduos esfuerzos para optimizar la etapa de entrada pueden ser mejor aprovechadas por el VAS. El VAS está encargado de toda la ganancia de voltaje de un amplificador, además es una etapa de suma importancia en el tema de la estabilidad; que incluye el tema de los dos tipos de retroalimentación que se dan en el amplificador. El VAS no genera altas distorsiones pero es conveniente trabajar para reducirlas. Para mayor detalle sobre el tema del VAS referirse a los puntos 10 y 11 de la bibliografía 66 3.3 Etapa de Salida No hay duda de que la etapa de salida (OPS) de una arquitectura de tres etapas presenta el mayor obstáculo en la búsqueda de la perfección en el sonido. Hay muchas opciones de diseño, tipos de clase, y existen diversos mecanismos de distorsión al considerar la elección de la topología óptima. Cada uno de estos temas podría ser perfectamente desarrollado a profundidad en un libro, pero el objetivo de esta sección y de las anteriores es dar una idea general de los temas del mundo del audio. El propósito de la OPS es recibir la tensión de alto nivel de la de salida del VAS e interconectarla a una carga reactiva de baja impedancia (es decir, un sistema de altavoces). En otras palabras, la OPS es típicamente un amplificador de corriente con ganancia de voltaje unitaria. Existen OPS que incluyen la ganancia de la tensión, pero por lo general se cree que el control de la distorsión, durante la manipulación de grandes corrientes es lo bastante complicado, para intentar generar ganancia de tensión al mismo tiempo. Además si el VAS puede proporcionar casi "sin distorsión" la amplificación de tensión de hasta cerca el potencial de alimentación (que se puede), simplemente no hay razón práctica para tratar de obtener un beneficio adicional de tensión en la OPS. Debido a que el proyecto se centra en el desarrollo de amplificador de audio tipo AB en simetría complementaria, en la presente sección se estará detallando solo OPS de tipo AB. Partiendo de los conocimientos ya expuestos en el capítulo dos. Seguidamente se pretende explicar los tipos de distorsión que se ven expuestos los amplificadores de tipo AB, para continuar con las topologías más usadas y conocidas de la etapa de salida; para finalizar con el análisis de una etapa de salida básica. 67 3.3.1 Tipo de distorsiones Las etapas de salida de tipo AB presentan tres principales tipos de distorsiones. La primera es la distorsión de cruce, ya mencionada en el capitulo uno, la distorsión de conmutación y la distorsión proveniente de las no-linealidades de las señales grandes, mejor conocida como la caída del beta. A continuación se pretende explicar que son y cuáles son sus causas; esto porque en la siguiente sección se presentará los diferentes tipos de topologías, cuáles son sus ventajas y desventajas, relacionándolas con el efecto que tienen en las anteriores distorsiones. Distorsión de cruce: Este tipo de distorsión, como ya se mencionó anteriormente, se da por la tensión base emisor necesaria para poner a conducir los diodos de los transistores. Recordando que los transistores están conformados de un par de diodos y que tienen que superar una tensión de aproximadamente 0,7v para que conduzcan. El término cruce por cero se refiere al punto en que la señal tiene un valor nulo cuando los dispositivos se encuentran en transición, en este caso, el cambio de transistor. Este tipo de distorsión no puede ser eliminado por completo (al menos, a nuestro nivel tecnológico actual), pero puede ser reducida muy eficientemente. La distorsión de cruce genera desagradables armónicos de alto orden, con al menos el potencial de aumentar en porcentaje cuando el nivel de la señal cae. La distorsión de cruce disminuye en las frecuencias bajas; esto porque la frecuencia de los transistores se ve afectada de los cambios en la amplitud de la señal salida. Tenga en cuenta que este principio no tiene nada que ver con el nivel de distorsión de cruce sólo los componentes de frecuencia asociados a ella. Regresando a los principios involucrados con NFB global, se estableció que la NFB global es mucho más eficaz en la eliminación de la distorsión en las frecuencias bajas. En consecuencia, como la amplitud de la señal de salida disminuye, el contenido de frecuencia de la distorsión de cruce cae en las regiones de baja frecuencia, las que son efectivamente eliminadas por la NFB global. 68 Una de las soluciones más usadas y efectivas es usar una red de polarización para poner a conducir a los transistores a un potencial cercano a cero. O sea, como ya se explico en el capitulo #1, montar la señal de entrada sobre componentes de voltaje directo de +0,7V y 0,7V para el par de transistores. De manera que estos empiecen a conducir para tensiones Vi > 0 y Vi < 0 y no Vi > 0,7V y Vi < 0,7V como el circuito original. La red que se implementará en el amplificador en estudio es a partir de diodos. Las ventajas ya fueron mencionadas anteriormente, por lo que concluyendo, la distorsión se disminuirá con una red de polarización a base de diodos, estos diodos estarán integrados al mismo chip, junto con los transistores. Este tipo de transistores se llaman “Themal Track” los cuales fueron detallados en el capitulo dos. Distorsión de Conmutación: Distorsión de conmutación se produce en los transistores complementarios de salida, resultado de su incapacidad para apagarse (es decir, ir al corte) lo suficientemente rápido cuando la señal de salida pasa por el punto de cruce por cero. A altas frecuencias de audio, este retraso de desconexión se puede manifestar en forma de conducción de cruce (es decir, ambos transistores de salida están conduciendo al mismo tiempo) causando un tipo de distorsión muy similar a la anterior. Por esta razón, la distorsión de conmutación es a menudo confundida con la distorsión de cruce. La diferencia, sin embargo, fácilmente se puede detectar puesto la distorsión de conmutación generalmente desaparece en las frecuencias más bajas. En casos extremos, la distorsión de conmutación puede causar un sobrecalentamiento rápido de los transistores de salida y / o destrucción de los mismos. [10] 69 Esta depende de muchas variables, en particular las características de velocidad de los dispositivos de salida y la topología de la salida. La etapa de salida debe ser capaz de polarizar inversamente las uniones base-emisor de los dispositivos de salida para maximizar la velocidad en que estos se apaguen (corte). Una segunda influencia es el valor de las resistencias de emisor, entre más bajo sea su valor más rápido la carga almacenada se podrá remover. Este problema es causado por el proceso de fabricación de los transistores, porque los transistores de salida de alta potencia debe ser capaces de controlar corrientes altas y deben tener una disipación de potencia relativamente alta. La única forma de que estas características se pueden incorporar en un transistor es aumentando el tamaño de los chips o sea el tamaño de los semiconductores internos. Desafortunadamente, esto conlleva a un incremento proporcional de la capacitancia de la unión, lo que se traduce en una lentitud de estos transistores. En una operación de clase A para una OPS, la capacitancia interna de los transistores de salida es sólo una preocupación en lo que respecta a la estabilidad. Pero en la operación de clase B, los transistores de salida se deben apagar rápidamente cuando su período de conducción cesa, o terminamos con la condición de los dos transistores de salida conduciendo simultáneamente. [10] Entre alguna de sus soluciones son la implementación de una red de desconexión, que logre maximizar la velocidad en que los transistores de salida pasen a corte. Otro tipo de solución es la reducción de las resistencias de los transistores para ofrecer una vía de descarga de menor impedancia de las cargas almacenadas en las bases de los transistores. 70 Distorsión de grandes señales (caída de Beta) Todos los transistores bipolares presentan la característica de la disminución del parámetro beta cuando se manejan corrientes de colector altas. En una OPS, esto puede causar un tipo distorsión debido a las no-linealidades de las grandes señales (LSN por sus siglas en inglés, “Large Signal Nonlinearity”) comúnmente se conocida como caída beta. En pocas palabras, esto significa que los factores de ganancia de corriente en los transistores bipolares caerán al producirse corrientes pico de salida, de ahí el nombre de "caída beta." Efecto que solo se da en los transistores bipolares, los MOSFET son afortunadamente inmune a esta deficiencia, debido a sus diferentes principios de funcionamiento. La cantidad de LSN generado es altamente dependiente de las características del dispositivo. [11] La caída del beta radica principalmente en los transistores Predriver de la etapa de salida (transistores encargados de darle un buffer extra a la OPS que reduzca los efectos de carga del VAS) en lugar de los transistores de salida. A primera vista, esto parece un poco contradictorio, ya que en los transistores de salida se verán las mayores variaciones Ic. Sin embargo, hay que recordar que la ganancia de los transistores Predriver se multiplicara por la ganancia de los transistores de salida. Puesto que los transistores Predriver son generalmente dispositivos con menor disipación y con los valores de beta más altos, son más propensos a variaciones del beta. Entre las soluciones más importantes son la elección de mejores transistores con menor caída de beta. Otra de las más usadas es duplicar los dispositivos de salida. La caída del beta depende de la corriente de colector, y si dos dispositivos de salida se conectan en paralelo, la corriente de colector se divide en dos entre ellos, por lo que la caída del Beta se reduce mucho. [10] 71 Tipos de OPS: OPS en Emisor Seguidor: Figura 5-17 ilustran el tipo más frecuente de OPS el seguidor de emisor (EF). Como es evidente, una OPS en EF es simplemente una topología Darlington complementaria. Un rendimiento óptimo para este tipo de OPS se logra con una polarización de CC de aproximadamente 2,8 voltios (red de polarización). Figura 5-17: Tipos de EF [10] En la Figura 5-17 (a), los transistores Ql y Q2 se conocen normalmente como el Predriver. Su función, como ya fue discutida anteriormente, es darle un buffer extra a la OPS para que reduzca los efectos de carga del VAS. Otra manera de decir lo mismo es que su función es "potenciar el beta" de los transistores de salida. 72 Las OPS en EF tienen una ventaja única sobre otros tipos de diseños, con respecto a la distorsión de cruce en los niveles de salida bajos. El rango de tensión de cruce de una OPS en EF es muy amplio en comparación con otras topologías. Por lo que a tensiones de salida bajas, la pendiente de potencial de salida en la región de cruce aumenta considerablemente hacia el plano horizontal, causando que los habituales armónicos de alta frecuencia de la distorsión de cruce, disminuyan radicalmente su frecuencia. Si bien esto no disminuye el nivel de distorsión de cruce, se coloca en una menor frecuencia donde lo NFB global del amplificador efectivamente los puede reducir. [10] En este tipo de OPS habrá que tener cuidado con el seguimiento térmico, ya que hay dos diferentes uniones base-emisor entre la red de polarización y la resistencia de emisor Re, llevando a diferentes corrientes y diferentes temperaturas. Por lo que el censado de temperatura debe ser muy eficiente. Problema que en la actualidad puede ser solucionado con el uso de los transistores “Thermal track”. Una desventaja de las topologías de EF con respecto a las otras topologías, es la disipación de energía en un estado de reposo, (reposo se refiere al estado de un amplificador de potencia de audio con una potencia aplicada, pero sin señal de entrada.) La red de polarización deberá polarizar cuatro uniones base-emisor, mientras que en otro tipo de topologías se reduce sola a dos. 73 La figura 5-17(b) muestra otro tipo de OPS en EF, la operación y el análisis son idénticos a los del circuito de la figura 5-17 (a) con la excepción de la red de desconexión constituida por R1 y CS. Si se asume que una oscilación de tensión positiva acaba de ocurrir, dejando una carga positiva en la base de Q3, a medida que el señal de voltaje del VAS cambie a la región negativa, la tensión en el emisor de Q2 debe estar ya 0,7V más negativa que la tensión de emisor de Q4, con el fin de superar la caída de VBE de Q4. A medida que la corriente comienza a fluir a través de RE2, también comienza a producirse una caída de tensión negativa, que se suma a la del emisor de Q2, aumentando el potencial negativo. Este potencial negativo se aplica a la base de Q3 a través de Rl y el condensador de gran velocidad de carga CS; forzando a que las cargas positivas sean rápidamente succionadas de la base de Q3, haciendo que este transistor se apague rápidamente. El efecto es recíproco en la base de Q4 durante el cambio del semi-ciclo negativo a positivo; reduciendo así la distorsión de conmutación. [10] Refiriéndose a la Figura 5-17 (a), la distorsión de conmutación se podría reducir mediante la reducción del valor de Rl y R2. Esta modificación ofrece una vía de descarga de menor impedancia a las cargas almacenados en las bases de Q3 y Q4, pero también aumenta la disipación de potencia del Predriver y acentúa los efectos de la caída de beta. 74 OPS en paralelo: Este tipo OPS no representan un nuevo tipo de configuraciones, más bien son una mejora de otros tipos de topologías como la EF; ya que brinda varias ventajas, primero aumenta la capacidad de potencia de salida del amplificador de potencia. Segundo, reduce la caída del Beta; la LSN puede reducirse eficazmente mediante la duplicación de los dispositivos de salida. Recordando que la caída del beta depende de la corriente de colector, y si dos dispositivos de salida se conectan en paralelo, la corriente de colector se divide entre los dos, por lo que consecuentemente la caída del Beta se reduce. En la figura 5-18 se muestra un ejemplo de la duplicación de los dispositivos de salida, para una de las dos topologías antes vistas. [11] Figura 5-18: Topologías en paralelo: En términos generales, existen algunas reglas básicas para los dispositivos BJT en paralelo. Más importante aún, algún tipo de NFB debe ser incorporada para asegurar que cada dispositivo de salida comparta una corriente uniforme. Resistencias de degeneración, comúnmente llamado resistencias RE, son universalmente utilizadas para este propósito. Los valores típicos de 0,1 a 1 ohm. 75 Para entender cómo las resistencias RE cumplen su tarea se detallará su comportamiento en el circuito, consultando la Figura 5-18. Los transistores Q3 y Q5 están en paralelo, utilizando 0,33 ohmios RE. A pesar de que Q3 y Q5 son del mismo tipo, las características de las tensiones Vbe probablemente variaran en pequeña cantidad. Para fines de la discusión, se supone que la diferencia de Vbe en Q3 es de 10 mV menos de Q5. Cuando una señal de potencial positivo se aplique simultáneamente a las bases de Q3 y Q5, el primer transistor empezará a conducir. Como el flujo de corriente positiva aumenta a través de la OPS rápidamente, RE1 comenzará a producir una tensión superior a RE3, ya que Q3 estará manejando la mayor cantidad de corriente en la OPS. Cuando la caída de tensión en RE1 sea superior a la diferencia de los voltajes Vbe (es decir, 10 mV en este caso), Q5 se ve obligado a iniciar la conducción, porque la suma de las caída de tensión en Vbe de Q3 y la caída de tensión en RE1 superará el Vbe Q5. Como la corriente positiva de la OPS continúa en aumento, las características desiguales de Vbe en Q3 y Q5 serán negadas por las caídas de tensión desigual en RE1 y RE2, creando una condición cercana al equilibrio de corriente. [10] Las resistencias de degeneración son también muy valiosas en la prestación de algún tipo de compensación térmica en los transistores de salida. El principio de funcionamiento es el mismo al anterior. Si un transistor de salida comienza a mostrar una pérdida excesiva al calentarse, el exceso de corriente de fuga se manifestará como un aumento de la tensión en la resistencia de degeneración asociada y fuerza al otro dispositivo de salida asumir una mayor parte de la corriente de carga. Este tipo de resistencias de degeneración no contribuyen a mejora de la linealidad en OPS. Si bien es cierto que la retroalimentación degenerativa mejora la linealidad, como se explicó en el apéndice II, los bajos valores de las resistencias provocan una contribución insignificante a la linealidad; ya que es como si no estuvieran presentes. 76 3.3.2 Análisis de una etapa de salida simple En la figura 5-19 se presenta el circuito en análisis: Figura 5-19: Etapa de salida en análisis Primeramente se supondrá que V + = 55V y V − = 55V , la impedancia del altavoz será de 6Ω y la señal de salida del VAS será de una amplitud 50V. Para analizar el comportamiento del circuito con señal, será necesario dividir el mismo en dos etapas: 1) Se tomara primero a Q1 conduciendo y Q2 en corte, es decir, el comportamiento para el semiciclo positivo de la señal de entrada; 2) se tomara el semi-ciclo negativo de la señal de entrada donde, Q1 estará en corte y Q2 conduciendo activa. Partiendo primero de la situación indicada en el primer punto, se realiza el circuito equivalente para señales grandes, en el cual se desprecia los parámetros de entrada de la base del transistor, ya que éstos, para el caso de transistores de potencia, son muy pequeños. En la figura 5-20, se tiene el circuito equivalente que se utilizará para este análisis. 77 Figura 5-20: Circuito equivalente con el modelo de gran señal La resistencia de la fuente se desprecia en la figura 5-20, ya que tiene un valor pequeño. Ahora si se reflejan las resistencias a la base, cambiaría el circuito de la siguiente manera: Figura 5-21: Circuito con resistencias reflejadas en la base 78 Con la figura 5-21 se puede apreciar mejor el análisis del circuito, aplicando mallas: Vo = I B1 ( RL )( H FE + 1) (3.3.3 - 1) El la corriente de la base se puede expresar como : I B1 = Ei ( RE1 + R L )( H FE + 1) (3.3.3 - 2) Sustituyendo la ecuación (3.3.3 - 1) en (3.3.3 - 2) se obtiene : Vo RL = E i ( R E1 + R L ) (3.3.3 - 3) Obsevando la ecuación (3.3.3 - 3), se puede concluir que; con un valor de RE1 pequeño la ganancia de tensión es casi unitaria. Ahora suponiendo lo anterior, osea Vo = Ei , la corriente de salida tendrá la siguiente forma : Io = Vo E = i R L RL (3.3.3 - 4) Por lo que se concluye que la forma de onda de la corriente de salida y la amplitud dependerá de Ei y RL . 79 Apéndice IV En el presente apéndice se analizará el amplificador a trabajar, en la figura 5-22 se muestra dicho amplificador de potencia: Figura 5-22: Amplificador de potencia [9] El procedimiento a desarrollar en este apéndice será separar el amplificador en las tres etapas anteriormente detalladas, con el objetivo de analizarlas por separado. 80 4.1 Análisis en DC: 4.1.1 Fuente de corriente En la figura 5-23 se muestra el circuito con las fuentes de corrientes, con sus respectivos valores: Figura 5-23: Amplificador de potencia En la figura 5-23 se puede identificar que los transistores TR8 y TR9, al igual que las resistencias R20, R19, R9 y R5, son parte de la topología de fuente de corriente vista en el apéndice tres. Por lo que ya se tiene una idea de cómo funciona y como calcular su corriente de salida. En la figura 5-24 se puede observar el circuito aislado. 81 Figura 5-24: Fuente de corriente En el análisis del apéndice III, se despreció la caída de tensión de la resistencia R19, pero en este caso la resistencia tiene un valor mayor; por lo que si se tomará en cuenta en el análisis; se quiere obtener la corriente de salida de esta fuente ( I O 2 ), primero se tomará como VBE ≈ 0.5V , esto por que el transistor en uso es hecho de germanio; además cuenta con una corriente de Saturación de I S ≈ 13.5 ×10 −12 y un β min ≈ 100 . Recordando el modelo de Ebber-Moll: IC = I se VBE V BE VT → IB = I = VT ln C Is Is β e V BE VT (4.1.1-1) 82 Io2 = VBETR 8 + I BETR 8 R19 R 20 = VBETR 8 + Is β e V BE VT R19 R 20 0.57 ≈ = 10.17 mA 56 (4.1.1-2) Seguidamente se presentará en la figura 5-25 los resultados de la simulación del circuito, con una tensión de alimentación de 55V; tensión a la cual fue diseñada el amplificador. Figura 5-25: Simulación de la fuente de corriente En la figura 5-25 se puede comprobar los resultados de la corriente de salida. Dando como valor una corriente de I O 2 ≈ 10.94mA , valor muy cercano al obtenido en el análisis. Seguidamente se estará analizando la fuente de corriente restante de la figura 5-23, aplicando mallas: 56Ω ⋅ I CTR 9 + VBETR 9 = 100Ω ⋅ I CTR 4 + VBETr 4 + 100Ω ⋅ I BTR 4 (4.1.1 - 3) 83 Si se desarrolla el lado izquierdo de la ecuación (4.1.1-3), conociendo el valor de I CTR 4 ≈ 10.17mA y el valor de I STR 4 ≈ 54 ×10-9 se obtiene: 56Ω ⋅ 10.17mA + VT ln IC Is 10.17mA = 0.57 + 26mA ⋅ ln( ) ≈ 0.8853V -9 54 × 10 (4.1.1-4) Ahora desarrollando el lado derecho de la ecuación: 100Ω ⋅ I C 4 + VT ln IC 4 I + 100Ω ⋅ C 4 = 0.8853V Is β (4.1.1-5) Y conociendo que el transistor TR4 de la figura 5-23 es igual que el TR8; lo que significa que I S ≈ 13.5 ×10 −12 y β min ≈ 100 se obtiene una corriente de I C 4 ≈ 3.15mA . A continuación se muestra la simulación obtenida: Figura 5-26: Simulación de la fuente de corriente restante 84 En la figura 5-26 se puede corroborar el resultado anteriormente obtenido; el cual es de un valor muy cercano; ya que el valor que se obtuvo fue de I C 4 ≈ 3.15mA y la simulación arroja un I C 4 ≈ 3.55mA . 4.1.2 Amplificador Diferencial En la figura 5-27 se presenta la etapa de entrada aislada. Se cambió su circuito de polarización (fuente de corriente) por una fuente de corriente, con su respectivo valor de amperaje. Figura 5-27: Etapa de entrada. El circuito conformado por las resistencias R1, R2, R3 y R4 en conjunto con los condensadores C1 y C2 es un filtro paso banda pasivo. Su función es filtrar las frecuencias que no se desean amplificar; usualmente el intervalo va desde 20Hz -20KHz; que es el intervalo de frecuencias que son audibles por el oído humano. 85 Pero debido a recientes experimentos este intervalo ha sido extendido a 20Hz -200KHz ya que, se demuestra que aunque se amplifiquen frecuencias inaudibles, estas proporcionan un efecto de mejor claridad y ubicación de los sonidos. El circuito formado por las resistencias R17 y R18 con el capacitor C5 es la red de retroalimentación. Su función es retroalimentar el potencial de salida, a la entrada; tratando de tener en fase ambas señales. Ambos circuitos no interfieren en el desempeño de la etapa de entrada, por lo que no se tomaran en cuenta en el análisis en DC; por lo que el circuito en análisis quedará se presenta en la figura 5-28. Figura 5-28: Etapa de entrada, en análisis Las resistencias R11 y R12 están en paralelo, para que la corriente que fluye por ellas sea igual. Por lo que entonces la corriente que de R6 y R14 será la mitad de la corriente de cola. Ósea I R 6 ≈ I R14 ≈ 1.775mA . 86 Ahora si suponemos que la tensión base- emisor del transistor TR2 es I R7 = VBETR 2 R7 = VBETR 2 ≈ 0.7 : 0.7 ≈ 318 .2 µA 2.2 k (4.1.2-1) Realizando un análisis de nodos en el emisor de TR2 se puede observar: I R 7 + I CTR 2 = I R 6 (4.1.2-2) De la ecuación (4.1.2-2) se puede obtener la corriente de colector del transistor TR2 realizando una simple resta. La cual arroja un valor de I CTR 2 ≈ 1.46 mA . Consecuentemente se puede encontrar el valor de la corriente de base del mismo transistor, conociendo que el β min del transistor MPS06 es β min = 100 ; la cual da un valor de I BTR 2 ≈ 14.6 µA . Realizando otro análisis de nodo en el colector de TR1: I R 7 + I BTR 2 = I ETR 1 (4.1.2-3) Desarrollando el lado izquierdo de la ecuación de (4.1.2-8): I R 7 + I BTR 2 = 318 .2 µA + 14.6 µA = 332.8µA (4.1.2-4) Ahora se desarrolla el lado derecho: I ETR1 = I R 6 − I CTR 2 = 1.775mA − 1.46 mA = 315 µA (4.1.2-5) 87 Comparando los resultados de las ecuaciones (4.1.2-4) y (4.1.2-5) se puede comprobar la validez del cálculo, ya que los valores son muy cercanos; el parámetro de β min del TR2 pudo haber influido la no igualdad de los valores. Por último se calcula el valor de la corriente de polarización de entrada, la cual será la corriente de base de TR1; la cual será entonces I CTR 1 = I CTR 1 β = 3.15 µA . El circuito restante conformado por los transistores TR6 y TR3 y las resistencias R8 y R16 es un espejo de corriente. Lo que obligara a que I R 8 ≈ I R 6 ; debido a la propiedad del espejo de corriente, analizada en el apéndice III, si se conoce la corriente de colector se puede obtener el voltaje V Be , usando las ecuaciones de Ebbers-Moll. Conociendo que el transistor TR2 tiene los siguientes parámetros de VBE = VT ln β min ≈ 100 y I S ≈ 14.5 × 10 −15 : IC ≈ 0.662 Is (4.1.2-6) Realizando un análisis de mayas en el espejo de corriente: I R 8 ⋅ R8 + VBETR 3 = I R16 ⋅ R16 + VBETR 6 (4.1.2-7) De la ecuación (4.1.2-7) y conociendo las propiedades del espejo de corriente se puede concluir que: I R 8 ≈ I R16 (4.1.2-8) A continuación se presenta en la figura 5-29 la simulación como respaldo del análisis realizado anteriormente: 88 Figura 5-29: Simulación etapa de entrada, en análisis La corriente de salida de la etapa de entrada es muy pequeña, debido al efecto del espejo de corriente. Mientras que el voltaje de salida será: − VEE + I R 8 ⋅ R8 + VCETR 3 = Vo (4.1.2-9) 89 4.1.3 Etapa de amplificación de potencial: El circuito en análisis se presenta continuación en la figura 5-30, sustituyendo el circuito de fuente de corriente por una fuente de corriente constante. Figura 5-30: Etapa de amplificación de tensión Los capacitores C6 y C10 tienen como función establecer una buena estabilidad en altas frecuencias; por lo que no influyen en el análisis. Además, aunque el capacitor C10 actúe como circuito abierto, la corriente entregada por la fuente llegar al colector de TR11; esto porque entre el colector de TR11 y el nodo situado entre la fuente de corriente y el C10, se encuentra el circuito de polarización (diodos), que consumen la gran parte de la corriente generada por la fuente. En la figura 5-22 se puede apreciar la ubicación del circuito de polarización. Dicho esto se inicia el análisis, conociendo el valor de I CTR 11 ≈ 10.92 mA la corriente de saturación del transistor TR11, el cual es el BD139 se averigua el valor de y el valor de I STR 11 ≈ 24.7 mA ; VBETR 11 : 90 IC ≈ 0.338 Is VBE = VT ln (4.1.3-1) Seguidamente se realiza un análisis de mallas entre el emisor de TR10 y la base de TR11: I R 21 ⋅ R21 = VBETR11 I R 21 = VBETR11 R21 Utilizando un ≈ 153 .63µA (4.1.3-2) β min ≈ 100 , se puede encontrar la corriente de base de TR11, la cual será aproximadamente I BTR 11 ≈ 109.2 µA . Aplicando nodos se obtendrá la corriente de emisor de TR10: I BTR 11 + I R 21 = I ETR 10 I ETR 10 ≈ 262.83µA (4.1.3-3) Y por último se puede encontrar la corriente de base del TR10, el cual es el MPSA06, que su β min ≈ 100 . Por lo que I BTR 10 ≈ 2.6283 µA . A continuación se presenta la simulación que sustenta los cálculos anteriores: 91 Figura 5-31: Simulación de la etapa de amplificación de tensión En la figura 5-31 se pueden comprobar los cálculos obtenidos. Las corrientes de base y emisor del transistor TR10, son las que reflejan más margen de error, si se comparan con los valores obtenidos en el análisis Seguidamente se presentan los márgenes de error: I BTR 10 ≈ 2.176 − 2.6283 × 100 = 23.3% 2.176 I ETR 10 ≈ 214 .5 − 262 .83 × 100 = 22.5% 214 .5 Estos porcentajes de error se pueden atribuir al uso del parámetro β min , ya que este puede variar muy fácilmente. 92 El análisis de la etapa de salida en DC no se realiza; debido a que no es necesario. Se recuerda que para las anteriores etapas si se puede usar el modelo de pequeña señal, pero no se puede usar para la etapa de salida; esto debido a que maneja señales muy grandes, provocando que su punto de operación varíe constantemente. Por lo que un análisis en DC para obtener su punto de operación es infructífero. Lo que se realiza al final es un análisis de potencia para calcular la potencia manejada por los transistores. 4.2 Análisis en pequeña señal: Seguidamente se realiza el análisis de la etapa de entrada y la etapa de entrada en pequeña señal. Para esto se mandan todas las fuentes de tensión a tierra y se sustituye los transistores por el modelo de parámetros híbridos. Para iniciar se obtiene la impedancia de las fuentes de corriente constante, haciendo uso del “efecto Early”. Para efectos del análisis solo se presentan las ecuaciones de este, para mayor detalle referirse al punto 7 de la bibliografía. (4.2-1) (4.2-2) 1 = Z0 hoe (4.2-3) VA se conoce como la tensión Early y normalmente es de 100 a 120V para los transistores npn y 50V para los pnp. En este análisis se harán uso de las ecuaciones (4.2-2) y (4.2-3), ya que con estas se puede obtener las impedancias de las fuentes de corrientes constante mostradas en la figura 5-32. 93 Figura 5-32: Impedancias de las fuentes de corriente constante Primeramente se obtiene la impedancia Zo1, tomando para los transistor PNP un V A ≈ 52 y usando las corriente de colector obtenidas en la pasada sección. Z 01 = VA 52 = = 14.65k I C TR 4 3.55mA (4.2-4) Z T = 14.65k + 100 = 14.75 K Ahora se obtiene la impedancia Zo2, despreciando la impedancia de TR8 y R19, que no tienen mayor efecto sobre la impedancia obtenida de la fuente de corriente: Z 01 = VA 52 = = 4.762 k I C TR 4 10.92 mA (4.2-5) Z T = 4.762 k + 56 ≈ 4.820 K 94 4.2.1 Etapa de entrada Seguidamente se calculan los H ie del modelo de parámetros híbridos para el amplificador diferencial, conociendo que el β min para los transistores MPSA06 (NPN) y MPSA56 (PNP), es el mismo y tiene el valor de H ieTR 1 = H ieTR 2 = βVT I CTR1 β VT I CTR 2 β min = 100 : = 100 ⋅ 26mV = 8.254 k 315 µA = 100 ⋅ 26mV = 1.78k 1.46mA (4.2.1-1) Recordando además que las corrientes que fluyen por los transistores TR7 y TR5 son iguales a las corrientes que fluyen por TR1 y TR2, respectivamente; por ende: H ieTR 1 = H ieTR 7 = 8.254 k H ieTR 2 = H ieTR 5 = 1.78k (4.2.1-2) Realizando la sustitución de los transistores por el modelo de parámetros híbridos el circuito queda de la siguiente manera: 95 Figura 5-33: Pequeña señal para el amplificador diferencial. En la figura 5-33 se puede observar el circuito de pequeña señal para el amplificador diferencial. Se ha sustituido la fuente de corriente por su impedancia obtenida anteriormente, esta sirve para el análisis de corrientes y la obtención de la impedancia de entrada. Realizando un análisis de corrientes se puede concluir: I1 = I 2 (4.2.1-3) Por lo que el análisis de una de las dos corrientes bastaría para predecir la otra. Por lo que se está analizando La corriente I1 . I1 se puede expresar de la siguiente forma: I1 = 101I b1 + 100 I b 2 (4.2.1-4) 96 Por lo que se ocupa una relación entre las corrientes de base de los transistores TR1y TR2. Observando la figura 5-33 se puede ver claramente que R7 // H ieTR 2 ⇒ 2.2k // 178.1K . Por lo que la corriente de colector de TR1 se divide entre estas dos resistencias, de lo que se puede obtener la corriente que fluye por H ieTR 1 mediante un divisor de corriente: I H ieTR 2 = I BTR 2 = I CTR 1 ⋅ 2.2k 2.2k + 178.1k 100 I BTR 1 ⋅ 2.2k = ≈ 1.22 I BTR 1 2.2k + 178.1k (4.2.1-5) Si se combinan las ecuaciones (4.2.1-4) y (4.2.1-5) se obtiene: I1 = 223 I b1 (4.2.1-6) Ahora se tiene una relación entre R6 = 100Ω I1 y I b1 , por lo que se puede reflejar la resistencia a la base de TR1 para obtener la impedancia de entrada del circuito. Z i = 8.254 KΩ + 233 ⋅ 100Ω = 31.554 kΩ (4.2.1-7) Seguidamente se obtiene la expresión de tensión de entrada con respecto a la tensión de modo común y modo diferencial. En la figura 5-33 se puede observar que la impedancia de la fuente de corriente se suma con, la resistencia producto del paralelo entre las resistencias de 12K. Dando como resultado una Z t = 20.75kΩ . 97 Si se realiza una malla desde la tensión V+ a tierra se obtendrá: V + = 8.254 k ⋅ I BTR 1 + 100 I1 + 20.75k ⋅ ( I1 + I 2 ) I1 + 100 I1 + 20.75k ⋅ ( I1 + I 2 ) 223 = 138 I1 + 20.75k ⋅ ( I1 + I 2 ) = 8.254 k ⋅ (4.2.1-8) Recordando que en el modo común se cumple las siguientes expresiones: V + = V − = VA I1 = I 2 (4.2.1-9) (4.2.1-10) Si se combinan las anteriores 2 ecuaciones y la ecuación (4.2.1-8) se obtiene: VA = 138 I1 + 2 ⋅ 20.75kI1 I1 A = VA 41.638k (4.2.1-11) Ahora en el modo diferencia se cumple las siguientes expresiones: V+ =V− = VD 2 I1 = − I 2 (4.2.1-12) (4.2.1-13) 98 Si se sustituyen las ecuaciones (4.2.1-12) y (4.2.1-13) en la ecuación (4.2.1-8) se obtiene: VD = 138 I1 2 V I1 D = D 276 (4.2.1-14) Seguidamente se expresa la corriente I1 en términos de sus compontees en modo común y modo diferencial: I1 = I1 D + I1 A = VA V + D 41.638k 276 Al igual que la corriente (4.2.1-15) I1 y teniendo en cuenta que I 1D = − I 2 D : I2 = I2D + I2 A = VA V − D 41.638k 276 (4.2.1-16) Seguidamente se analiza el espejo de corriente con el modelo de parámetros híbridos. Primeramente se obtienen los H ie de los transistores TR3 y TR6: H ieTR 3 = H ieTR 6 = βVT I CTR 3 = 100 ⋅ 26mV = 1.478k 1.759mA (4.2.1-17) 99 A continuación se sustituye los transistores por el modelo de parámetros híbridos: Figura 5-34: Pequeña señal espejo de corriente. Realizando un análisis de nodos en la figura 5-34 se puede determinar que: I 2 = 100 I B 6 + ( I B 6 + I B 5 ) = 101I B 6 + I B 5 (4.2.1-18) Seguidamente, realizando un malla en los emisores, se determina: 100 VR 8 = VR16 101I B 6 ⋅ 68 = 101I B 5 ⋅ 68 (4.2.1-19) I B6 = I B5 Sustituyendo la ecuación (4.2.1-18) en la ecuación (4.2.1-19): I 2 = 102 I B 5 (4.2.1-20) Por lo que se puede concluir: 100 I 2 = 100 I B 5 102 (4.2.1-21) Y finalmente realizando un análisis de nodos, para la corriente I1 : I1 = I x + 100 I b 5 I x = I1 − 100 I b 5 (4.2.1-22) 100 I x = I1 − I2 102 Recordando que la corriente Ix Si se expresa la corriente Ix es la que entra a la siguiente etapa. en términos de sus componentes de modo común y diferencial, quedara de la siguiente manera: ( ) ( I x = I1D + I1 A − I 2 D + I 2 A ) V 50 V A V VA = + D − − D 41.638k 276 51 41.638k 276 101VD VA = + 14076 2123538 (4.2.1-23) 101 4.2.2 Etapa de amplificación de tensión: Prosiguiendo se realiza un análisis de pequeña señal del VAS, primero se calcula los H ie de los transistores TR10 y TR11; el TR11 no es del mismo tipo que todos los demás transistores, este es el BD139 y posee un H ieTR 10 = H ieTR 11 = β VT I CTR10 βVT I CTR 11 β = 170 : = 100 ⋅ 26mV = 12.12k 214.5µA = 170 ⋅ 26mV = 404.75Ω 10.92mA (4.2.2-1) Y seguidamente se presenta el circuito en pequeña señal: Figura 5-35: Pequeña señal del VAS. 102 En la figura 5-35 se incluye la impedancia de la fuente de corriente, obtenida en pasadas secciones. Los capacitores sólo ayudan a la estabilidad del circuito, añadiendo un polo de compensación, esto se puede apreciar en secciones anteriores de manera más detallada; por ende no se toman en cuenta para el análisis de pequeña señal. Realizando un análisis de nodos en la figura 5-35: 101I B 7 = I B 8 + I R 21 (4.2.2-2) Seguidamente se aplica un divisor de corriente para determinar la relación entre las Corrientes I B 7 y I B 8 : I B 8 = 101I B 7 ⋅ I B 8 = 85.3I B 7 2 .2 k 2.2k + 404.752Ω Utilizando la ecuación (4.2.2-3) para determinar la corriente (4.2.2-3) I CTR 11 : I CTR11 =170 I B8 (4.2.2-4) I CTR11 =14.501kI B 7 Y conociendo el valor de I B 7 de la ecuación (4.2.1-23) se sustituye en la (4.2.2-4): I B7 = I x I CTR11 = 8530.54 I x (4.2.2-5) 853 = 104VD + VA 124914 103 Y por último obtengo el potencial en el colector: I CTR11 ⋅ 4.818k = VCTR11 VCTR11 = 501kVD + 32VA (4.2.2-6) Recordando la función de la etapa de salida, la cual es amplificar corriente dependiendo del potencial de entrada; pero la tensión es la misma de la entrada. Por esto se puede concluir que el potencial de salida del amplificador es: Vo = 501kVD + 32VA (4.2.2-7) Si se compara la ecuación anterior con la ecuación característica de un amplificador, presentada a continuación: Vo = ADVD + AAVA (4.2.2-8) Se puede obtener el rechaza de modo común, siendo este expresado de la siguiente manera: A CMRR = 20 ⋅ log D AA 501k 20 ⋅ log = 84dB 32 (4.2.2-9) 104 4.3 Etapa de salida: Como se mencionó anteriormente en la etapa de salida solo se le realiza un análisis de potencia, ya que su funcionamiento no se podría describir usando el modelo de pequeña señal, debido a el tamaño de las señales que maneja. Seguidamente se presenta la etapa de salida: Figura 5-36: Etapa de salida En la figura 5-36 se puede observar que la etapa de salida en estudio es de tipo emisor seguidor, usando los transistores de salida en paralelo. La etapa en estudio puede ser reducirse a una etapa AB estándar, mostrada en la figura 5-37, para el cálculo de la potencia en cada transistor 105 Figura 5-37: Etapa de salida simplificada Las siguientes expresiones son las ecuaciones estándar de la clase B, para mayor detalle refiérase al punto 7 de la bibliografía. 2V 2 CC PCC ,Max = ` R Lπ V 2 CC PL,Max = 2 R `L P − PL,Max PT ,Max = CC ,Max 2 (4.3-1) 106 Si PCC , Max es la potencia máxima que puede entregar la fuente, PL, Max potencia máxima en la carga y PT ,Max es la potencia máxima en cada uno de los transistores. Todas estas expresiones son ideales ya que para su obtención no se tomaron en cuenta la caída de voltaje en las resistencias. Se obtendrá los valores teóricos suponiendo una R ` L = 6Ω . PCC ,Max = 321W PL,Max = 252W PT ,Max = 34.5W (4.3-2) La potencia en cada transistor será de menor valor; ya que en la etapa de salida original los transistores están en paralelo, logrando que la corriente se divida de manera equitativa; por lo que la potencia deberá reducirse a la mitad. PT ,Max = 17.25W (4.3-3) Con respecto al valor de la corriente de salida se puede usar el análisis realizado en el apéndice III, el cual tiene la siguiente forma: Io = Vo E = i RL RL (4.3-3) 107 Si se conoce que la amplificación de tensión no es alimentación del circuito y además suponiendo un no mayor a las tensiones de RL = 6Ω se puede encontrar un tope máximo teórico de la corriente de salida: Io = Ei 55V = = 9.1667 A R L 6Ω 4.4 Diseño de la fuente de alimentación A continuación se presenta en la figura 5-38 el esquemático propuesto para la fuente de alimentación: R1 D9 D2SB60/SDG TX1 1m V V1 VOFF = 0 VAMPL = 170 FREQ = 60 C1 4.7u 0 0 C3 4.7u V+ C5 4.7u 0 C2 4.7u C4 4.7u V- C6 4.7u V+ Figura 5-38: Topología a usar para el diseño de la fuente de alimentación. La fuente de alimentación es no regulada, se conforma de un puente de diodos y solo capacitores en paralelo; esto para cuando el amplificador solicite mayor energía la fuente este en la capacidad de brindarla. Los valores de capacitores se escogen un poco altos para que se minimice los cambios de la tensión. Se diseño para obtener una tensión de +55V y -55V aproximadamente, se presenta a continuación la simulación del circuito. 108 Figura 5-39: Salida del circuito En la figura 5-39 se observa la salida del circuito, que da un potencial Dc muy cercano al diseñado. 109