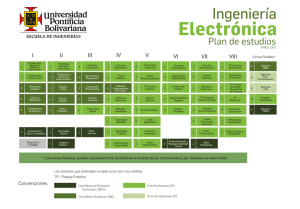

Tema 1.4. Diseño de elementos CMOS específicos.

Anuncio

Módulo I Tecnología CMOS

Tema 4 Diseño de elementos CMOS

específicos

Módulo I Tecnología CMOS

Tema 1. Tecnologías de diseño microelectrónico.

microelectrónico.

Tema 2. Diseño digital CMOS.

Tema 3. Diseño físico de circuitos CMOS.

Tema 4. Diseño de elementos CMOS

específicos.

Tema 5. Cables.

Tema 4 Diseño de elementos CMOS

específicos

1.1.- Circuitos analógicos básicos: capacidad, capacidad de paso,

resistencia, buffer.

2.2.- Circuitos específicos:

– líneas de retardo,

– osciladores controlados por voltaje,

– comparadores de fase,

– PLL,

– DLL.

– Estructuras de E/S:

puertos de alimentación y tierra,

puertos de entrada,

puertos de salida,

puertos bidireccionales

puertos triestado,

puertos especiales.

Introducción

Ley de Ohm V = I x R

Sólo para cargas resistivas.

resistivas.

En general: V = I x Z

Z: impedancia de la carga

Capacitor:

Capacitor: es un dispositivo que almacena energía en presencia

de un campo eléctrico y trata de mantener constante el voltaje

entre sus terminales.

La impedancia de un capacitor es Z c = 1/ j.ω

j.ω.C ( ω = 2 π f)

– Para altas frecuencias (ω

(ω = grande)

grande) la señal pasa fácilmente (baja

impedancia)

– Para bajas frecuencias (ω

(ω = pequeño)

pequeño) la señal pasa con dificultad (alta

impedancia)

– Para D.C. ( ω = 0) la señal se bloquea (impedancia infinita para continua)

Vin

C=

Q

∆V

R

Vout

C

Filtro paso baja

Vin

C

Vout

R

Filtro paso alta

Introducción

Inductore

Inductores

Es un dispositivo que trata de mantener constante un flujo de

corriente a través de sí mismo, y es capaz de almacenar energía

en presencia de un campo magnético

Muchas componentes eléctricas son inductivas:

– motore

motores

– transformadores

transformadores

– puertos de E/S

La impedancia de un inductor viene dada por:

por:

Z L = j .ω

.ω .L

– Para D.

D. C. es 0

– Se incrementa con la frecuencia

Todos los elementos de un circuito (cables) tienen una inductancia

inductancia

inherente

Introducción

Resumen:

Dominio del tiempo

dvC (t ) 1

= ic (t )

dt

C

diL(t )

vL(t ) = L

dt

vR (t ) = iR (t ) * R

Dominio de la frecuencia

1

v ( 0)

Ic( s) +

Cs

s

VL ( s ) = L( sIL ( s ) − i (0))

VR ( s ) = IR ( s ) * R

Vc( s ) =

S=jw

Impedancia

1

jwC

ZL = jwL

ZC =

ZR = R

Tema 4 Diseño de elementos CMOS

específicos

1.1.- Circuitos analógicos básicos: capacidad, capacidad de paso,

2.2.- Circuitos específicos:

– líneas de retardo,

– osciladores controlados por voltaje,

– comparadores de fase,

– PLL,

– DLL.

– Estructuras de E/S:

resistencia, buffer.

puertos de alimentación y tierra,

puertos de entrada,

puertos de salida,

puertos bidireccionales

puertos triestado,

puertos especiales.

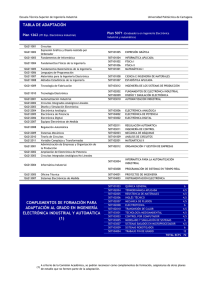

4.1 Circuitos analógicos básicos

Capacidades

Necesarias en circuitos analógicos (capacitores

(capacitores de conmutación) y celdas de

memoria

Pueden usarse capacitores de polisilicio (2 layers de polisilicio y oxido en

medio)

En ocasiones se utilizan estructuras 3D para incrementar la capacidad

capacidad por área

Layer de interconexión

fF/

fF/µm2

Polisilicio a substrato

0.058±

0.058±0.004

Metal 1 a substrato

0.031±

0.031±0.001

Metal 2 a substrato

0.015±

0.015±0.001

Metal 3 a substrato

0.010±

0.010±0.001

Difusión n+ a substrato

0.36±

0.36±0.02

Difusión p+ a substrato

0.46±

0.46±0.06

φ

D

φ

Q

4.1 Circuitos analógicos básicos

También puede utilizarse la

capacidad de puerta de los

transistores.

Se descompone en tres

porciones:

– CGB (entre puerta y

substrato),

– CGS (puerta y fuente),

– CGD (puerta y drenador).

drenador).

No son lineales y son función de

la región de trabajo y de la

superficie del canal.

Descripción

C

MOS OnOn-chip (0.35*114µ

(0.35*114µm)

250fF

MOS OnOn-chip (1.4*114µ

(1.4*114µm)

1pF

SMT Cerámica

1nF

SMT Cerámica

10nF

Disco de cerámica

10nF

Electrolítico de aluminio

10 µ F

Electrolítico de aluminio

1000 µF

4.1 Circuitos analógicos básicos

Capacidades de paso

Los capacitores de paso son elementos clave de un sistema de distribución de

alimentación a todos los niveles (sistema, panel, tarjeta, paquete,

paquete, chip)

En cada nivel los condensadores deben dimensionarse para aportar los picos

de corriente que pueden producirse en un ciclo

– En cada ciclo se consume una cierta cantidad de intensidad debida

debida a las

conmutaciones de los FF

Qck = IAVG * tck

– En ciertos momentos puede haber una demanda mayor de intensidad que

puede provocar una caída del potencial del circuito

Q max = Qck * ki

CB ≥

Qck *ki

∆V

0.25⟨ ki ⟨ 0.5

Si existen elementos inductivos L la

dimensión del capacitor debe calcularse

para evitar oscilaciones y la ecuación que

nos queda es:

CB

I

> L

∆V

AVG

max

2

+ Ki

IAVGtCK

∆V max

4.1 Circuitos analógicos básicos

Circuito equivalente de un condensador de paso

– LC inductancia parásita

– Rs resistencia serie efectiva

ZC = jwLC + Rs +

1

1

= Rs + j ( wLC −

)

jwC

wC

Los componentes capacitivo e inductivo de la

impedancia se cancelan en:

fLC =

1

2π LC

Si la Rs es bastante grande para moderar el

circuito LC hay dos puntos de ruptura

fRC =

1

2πRSC

fLR =

Rs

2πL

4.1 Circuitos analógicos básicos

Por encima de fRC y fLC la impedancia del capacitor se encuentra dominada por

la inductancia o por la resistencia, y el capacitor pierde su efectividad

a.a.- Capacitor electrolítico C=10µ

C=10µF

LC=10nH

Rs=1Ω

Rs=1Ω

fRc=160kΩ

fLR=16MΩ

No se usa por encima de 100KHz

b.b.- Disco de cerámica C=10nF

LC=5nH

Rs=0.1Ω

Rs=0.1Ω

fLc=23MΩ

Para esta frecuencia actúa como R=0.1 Ω

Puede utilizarse hasta 10MHz

4.1 Circuitos analógicos básicos

El tipo de capacitor en cada nivel debe seleccionarse para que tenga un ancho de

banda adecuada a las variaciones de corriente esperadas

Una red de distribución de alimentación utiliza una jerarquía de capacitores

En cada nivel de jerarquía los condensadores filtran una banda de

de frecuencia de

corrientes transitorias

Dentro de un CI tr es del orden de 200ps (fs=800MHz

(fs=800MHz))

4.1 Circuitos analógicos básicos

Resistencias

– Polisilicio

es altamente resistivo

Produce resistencias lineales

Difícil de controlar (la resistencia

absoluta puede variar en un factor 2:1)

– Difusión o nn-well

Son lineales

Presentan gran capacidad de unión

– Transistores FET

No son lineales

Permiten gran compactación y fácil

conexión entre componentes

Facilitan la digitalización

Metal1

/metal2

Max

Min Typ

Ω/sq Ω/sq Ω/sq

0.05 0.07 0.1

metal3

0.03

0.04

0.05

poli

15

20

30

silicio

2

3

6

Difusión

(n+, p+)

10

25

100

nwell

1K

2K

5K

4.1 Circuitos analógicos básicos

VDD

Trabaja en la zona lineal VGS - VT<VDS

IDS = -βp [ {VGS - VTp} VDS - (VDS)2 / 2 ]

βp=KpW/L

Kp=µCox

La relación IDS / VDS es casi lineal para pequeños VDS

ROP=1/ βp {VGS - VTp}

ROp =

L

1

W µCox( VGS − VTP )

La resistencia obtenida puede llegar fácilmente a 100KΩ. La

misma resistencia en polisilicio requeriría mucha más área

•La componente cuadrática se hace importante para VDS>1

4.1 Circuitos analógicos básicos

4.1 Circuitos analógicos básicos

Utilizando otro FET conectado como diodo se extiende la zona lineal

VDD

ITRIODO ≅ Ilineal= -βp [ {VGS - VTp} VDS - (VDS)2 / 2 ]

IDIODO ≅ Isat= -βp [ (VGS – VTp)2 / 2 ]

ITRIODO ≅ -βp [ {-Vdd - VTp} VDS - (VDS)2 / 2 ]

IDIODO ≅ -βp [ (VDS – VTp)2 / 2 ]= -βp [ (VDS )2 / 2+( VTp)2 / 2- VDS VTp]

I= ITRIODO+ IDIODO ≅ -βp [ {-Vdd - VTp} VDS + (VTn)2 / 2 - VDS VTp]

Con la aproximaciones se obtiene una ecuación lineal

4.1 Circuitos analógicos básicos

La curva punteada muestra el comportamiento de un resistor lineal perfecto

4.1 Circuitos analógicos básicos

Cuando el voltaje de los dos terminales puede variar sobre un amplio

amplio

rango, se suele emplear un resistor como puerta de paso

vin

Cuando el voltaje de los terminales vin y vout sube, se reduce

la conductancia del NFET, mientras que la del PFET se

incrementa.

Suponiendo que ambos están en zona lineal puede

aproximarse por

RONP ≅ 1/(βp ( |VGSp | - | VTp |) )

RONN ≅ 1/(βn ( VGSn - VTn))

Dimensionando los dispositivos de forma correcta, el efecto

global se cancela, y la resistencia total es casi lineal

vout

4.1 Circuitos analógicos básicos

Cuando se necesita una resistencia muy precisa, cualquiera de los

los

circuitos anteriores puede digitalizarse

¾Los valores digitales de las líneas r0 a r3 seleccionan el subconjunto de

transistores m0-m3 que conducen.

¾Según las dimensiones de los transistores puede conseguirse un rango

más o menos amplio o preciso de resistencias.

r3

m3

r2

m2

r1

m1

r0

m0

m4

4.1 Circuitos analógicos básicos

Buffers

Para procesos no submicrónico

Se utilizan para atacar grandes grandes

1

1 CLVDD CLVDD

capacidades

tp = (tpHL + tpLH ) = (

+

)

2

2 Idssn

Idssp

Puede utilizarse un simple inversor (bufferinversor) con una resistencia de canal muy

CLVDD

Ln

Lp

+

tp =

pequeña (W grande)

2

W

p

k

p

W

nkn

2 (VDD −VT )

Al aumentar W se disminuye la resistencia de

k = µCox

canal, pero se aumenta la capacidad de puerta y el

retardo de la etapa anterior

Sin buffer

CL

2/α

2/ α u

tp = tpinv =

tp 0

C min

Con

buffer

Cin 2/2

CL

2/2u

tp 0 =

C min VDD

1

2

kn

(VDD −VT )

tp = tpinv + tpbuf = utp 0 +

Para procesos submicrónicos el razonamiento es

idéntico con una Idss diferente

CL / C min

CL / C min

)

tp 0 = tp 0(u +

u

u

uopt =

CL

C min

4.1 Circuitos analógicos básicos

Sin buffer

tp = tpinv =

Con buffer

CL

tp 0

C min

uopt =

tp = tpinv + tpbuf = utp 0 +

CL

C min

CL / C min

CL / C min

tp 0 = tp 0(u +

)

u

u

tp = tp 0( CL / C min +

CL / C min

) = 2tp0 CL / C min

CL / C min

Merece la pena insertar un buffer cuando

CL / C min > 2 CL / C min

CL / C min > 4

Interesa poner un buffer siempre que la

carga capacitiva sea superior a 4Cmin, es

decir, cuando el número de puertas

conectadas sea mayor que 4.

4.1 Circuitos analógicos básicos

Los bufferes son elementos con grandes capacidades de

entrada

VDD

C min = 3Cg

Supongamos CL=200Cg

uopt =

2/4u

CL

200Cg

=

≈8

C min

3Cg

Vout

Vin

Cin=(3u)Cg

2/2u

CL

Para grandes cargas se necesitan

bufferes de gran tamaño con Cin

demasiado grandes

4.1 Circuitos analógicos básicos

Supper-buffers

Se utilizan para atacar capacidades muy grandes, como por ejemplo

capacidades externas que pueden ser 1000 veces mayor que una capacidad

de puerta mínima

CL

Sin buffer

tp =

tp 0 = 1000tp 0

C min

Con un buffer

tp = 2tp 0 CL / C min = 2tp0 1000 ≈ 64tp 0

Con N bufferes

Cin

2/4

2/4f

2/4f2

2/4f3

2/4f4

2/2

2/2f

2/2f2

2/2f3

2/2f4

CL

4.1 Circuitos analógicos básicos

Supongamos la etapa i

Cin

2/4

2/4fi-1

2/4fi

2/4fi+1

2/4fN-1

2/2

2/2fi-1

2/2fi

2/2fi+1

2/2fN-1

Suponiendo que la capacidad de cada inversor se escala linealmente con su

tamaño

CLi = f i+1C min

W

i

= f

L i

tpbufi =

CLi / C min

f i+1

tp 0 = tp 0( i ) = tp 0 f

u

f

Todas las etapas (excepto la última) tienen el mismo retardo f*tp0

Para conseguir el mismo retardo en la última etapa debe cumplirse que

CL = f N C min

4.1 Circuitos analógicos básicos

CL = f N C min

El retardo total viene dado por

tp = N * f * tp0

donde

fopt = e

topt = eLn(CL/Cin)tp0

En realidad f puede ser 2 o 3 y

N puede tomarse por arriba o

por debajo de

Ln(CL/Cmin)/Lnf

N=

Ln(CL

C min)

Lnf

Los resultados son pesimistas

puesto que la capacidad no

aumenta linealmente al hacer

más ancho el canal, debido a

las capacidades de difusión de

los transistores

CL

4.1 Circuitos analógicos básicos

Variación de tp/tp0

tp/tp0 en función de f para distintos valores de x=CL/Cmin

f/Lnf

u/ln(u)

60.0

40.0

x=10,000

x=1000

20.0

x=100

x=10

0.0

1.0

3.0

fu

5.0

7.0

4.1 Circuitos analógicos básicos

4.1 Circuitos analógicos básicos

VDD

Buffers triestado

Sirven para conectar las salidas de varias

puertas a un bus

En cada instante, todos los buffers

menos uno deben tener su salida en alta

V DD

impedancia

En

Out

In

En

En

Out

Esta otra implementación tiene menos

transistores en serie, y por tanto es más

apropiada para atacar grandes capacidades

En

In

Tema 4 Diseño de elementos CMOS

específicos

1.1.- Circuitos analógicos básicos: capacidad, resistencia, capacidad de

paso, buffer.

2.2.- Circuitos específicos:

–

–

–

–

–

–

líneas de retardo,

retardo,

osciladores controlados por voltaje,

comparadores de fase,

PLL,

DLL.

Estructuras de E/S:

puertos de alimentación y tierra,

puertos de entrada,

puertos de salida,

puertos bidireccionales

puertos triestado,

puertos especiales.

4.2 Circuitos específicos

Líneas de retardo

Se trata de elementos que permiten ajustar los flancos de reloj

Modelo digital basado en inversores

Problemas del modelo:

1.- Rango amplio y ajuste fino son objetivos mutuamente incompatibles.

2.- El retardo mínimo depende de la tecnología

3.- Necesidad de un sistema de control digital

Los sistemas de control analógicos suelen

ser mas compactos, eficientes y precisos

4.2 Circuitos específicos

Solución: utilizar un elemento de retardo con una entrada de control

control

analógica.

El elemento de una línea de retardo es una fuente de corriente FET

FET que

carga una capacidad de puerta FET

Controlamos la intensidad de la corriente de carga

O bien controlamos la capacidad de carga

4.2 Circuitos específicos

Rango de ajuste de retardo para los dos casos anteriores

(W/L)p=2 (W/L) n=5.6µm/0.35 µm

K=10

El retardo que se muestra es el de un par de etapas

Las líneas punteadas representan la simulación para las

condiciones peor y mejor

4.2 Circuitos específicos

Sensibilidad (Sv): es el cambio en el retardo ocasionado por un cambio en

el voltaje de alimentación

Problema: gran sensibilidad al ruido en la fuente

Elemento de carga controlada

Elemento de corriente controlada

Retardo de un par de etapas

tinv ≈

VDD

VDD

1

≈

≈

Idss (VDD −VT )2 VDD

tinv ≈

VDD

VDD

≈

≈ VDD

IDS

f (VCN )

4.2 Circuitos específicos

Solución: utilizar la línea de retardo basada en inversores

con una fuente de voltaje regulada

Filtro paso baja

(elimina ruido de alta

frecuencia)

v2

v1

+

-

v0

vo ≈ Ad (v 2 − v1)

4.2 Circuitos específicos

Otra solución: utilizar como elemento de retardo básico un diferencial.

diferencial.

Las estructuras diferenciales amplifican la diferencia entre 2 voltajes

voltajes y

tienen inherentemente mejor eliminación de ruido

Cada par de señales varían

entre VDD y VLO=IT*R

IT está determinada por Vbn

El retardo es ~ a R

Variaciones en el voltaje de

alimentación cambian sólo

el voltaje del modo común

Método de control

analógico: utilizar una

resistencia ajustable

implementada con PFET

4.2 Circuitos específicos

En la figura se muestra un resistor controlado por voltaje y

las corrientes asociadas

Si Vload se limita entre Vc y 0, la característica es aprox. Lineal y la

resistencia viene determinada por Vc.

Tema 4 Diseño de elementos CMOS

específicos

1.1.- Circuitos analógicos básicos: capacidad, capacidad de paso, resistencia,

resistencia,

buffer.

2.2.- Circuitos específicos:

– líneas de retardo,

– osciladores controlados por voltaje,

– comparadores de fase,

– PLL,

– DLL.

– Estructuras de E/S:

puertos de alimentación y tierra,

puertos de entrada,

puertos de salida,

puertos bidireccionales

puertos triestado,

puertos especiales.

4.2 Circuitos específicos

Oscilador controlado por voltaje:

voltaje: se clasifican según la

ecuación diferencial que describe su comportamiento

– Osciladores de primer orden:

orden: generan una señal cuyo periodo se

determina por el tiempo de carga de una capacidad

La frecuencia del oscilador puede

cambiarse variando las fuentes de

corriente.

Si ambas fuentes son iguales:

T=

2C (VHI − VLO )

I

Puede realizarse un diseño más simple con un único comparador y un

voltaje umbral

4.2 Circuitos específicos

En los diseños modernos suelen utilizarse osciladores en anillo

formados por elementos de retardo controlados por voltaje

Es análogo al oscilador de 1er orden:

•

El capacitor y la corriente de carga se implementa

directamente en los elementos de retardo

•

La función de memoria está implícita en el

retardo a través de la cadena de etapas

•

El cambio está implícito en la inversión alrededor

del lazo

F=

1

N (TDH + TDL )

4.2 Circuitos específicos

– Osciladores de segundo orden: son circuitos LRC

Son útiles en aplicaciones que requieren una señal periódica con muy

poco ruido de fase.

Problema: no se puede variar la frecuencia sobre un rango amplio

Cuarzo o cerámica

Osciladores de cristal:

utilizan un cristal piezoeléctrico

como elemento mecánico análogo a

un circuito resonante LRC

El cristal piezoeléctrico es

equivalente a un circuito serie LRC

La frecuencia de vibración depende

de las dimensiones del cristal

Zc = − ZR

ZR = R +

Wr =

1

+ jwL

jWC

1

LC

Tema 4 Diseño de elementos CMOS

específicos

1.1.- Circuitos analógicos básicos: capacidad, capacidad de paso, resistencia,

resistencia,

buffer.

2.2.- Circuitos específicos:

– líneas de retardo,

– osciladores controlados por voltaje,

– comparadores de fase,

–

–

–

PLL,

DLL.

Estructuras de E/S:

puertos de alimentación y tierra,

puertos de entrada,

puertos de salida,

puertos bidireccionales

puertos triestado,

puertos especiales.

4.2 Circuitos específicos

Comparadores de fase: miden el retardo relativo o

fase entre 2 señ

señales

Son necesarios para generar la señ

señal de control Vc que

selecciona un determinado retardo en la lí

línea de retardo

Modelo ideal

φAB=2π(tA-tB)/tciclo

4.2 Circuitos específicos

En la práctica no es posible construir un comparador ideal. Los

comparadores reales introducen offset y retardo

Necesitan transiciones en sus entradas. Operan sobre un rango de fase

Tienen ganancia no lineal

Rango lineal: relación lineal fase-voltaje

Rango de bloqueo: rango sobre el cual la salida tiene la polaridad adecuada

4.2 Circuitos específicos

Comparador de fase XOR

Φ≅0

Φ ≅ π/2

Φ≅π

La salida V es una versión filtrada de Q (se eliminan las altas frecuencias)

Amplio rango lineal centrado en π/2

Sólo funciona con

señales periódicas

4.2 Circuitos específicos

•

Un lazo de control que utiliza un detector de fase XOR referencia la salida a Vdd/2 y

bloquea la diferencia de fase a π/2 (se dice que las señales están en cuadratura).

Sólo son adecuados en lazos temporales que requieren estabilizar la diferencia de fase

en π/2

Si el factor “duty” es distinto del 50% se puede pasar la señal de entrada a través de un

biestable T (divisor de frecuencia). El problema es que se aumenta el tiempo de

respuesta del lazo de control

Si se utiliza en un PLL y las señales de entradas tienen frecuencias muy diferentes, la

salida de la XOR promedia muy cerca de su punto medio. Por esta razón la

convergencia del lazo es muy lenta, y se suele utiliza un detector de frecuencia auxiliar

4.2 Circuitos específicos

Comparador de fase FF

Tiene dos estados y un rango de ±π

alrededor del punto de bloqueo

Alta ganancia

Tp: periodo reloj

Ta: tiempo apertura

Si B se adelanta respecto de A la salida es 1

Si B se retrasa respecto de A la salida es 0

El FF muestrea el

estado de la señal B en

los flancos de subida de

la señal A

No es un detector proporcional ni simétrico, por eso

suelen utilizarse dos detectores de fase con las

funciones de señal muestreada y de muestreo

intercambiadas, y se restan sus salidas.

Puede haber falso bloqueo cuando las entradas están

relacionadas armónicamente.

La adición de un 3er estado aumenta el rango de detección y elimina el faso bloqueo

4.2 Circuitos específicos

Comparador de fase secuencial

Si A encabeza a B,

Up está a 1 un tiempo

proporcional a la

diferencia de fase

entre A y B

La salida Dn produce

un pulso breve cuya

duración es la suma

del retardo a través de

la puerta AND y el

retardo del reset de los

FF

Si B adelanta a A las

reglas de Up y Dn se

invierten

4.2 Circuitos específicos

La adición del tercer estado permite un rango de detección más amplio

amplio

Un ángulo mayor que

2π se sigue

interpretando como +

De esta forma puede utilizarse como detector de frecuencia

Es muy útil incluso cuando las

frecuencias de ambas señales es

muy diferente

En ocasiones se denomina

detector de fase y frecuencia

(PFD)

4.2 Circuitos específicos

Comparadores de frecuencia y fase secuenciales

Máquina de estados asíncrona

Contador mod 3 de

transiciones

Entradas a,b

Salidas A,B

Estados de cuenta (b, n, a)

Estado a A=1 hay más transiciones en a

Estado b B=1 hay más transiciones en b

A-B sirve como salida de control

con rango lineal 4π

centrado en 0

El signo de AA-B indica cuál tiene mayor frecuencia

El tiempo que A ó B están a 1 indica qué señal se adelanta

Tema 4 Diseño de elementos CMOS

específicos

1.1.- Circuitos analógicos básicos: capacidad, capacidad de paso, resistencia,

resistencia,

buffer.

2.2.- Circuitos específicos:

– líneas de retardo,

– osciladores controlados por voltaje,

– comparadores de fase,

– PLL,

– DLL.

DLL.

– Estructuras de E/S:

puertos de alimentación y tierra,

puertos de entrada,

puertos de salida,

puertos bidireccionales

puertos triestado,

puertos especiales.

4.2 Circuitos específicos

PLL (Phase- Loocked Loop) - DLL (Delay Locked Loop)

Oscilador controlado por voltaje

En los casos donde el reloj de referencia D sea muy inestable o no pueda

utilizarse, hay que usar un PLL que genere el reloj local

El VCO toma una entrada de control Vf y genera una señal periódica de frecuencia

f=fc+kfVf

Se suele diseñar con una kf lo más pequeña posible que permita generar el rango

de frecuencias deseado

4.2 Circuitos específicos

Alineadores de reloj

4.2 Circuitos específicos

PLL

Si el detector de fase proporciona VDD/2 en el punto de bloqueo este PLL

produce un desfase en la salida. Para solucionar esto se puede utilizar un filtro

RC activo

El filtro RC activo se suele

utilizar en implementación de

PLL de componentes discretas

4.2 Circuitos específicos

Filtros de carga

Lazo de 100 MHz inicializado a 170MHz

Comparador de frecuencias

Un contador de transiciones da

el signo de la diferencia de

frecuencias, lo cual asegura que

VCO se dirige en la dirección

adecuada

4.2 Circuitos específicos

DLL con circuito digital de inicialización

•Se trata de ajustar el retardo de forma que TD+TB=N*Tclk

•Cuando Reset=1 se inicializa el circuito de control digital que selecciona el

número de elementos de retardo necesarios (bloqueo grueso)

•Como TB varia con T y VDD, el lazo de control analógico ajusta TD en función

de dichas variaciones (ajuste fino)

Tema 4 Diseño de elementos CMOS

específicos

1.1.- Circuitos analógicos básicos: capacidad, capacidad de paso, resistencia,

resistencia,

buffer.

2.2.- Circuitos específicos:

– líneas de retardo,

– osciladores controlados por voltaje,

– comparadores de fase,

– PLL,

– DLL.

– Estructuras de E/S:

puertos de alimentación y tierra,

puertos de salida,

puertos de entrada

puertos bidireccionales

puertos triestado .

4.2 Circuitos específicos

Organización global

– El tamaño de un pad se define como el tamaño mínimo para que un cable

se pueda conectar (100(100-150µ

150µm2)

– El espacio entre pads se define como la mí

mínima distancia que deben tener

dos pads para que puedan realizarse las conexiones (150(150-200µ

200µm)

Substrato

Dado

Pad

armazón

4.2 Circuitos específicos

Mayor nº de pads

Colocación de los pads

sobre la superficie del CI

Limitado por pads

Limitado por core

4.2 Circuitos específicos

Conexión mediante cables

Conexión de chip invertido

Cable

Dado

Chip

L

Bolas de soldadura

Cavidad

Montaje

L’

Armazón

Pin

Layers

Interconexión

Sustrato

4.2 Circuitos específicos

Distintos tipos de empaquetamiento

4.2 Circuitos específicos

Pad

100 µm

Puertos de alimentación y tierra

Son los más sencillos y consisten en un

sandwich de layers de metal conectados

al bus

4.2 Circuitos específicos

Pads de Entrada/Salida

Se necesita colocar un buffer grande para disminuir la resistencia de carga

¿Cómo diseñar transistores grandes?

VDD

Drenador

S

Contactos

Multiples

Vin

Vin

Vin

D

G

Vin

Vout

Fuente

S

Puerta

(a) Transistores en paralelo

(b) Transistores circulares

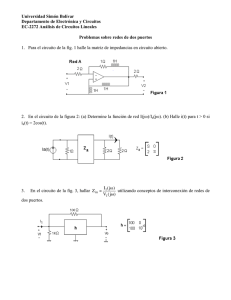

4.2 Circuitos específicos

Pad

GND

100 µm

Out

VDD

In

GND

Out

4.2 Circuitos específicos

Diferentes estructuras de PADs

El voltaje inferior (Vss) debe

colocarse en la pista exterior

4.2 Circuitos específicos

Pads de entrada

Diodos de corte

4.2 Circuitos

específicos

Pads bidireccionales y triestados