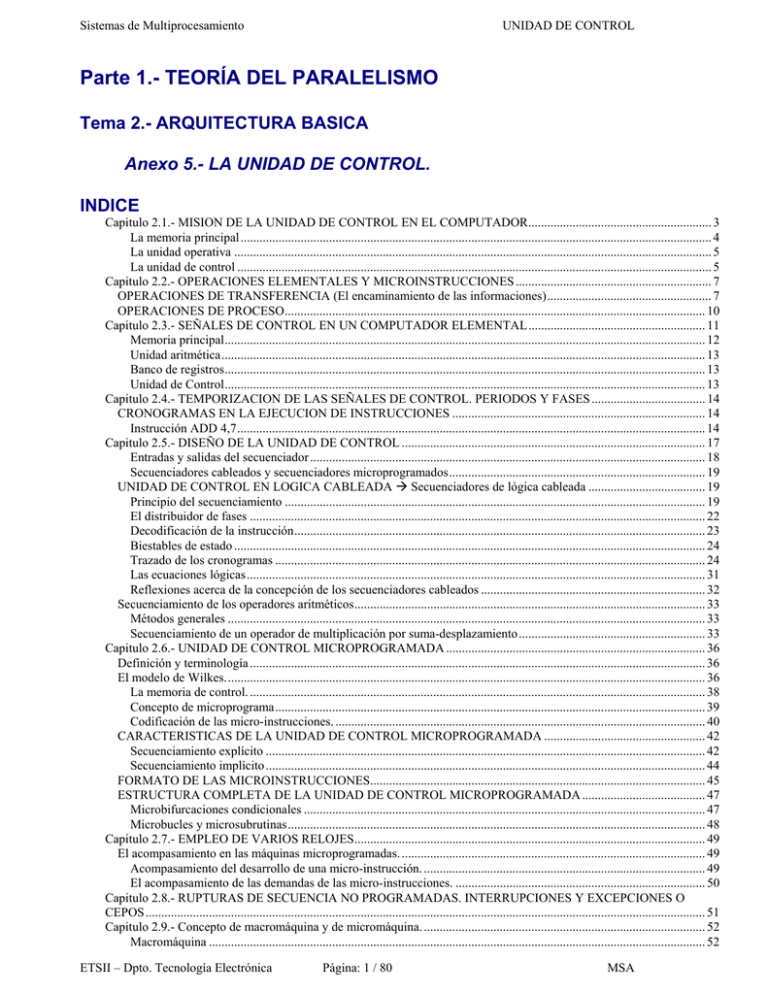

Anexo 5. - Departamento de Tecnología Electrónica

Anuncio