DISEÑO DE PADS ANALÓGICOS: UNA REVISIÓN J. B. Cob

Anuncio

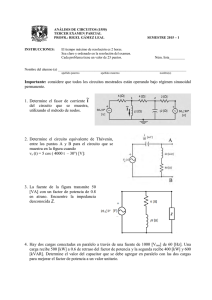

DISEÑO DE PADS ANALÓGICOS: UNA REVISIÓN J. B. Cob-Sulub y F. Sandoval-Ibarra Electronics Design Group CINVESTAV, Guadalajara Unit Prol. López-Mateos Sur 590, 45235 Guadalajara JAL. (México) [email protected] [email protected] RESUMEN El diseño de circuitos integrados es una actividad en la que no solo la atención hacia el diseño del circuito o sistema bajo desarrollo es importante, también lo es el diseño de PADs. Estos últimos, además de proporcionar protección electrostática, son el medio a través del cuál el diseñador puede acceder a los nodos de entrada/salida y, por tal razón, un PAD no debe ser un elemento que limite el desempeño del sistema. Por lo anterior, se presenta una revisión del estado del arte que guarda el diseño de PADs orientado a aplicaciones analógicas, con la intención de elaborar una referencia que sea útil para el principiante y para el diseñador de circuitos integrados. SUMMARY Integrated circuits design is an activity in which not only the design of the circuit or system under development is important but also the design of PADs. The last one gives a circuit's protection under electrostatic discharge because they are the way by which the designer goes to the input/output nodes; that is the reason why PADs have not been a cause to limit the circuit or system performance. According that, a review on PAD design for analog applications has been created with the purpose to write a useful reference for the beginner and for the integrated circuits designer. DISEÑO DE PADS ANALÓGICOS: UNA REVISIÓN J. B. Cob-Sulub y F. Sandoval-Ibarra Electronics Design Group CINVESTAV, Guadalajara Unit Prol. López-Mateos Sur 590, 45235 Guadalajara JAL. (México) [email protected] RESUMEN El diseño de circuitos integrados es una actividad en la que no solo la atención hacia el diseño del circuito o sistema bajo desarrollo es importante, también lo es el diseño de PADs. Estos últimos, además de proporcionar protección electrostática, son el medio a través del cuál el diseñador puede acceder a los nodos de entrada/salida y, por tal razón, un PAD no debe ser un elemento que limite el desempeño del sistema. Por lo anterior, se presenta una revisión del estado del arte que guarda el diseño de PADs orientado a aplicaciones analógicas, con la intención de elaborar una referencia que sea útil para el principiante y para el diseñador de circuitos integrados. 1. INTRODUCCION La gran demanda de sistemas de comunicación personal, de entretenimiento y de información están dictando desde el pasado reciente los productos electrónicos de consumo para bandas de alta frecuencia, lo cual aunado a la necesidad de ofrecerlos a precios competitivos obliga a las empresas y a sus ingenieros de diseño a considerar la tecnología CMOS para desarrollar componentes básicos de RF. Sin embargo, debido a la naturaleza capacitiva de esta tecnología es común enfrentar daños fatales en el desempeño de los circuitos y sistemas por descargas electrostáticas, por ello es imperativo incorporar circuitos especiales de protección. Estos circuitos inevitablemente introducen elementos y efectos parásitos que, además de los efectos introducidos por los bonding pad, degradan y/o limitan el desempeño del circuito integrado. En la práctica, existe un compromiso entre el nivel de protección requerido y los efectos introducidos por parásitas, por lo que, si bien es cierto que las tecnologías actuales pueden operar a frecuencias muy altas, también es cierto que estos desarrollos requieren de una protección mayor debido a que, al disminuir las dimensiones, también disminuye el grosor del óxido de compuerta lo que lo hace más [email protected] susceptible de sufrir un daño. Por esta razón, mientras más pequeña sea la longitud mínima del canal del transistor más cuidados se requiere para diseñar su esquema de protección [1]. Ese hecho obliga a considerar que el esquema de protección no disminuye su dimensión por lo que su efecto estará presente tal y como ocurre en tecnologías de gran canal. En la práctica el bonding pad no reduce su área, la razón es por limitaciones de la infraestructura que realiza el alambrado (a saber el llamado bonding machine) [2]. En la actualidad, esta limitación está generando un nuevo reto a los ingenieros de diseño, el cual consiste en diseñar estructuras que proporcionen la protección requerida a los dispositivos y que, al mismo tiempo, afecten un mínimo el desempeño del sistema. Por lo anterior, este documento presenta una revisión tanto del estado actual que guardan las estructuras de protección a nivel circuito integrado como del desarrollo del bonding pad. Por ello, se proporciona una evaluación de las propuestas existentes, así como los conceptos básicos concernientes a las estructuras de protección y, muy importante, una descripción de los efectos que degradan la operación del sistema bajo análisis y cómo aquellos pueden ser minimizados. 2. PADS ANALOGICOS En tecnologías de circuitos integrados MOS un PAD está constituido por los denominados bonding pad y por una estructura de protección ESD (del inglés ElectroStatic Discharge). Los primeros son el medio a través del cual se tiene comunicación con los nodos de entrada/salida de un circuito integrado, mientras que el segundo es para incorporar un medio de protección ante descargas electrostáticas. 2.1 Bonding pad La Fig. 1a muestra la descripción mencionada. Es claro qué para acceder a la operación del Circuito MOS es fundamental el uso de un bonding pad ya que, para el circuito que se muestra, la comunicación se realizará mediante un probador de puntas. Por tal razón, la dimensión puede ser de 80×80 µm² a 100×100 µm² [3], [4]. Sin embargo, existe equipo de caracterización a nivel oblea que requiere que la dimensión sea de 120×120 µm². Ahora bien, cada vez que un diseñador tiene acceso a una tecnología de fabricación, él/ella saben qué equipo de caracterización usarán, siendo esta última quién dicta la dimensión del bonding pad. En la práctica, cuando el circuito integrado está incorporado en un encapsulado, la comunicación al circuito se hace a través de pines. Estos últimos se comunican con cada PAD mediante una conexión física, es decir, usando un medio conductor. Ejemplo de ello es el circuito mostrado en la Fig. 1b, donde se muestra (mediante una flecha) sólo una de las conexiones realizadas a través de un proceso llamado bonding. Por cuestiones de espacio, esta ilustración no muestra el encapsulado. Con relación al wire bonding (o alambrado) es prudente mencionar que éste se realiza con calor y a través de presión mecánica. Del punto de vista de la confiabilidad del circuito integrado, es recomendable que cada bonding pad se diseñe mediante una interconexión de los niveles metálicos de la tecnología que se usa. Con este procedimiento se asegura que al levantar el brazo mecánico el bonding pad no se desprenderá. Sin embargo, varias consideraciones eléctricas y de desempeño deben considerarse en este tipo de diseño: - La capacitancia parásita del bonding pad está determinada por el área de la placa metálica inferior y por el substrato. Esta capacitancia puede ser hasta de 0.67pf para un área de 96×96µm² en tecnología CMOS de 0.35µm [2]. - El bonding pad descrito es conocido como estándar. En éste el ruido de substrato se acopla directamente a las trayectorias de la señal a través de la capacitancia parásita. - Para minimizar el efecto del ruido, y sí la tecnología cuenta con mas de dos niveles de metalización, una opción es diseñar el bonding pad con los niveles superiores de metal. Este es el denominado high frequency bonding pad [5]. Finalmente, en esta opción, el nivel inferior de metal estaría conectado al potencial más negativo. Otros problemas que degradan el desempeño del circuito a frecuencias altas de operación son los relacionados con pérdidas de la señal por efectos del substrato y/o debido al fenómeno cross-talk. En la literatura se ha reportado una nueva estructura que permite sanar estos problemas [4]. La idea básica es formar el bonding pad con los metales superiores, de forma tal que éstos se conectan entre sí a través de una alta densidad de vías colocadas en el perímetro. En la práctica, muchas vias aseguran una alta adherencia mecánica con lo que el desprendimiento del bonding pad no ocurrirá. Bajo esta estructura se realiza una difusión p+ en un pozo N. Debido a ello hay dos capacitancias de unión que, al estar conectada en serie a la capacitancia del bonding pad, se obtiene una capacitancia total menor. Por otro lado, tal y como se muestra en la Fig.2, para minimizar las pérdidas por substrato se incluye un gran número de contactos a él. Todos ellos polarizados al potencial más negativo (VSS). Otra opción de diseño que permite reducir la capacitancia consiste de una estructura metálica multicapa (ver Fig. 3). A diferencia del diseño anterior, todos los niveles metálicos están conectados (ellos forman el bonding pad) para evitar el posible desprendimiento del mismo por el mecanismo descrito con anterioridad, las placas metálicas, excepto la metalización superior, no son un cuadrado continuo sino un cuadrado con un determinado patrón geométrico [2]. Esta característica minimiza la capacitancia parásita a substrato e incrementa la adherencia mecánica del wire bonding, obteniendo un rendimiento alto en la integridad física del bonding pad. Para una descripción de los diferentes patrones geométricos propuestos, se recomienda al lector acudir a la referencia [6]. Fig. 1 Microfotografía que muestra el bonding pad y su protección ESD (a), así como el alambrado para acceder a los nodos de entrada/salida del circuito integrado (b). 2.2 Protección electrostática Estas son estructuras que se incorporan al bonding pad, por lo qué ambos elementos constituyen lo que en este documento se denomina PAD. Un circuito ESD sirve para brindar protección a los circuitos y sistemas integrados ante descargas electrostáticas. Por ejemplo, cuando un involucrada es relativamente pequeña (del orden de µJ) [8], sin embargo si la descarga tiene lugar a través de los "pines" de un circuito integrado, la corriente y la energía disipada son lo suficientemente grande como para inducir una reducción en el desempeño y/o para generar una falla total en el circuito. La descarga ocurre en un tiempo muy corto, típicamente del orden de 10- a 100-ns con corrientes de 1- a 10-A. Estos valores dependen fundamentalmente de las condiciones de descarga, las cuales están incorporadas en el modelo denominado HBM (del Inglés Human Body Model). En la práctica, para caracterizar los circuitos ESD se usa una aproximación eléctrica equivalente del HBM consistente de un resistor de 1.5 kΩ en serie con un capacitor de 100 pF. Esta aproximación es el circuito de entrada del dispositivo bajo prueba [7], [10] (ver Fig. 4a). elevado potencial se presenta en el bonding pad, el circuito de protección es un camino de baja impedancia que permite desviar la corriente generada, evitando con ello que la corriente dañe al circuito. Sin embargo, hay efectos no deseados que pueden dar lugar a degradar el desempeño del circuito que se protege. Uno de éstos es el debido a la distorsión en circuitos analógicos de alta velocidad, fundamentalmente en circuitos de entrada simple. La razón de esta no idealidad es la capacitancia no-lineal dependiente de voltaje asociada a la estructura de protección. - La segunda fuente de ESD es la que tiene lugar en equipos que realizan pruebas eléctricas al circuito integrado para diversos propósitos. Estos equipos pueden acumular cargas estáticas debido a un mal sistema de aterrizado, generando con ello la transmisión de carga a través de los pines de entrada/salida del circuito integrado. Aún cuando la carga acumulada puede ser mayor que la del HBM los voltajes asociados son típicamente menores. En la práctica, la descarga es un pulso de corta duración pero de muy alta magnitud. A este mecanismo se le conoce como MM (del Inglés Machine Model). Al igual que la aproximación HBM, a esta fuente de ESD se le modela mediante el circuito eléctrico equivalente mostrado en la Fig. 4b [7], [10]. - El tercer mecanismo en importancia ocurre cuando el circuito integrado acumula carga durante el transporte, desplazamiento y/o por contacto con superficies o materiales altamente cargados electrostáticamente. Cuando el circuito integrado se descarga a través de sus pines, genera una gran corriente que circula por sus interconexiones internas. Esta corriente puede dar lugar a altos voltajes que provocan daños a los diversos materiales dieléctricos del dispositivo o circuito en cuestión. A este mecanismo se le conoce como CDM (del Inglés Charged Device Model) [7], [10]. Fig. 2 Sección transversal que muestra el alambrado (bond wire) al bonding pad y la incorporación de dos regiones de agotamiento para minimizar la capacitancia parásita total. Fig. 3 Corte de sección transversal que muestra el diseño de un bonding pad en tecnología de tres niveles de metalización. La incorporación de patrones geométricos en los niveles inferiores (1 y 2) minimizan la capacitancia parásita total. 3. CONCEPTOS BASICOS DE PROTECCION ESD Existen tres fuentes principales de carga y descarga electrostáticas. A saber: - Una persona caminando sobre un piso de superficie sintética puede acumular hasta 20kV. Este persona se "descarga" al entrar en contacto con un objeto conductor que sea lo suficientemente grande y/o que esté a un potencial menor (respecto al potencial del individuo) con lo que se intercambia la mayoría de la carga electrostática. La cantidad de energía El daño que se produce en circuitos integrados por descargas electrostáticas se evidencía, en buen porcentaje, por la generación de calor; consecuencia de un flujo intenso de corriente. Por ello las estructuras ESD se diseñan para soportar altos niveles y, muy importante, presentar adecuada sensibilidad. Esta última se cuantifica en voltios y su valor depende del dispositivo bajo estudio y de la aproximación usada. Por ejemplo, en [9] se reporta una estructura de protección ESD que soporta hasta 6kV en HBM y 400V para MM. 4. TECNICAS DE PROTECCION ESD Durante mucho tiempo se ha invertido todo tipo de recursos para desarrollar técnicas que permitan incrementar la eficiencia de las estructuras ESD. Uno de varios conceptos que dan lugar al valor agregado de la protección ESD es incrementar su eficiencia mediante la optimización de sus dimensiones físicas. Al ser más eficientes se requiere menor área para brindar el nivel de protección requerido, lo que reduce en un alto porcentaje los efectos no deseados por los elementos parásitos. A manera de ejemplo, suponer que se tiene un ancho de banda de interés. Lo que no se requiere es que los elementos parásitos constituyan una constante de tiempo que represente un circuito pasa-bajas que limite el ancho de banda de trabajo. Reducir el valor de la capacitancia parásita representa alejar el polo a frecuencias mayores, es decir, situarlo más allá de la máxima frecuencia de interés. Otro ejemplo a mencionar es el relacionado a la distorsión armónica, el cual es un efecto nocivo para los circuitos analógicos. elementos del circuito conectados en serie; esta técnica es poco utilizada en aplicaciones de alta frecuencia debido a sus valores resistivos, ya que alteran el producto RC de la red. En cuanto a la técnica Gate-Coupling, ésta incrementa la eficiencia de un GGNMOS proporcionando polarización de la compuerta durante un evento ESD reduciendo con esto el voltaje de encendido (Vt1), para un GGNMOS en general Vt1 es mayor que el voltaje de falla (Vt2), debiendo suceder primero el encendido seguido por el snapback, y solo al incrementarse de nuevo el voltaje hasta alcanzar Vt2 sobreviene la falla, esto dificulta la uniformidad del encendido de todos lo fingers de una estructura interdigital, ya que al encender el/los primeros estos descargan toda la corriente ESD previniendo que los otros fingers enciendan, al ser menor el voltaje de falla esta sobreviene antes que los otros puedan encender, no sucediendo lo mismo para un Vt1 menor que Vt2. Al incrementar el numero de fingers activos se incrementa la eficiencia del dispositivo. El acoplamiento de compuerta se logra a través de la capacitancia de traslape o, alternativamente, incorporando elementos capacitivos externos. Por otro lado, la técnica RC-Coupling discrimina el pulso ESD de las señales de interés (con otras frecuencias asociadas) usando un circuito RC, el pulso discriminado se aplica al dispositivo de protección de forma tal que acelera el proceso de encendido, lo que a su vez incrementa la eficiencia de la protección ESD. El filtro es entonado para responder a aquellos anchos de pulso que son significativamente mas cortos que la escala de tiempo del encendido de la fuente de poder. Finalmente, la técnica Substrate-Triggering descarga el pulso ESD en el sustrato incrementando el potencial del sustrato local al MOSFET Vsub (=Isub×Rsub) lo que contribuye al encendido del transistor parásito npn formado por las regiones n+ del drenador/fuente y el sustrato p, lo cual reduce el voltaje de encendido del dispositivo y establece un incremento en el manejo de corriente, obteniendo un aumento en la eficiencia de la protección ESD [7]. Fig. 4 Aproximaciones HBM (a) y MM (b) útiles para evaluar el desempeño del circuito de protección ESD. 5. DISPOSITIVOS DE PROTECCIÓN Algunas de las técnicas de protección ESD que se usan en tecnologías CMOS son las denominadas ResistorBallasting, Gate-Coupling, RC-Coupling y SustrateTriggering. La primera de ellas hace uso de resistores en cada elemento del circuito para mejorar la distribución y uniformidad de la corriente. Típicamente un resistor integrado tiene una característica I-V no lineal, sin embargo para voltajes bajos la corriente incrementa linealmente pero, para voltajes altos, la corriente tiende a saturación. De acuerdo a este comportamiento, conforme la corriente se satura la caída de voltaje a través del resistor se incrementa, lo que previene el sobrevoltaje de otros Varios son los dispositivos que se usan en las estructuras de protección ESD: el transistor MOS, los diodos de unión y los SCR. Los transistores MOS se usan comúnmente en la red grounded-gate NMOS. En tecnologías CMOS submicrométricas la corriente de segundo encendido varía de 2- a 10-mA/µm de ancho del canal, lo que resulta en un MOSFET de 200- a 1000-µm para alcanzar un nivel de protección de 4kV en la aproximación HBM [7]. El uso de diodos como dispositivos ESD es muy común pero, en la actualidad, estos dispositivos están adquiriendo una mayor importancia en el diseño de estructuras ESD como consecuencia de las limitaciones que imponen los circuitos integrados de alta frecuencia, es decir, por los valores de los elementos parásitos que se pueden tolerar (200fF en un PAD a 2 GHz [15]). Además existen varias clases de diodos que se usan como estructuras de protección ESD. Algunos de ellas son los diodos obtenidos mediante la introducción de impurezas donadoras para obtener una región N+ en substratos P; también diodos a partir de regiones P+ en pozo N; diodos de polisilicio [15], diodos de compuerta de poly y diodos STI [16]. Un parámetro clave en esta clase de diodos es la baja resistencia serie. Esta se obtiene mediante diseños de perímetros grandes lo que se traduce en parásitas importantes [7]. Como todo diseño, el diseñador se enfrenta a evaluar las ventajas y desventajas de cada propuesta. Los SCR que se usan en las redes ESD se basan en la retroalimentación regenerativa β npnβnpn iniciada por el pulso ESD. Estos dispositivos de protección son muy eficientes en área; por ejemplo en [11] se menciona que es posible obtener una robustez de 2kV en HBM con una capacitancia total de 100 fF. No obstante, estos dispositivos poseen voltajes de encendido relativamente altos (del orden de 15.32V para SCR y 7.5V para LVSCR) lo que puede originar un daño al circuito antes de que éste entre en operación (estado ON) [17]. Por esta razón, conforme la tecnología permite reducir las dimensiones del canal se requiere usar nuevos tipos de SCR. Ejemplo de ello son los denominados n-well triggered MLSCR, difusión n-triggered MLSCR, n-channel triggered LVTSCR y RC triggered-SCR. En tecnologías CMOS modernas, donde el objetivo es minimizar el producto βnpnβnpn, el uso de SCR es limitado [7]. 6. CIRCUITOS MOS, ESD Y SUS EFECTOS Las interacciones entre el circuito y la estructura ESD pueden clasificarse en primera aproximación como influencias del circuito a la estructura ESD e influencias de la estructura ESD al circuito. La primera de ellas puede observarse en los circuitos de señal mezclada donde el ruido de conmutación puede acoplarse a las secciones de entrada/salida y provocar la activación de las estructuras ESD, llevando con ello a un mal funcionamiento de estas estructuras y, por consiguiente, generar un mal funcionamiento de todo el circuito. Esto puede entenderse por medio de las observaciones realizadas en [12], donde se indica que la corriente de desplazamiento, provocada por una variación en la señal de voltaje de entrada dV/dt, y por los efectos asociados a la fluctuación en la señal entrada (dI/dt) puede acoplarse en los dispositivos ESD a través de los capacitores y elementos inductivos parásitos, causando la activación incorrecta de las estructuras ESD. La generación de estas activaciones no deseadas se hace aparente conforme hay un incremento en la frecuencia de operación del circuito bajo estudio y/o análisis. Por otro lado, las influencias de las estructuras ESD al circuito se componen de varios efectos parásitos. De éstos el mas perjudicial viene de los elementos capasitivos asociados con las estructuras ESD. Es a través de estas capacitancias parásitas por el cual ocurre el acoplamiento de señales de ruido no deseadas incidentes en los pines de entrada/salida hacia el substrato, lo que puede provocar problemas de ruido en varios de los bloque que constituyen el circuito integrado. Además, en circuitos integrados MOS de señal mezclada, los grandes niveles de ruido digital pueden acoplarse en las secciones de protección ESD y por lo tanto en los pines de entrada/salida y fluir de nuevo en las trayectorias de la señal, llevando en consecuencia una degradación del desempeño del circuito. Aún más, esta capacitancia y la resistencia asociada introducen un retardo en la propagación de la señal, causando un "malfuncionamiento" del reloj. Esa es la razón por la cual algunos diseños consideran la introducción de un circuito sensor que ante tal retardo modifique la frecuencia del reloj hasta un valor en el que el procesamiento ocurra de manera satisfactoria. Esta técnica depende de varias variables y es, en la práctica, una propuesta aún en desarrollo. Esa misma capacitancia ejerce una modificación al acoplamiento de impedancias normalmente requerida (50 Ω) en los diseños de los puertos de entrada y salida en los circuitos de RF. Cuando el acoplamiento no es el adecuado, se afecta negativamente la eficiencia de transferencia de potencia y el ancho de banda útil del circuito. Los dispositivos ESD generan ruido por sí mismos; este ruido intrínseco puede afectar el valor de la razón señal-aruido en circuitos de RF. Este ruido, llamado también auto generado, es inherente a los dispositivos ESD y siempre existe por lo que resulta conveniente su consideración en el diseño de circuitos de bajo ruido [12]. Por otro lado, todas las estructuras ESD están caracterizadas por capacitancias parásitas no lineales. Esta no linealidad ejerce una influencia desfavorable al desempeño del circuito al introducir distorsión armónica, distorsión que incluso puede provocar que un ADC diseñado originalmente para obtener una resolución de 12 bits, obtenga tan solo una precisión de 10 bits [13]. 7. CONCLUSIONES En tecnologías de circuitos integrados un PAD está formado por el bonding pad y por una estructura de protección ESD. Este elemento es de vital importancia ya que una incorrecta propuesta puede dar lugar a que los beneficios y/o ventajas de un diseño completamente integrado se pierdan. En la práctica, existe un compromiso entre el nivel de protección requerido y los efectos introducidos por parásitas, por lo que, si bien es cierto que las tecnologías actuales pueden operar a frecuencias muy altas, también es cierto que estos desarrollos requieren de una protección mayor debido a que, al disminuir las dimensiones, también disminuye el grosor del óxido de compuerta lo que lo hace más susceptible de sufrir un daño. Por lo anterior en este documento se presentó una revisión del estado actual que guardan las estructuras de protección a nivel circuito integrado así como el desarrollo del bonding pad. Por ello, se proporcionó una descripción de las propuestas existentes, así como los conceptos básicos concernientes a las estructuras de protección y, muy importante, una descripción de los efectos que degradan la operación del sistema bajo análisis y cómo aquellos pueden ser minimizados. Agradecimientos Los autores agradecen al árbitro anónimo sus recomendaciones y notables señalamientos que permitieron clarificar la descripción técnica de este trabajo. Uno de los autores (J.B. Cob-Sulub) agradece el apoyo económico otorgado por CONACyT-México. Esta investigación se realizó con financiamiento del CONACyT-Mexico (convenio 38951-A). Referencias [1] M.-D. Ker, T.-Y. Chen, C.-Y. Wu, H.-H. Chang, “ESD protection design on anlog pin with very low imput capacitance for high-frecuency or current-mode applications”, IEEE Journal of Solid-Estate Circuits, Vol 35, No 8, August 2000, pp 1194-1199. [2] M.-D. Ker, H.-C. Jiang,C.-Y. Chang, “Design of lowcapacitance bond pad for high-frecuency I/O applications in CMOS integrated circuits”, proceedings of the IEEE International ASIC/SOC Conference, 2000, pp. 293-296. [3] http://intrage.insa-tlse.fr/~etienne/Microwind/book.html [4] S. Lam, W. H. Ki, M. Chan, “High-isolation bonding pad with depletion-insulation structure for RF/Microwave integrated circuits on bulk silicon CMOS”, IEEE MTT-S International Microwave Symposium Digest, pp. 677-680, June 2-7, 2002, Washington, USA. [5] J. Shorb, X. Li, and D.J. Allstot, "A resonant pad for ESD protected narrowband CMOS RF applications," ISCAS2003, Vol. 1 , pp. I61 -I64, 25-28 May 2003. [6] J. J. Peng, M.-D. Ker, N.-M. Wang, and H. C. Jiang, “Layout design on bond pads to improve the firmness of bond wire in packaged IC products”, Proc. of 1999 International Symposium on VLSI Technology, System, and Application, Taiwan, June 8-10, 1999, pp.147-150. [7] S. H. Voldman, “The State of the Art of Electrostatic Discharge Protection: Physics, Technology, Circuits, Design, Simulation, and Scaling,” IEEE J. of Solid-State Circuits, vol. 34, no. 9, pp. 1272-1282, 1999. [8] A. Amerasekera, C. Duvvury, ESD in silicon integrated circuits, Chichester, England Wiley, 1995. [9] M.-D. Ker, T.-Y. Chen, C.-Y. Wu, H.-H. Chang, “Design and analysis of the on-chip ESD protectioncircuit with a constant input capacitance for high-precision analog applications”, Proceedings of the IEEE Int. Symposium on Circuits and Systems, Vol. 5, 2000, pp. 61–64. [10] http://palgong.knu.ac.kr/~necst/upload/pds_63_four.pdf [11] M. K. Radhakrishnan, V. Vassilev, B. Keppens , V De Heyn, M. Natarajan, G. Groeseneken, "ESD Reliability Issues in RF CMOS Circuits", Invited paper, in: Proc. International Workshop on Semiconductor devices, 2001. pp. 551-556. [12] A. Wang, H. Feng, R. Zhan, G. Chen and Q. Wu, “ESD Protection Design for RF Integrated Circuits: New Challenges”, Invited, Proc. IEEE Custom IC Conf. (CICC), pp.411-418, 2002. [13] I.E. Opris, Bootstrapped pad protection structure, IEEE J. Solid-State Circuits 33 (1998) 300–301. [14] M.-D. Ker, T.-Y. Chen, “Layout design to minimize voltage-dependent variation on input capacitance of an analog ESD protection circuit”, Journal of Electrostatics, vol. 54, pp. 73-93, 2002. [15] M.-D. Ker, T.-Y. Chen, and C.-Y. Chang, “ESD protection design for CMOS RF integrated circuits”, Proc. of the 23rd Electrical overstress / Electrostatic Discharge Symposium (EOS/ESD), Oregon, USA, Sept. 9 - 13, 2001, pp. 346-354. [16] M.-D. Ker and C.-M. Lee, “Interference of ESD protection diodes on RF performance in giga-Hz RF circuits”, Proc. of 2003 IEEE International Symposium on Circuits and Systems (ISCAS), pp. I297-I300, Thailand, May 25-28, 2003. [17] H. Feng, R. Zhan, G. Chen, Q. Wu, X. Guang, H. Xie and A. Wang, “Bonding-Pad-Oriented on-chip ESD Protection Structures for ICs”, ISCAS2003, Vol. 1 , pp. I741 -I744, 25-28 May 2003.