Descripción de la funcionalidad

Anuncio

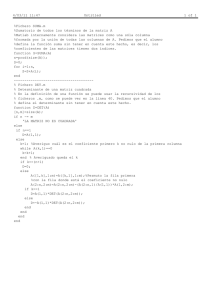

Tema 3: Descripción de la funcionalidad 3.1 Introducción/Repaso 3.2 Concepto de concurrencia 3.3 Procesos 3 4 Diseño de circuitos combinacionales 3.4 3.4.1. Sentencias concurrentes 4.4.2. Descripción mediante procesos Tema 3: Descripción de la funcionalidad 3.1 Introducción/Repaso p 3.2 Concepto de concurrencia 3.3 Procesos 3 4 Diseño de circuitos combinacionales 3.4 3.4.1. Sentencias concurrentes 4.4.2. Descripción mediante procesos Introducción -- Multiplexor de dos entradas entityy mux21 is port ( e1, e2: IN std_logic; sel: IN std_logic; o1: OUT std_logic); std logic); end mux21; arquitecture A of mux21 is b i begin process(e1,e2, sel) begin if (sel=‘0’) ( l ‘0’) then th o1 <= E1; else o1<= 1< e2; 2 endif; end process; end d A; A Introducción. Formas de describir una ARCHITECTURE Dos formas distintas : 1. Órdenes concurrentes: órdenes en parelelo. parelelo Ejecución de 2 Utili 2. Utilizando d process: Dentro D t d de un process las órdenes se ejecutan de forma secuencial. secuencial Es posible E ibl combinar bi ambas b en una misma ARCHITECTURE Tema 3: Descripción de la funcionalidad 3.1 Introducción 3.2 Concepto de concurrencia 3.3 Procesos 3 4 Diseño de circuitos combinacionales 3.4 3.4.1. Sentencias concurrentes 4.4.2. Descripción mediante procesos Concepto de concurrencia ARCHITECTURE Sentencias concurrentes: Órdenes independientes que se ejecutan en paralelo. A<=C and D or G; F <= < A when E='0' E 0 else 'H'; H ; PROCESS: Conjunto de órdenes que se ejecutan de forma secuencial. process(e1,e2, sel) begin if (sel='0') then o1 <= E1; else o1<= e2; endif; end process; INSTANCIAS A COMPONENTES: COMPONENTES Cada C d componente será un bloque que funcionará en paralelo cont1: contador GENERIC MAP (N=>7) PORT MAP ( …………….) Por naturaleza,, todos los elementos de un circuito funcionan de forma concurrente concurrente. Todas las sentencias fuera de un process se ejecutan d forma de f paralela. l l El orden de las sentencias no es importante. p Un componente se entiende como otra sentencia concurrente concurrente. Un process se comporta externamente como una sentencia concurrente. Tema 3: Descripción de la funcionalidad 3.1 Introducción 3.2 Concepto de concurrencia 3.3 Procesos 3 4 Diseño de circuitos combinacionales 3.4 3.4.1. Sentencias concurrentes 4.4.2. Descripción mediante procesos Proceso El bloque q process p como unidad básica de ejecución. j nombre:process(e1,e2, nombre:process(e1 e2 sel) Li de Lista d sensibilidad ibilid d variable ……………… Declaración variables begin if (sel=’0’) then Comportamiento p o1<= 1< e1; 1 else o1<= 1 e2; 2 Todos los bloques process son sensibles a sus endif; entradas como las puertas lógicas a los suyos. Todos los bloques process se ejecutan en end d process; paralelo como las puertas lógicas de un circuito. Proceso. Lista de sensibilidad El p proceso oceso se ejecu ejecuta ae en su totalidad o a dad cua cuando do ca cambia ba algunas señal de la lista de sensibilidad proc1: process (a,b,c) begin x <= a and b and c; end process; proc2: process (a,b) begin x <= a and b and c; end process; Desde el punto de vista de simulación, ambos procesos son muy diferentes. El proc2 2 no es sintetizable i t ti bl (faltará (f lt á un latch l t h para c que es sensible a ambos flancos de a y b), por tanto: – El programa de síntesis añadirá la señal c a la lista de sensibilidad para poder asociar un circuito al código. – El programa de síntesis produce un mensaje de error. Proceso. Lista de sensibilidad CONCLUSIÓN: En CONCLUSIÓN E un código ódi VHDL para síntesis de un proceso combinacional, en la lista de sensibilidad deben incluirse todas las señales que afecten a la evaluación del proceso. • • Un proceso sin lista de sensibilidad se estaría ejecutando siempre, por tanto el simulador nunca avanzaría. Si una señal de la lista de sensibilidad cambia el proceso es evaluado sucesivamente hasta que todas las señales sensibles se estabilicen. Proceso. Asignación g de señales Todas la expresiones de un proceso se resuelven con el valor actual de las señales. Las asignaciones se hacen efectivas cuando se termine la evaluación del proceso. Todas las señales serán actualizadas con el último valor asignado dentro del proceso. El proceso vuelve a evaluarse si se ha modificado alguna l señal ñ l de d su lista li t sensible. ibl Todos los procesos cuya lista sensible ha sido alterada y todas las órdenes concurrentes se ejecutan hasta que se alcanza un estado de equilibrio (no hay más cambios). Proceso. Asignación g de señales ((ejemplo j p 1)) Diferentes e e es opc opciones o es pa para a implementar pe e a e el mux2 u process(e1,e2, sel) begin if (sel=’0’) then o1<= e1; else l o1<= e2; endif; end process; process(e1,e2, sel) begin o1<= e1; process(e1,e2, sel) begin if (sel=’1’) then if (sel=’1’) then o1<= e2; endif; o1<= e1; end process; o1<= e2; endif; end process; – INCORRECTO – O1 siempre i valdrá ld á e11 Procesos. Declaración de variable U a variable Una a ab e só sólo o tiene e e se sentido do de dentro o de u un proceso (por eso se declara dentro del proceso). No trascienden fuera del proceso. Las variable se actualizan en el momento en que se hace la asignación dentro del proceso, al contrario que las l señales, ñ l que lo l hacen h una vez ha h terminado t i d el proceso. Señales representan cables del diseño, diseño variables representan la salida de “sub-circuitos”, utilizado en los calculos de un proceso. Se suelen usar para cálculos aritméticos. Se recomienda que sólo se utilicen cuando sean realmente útiles. Procesos. Declaración de variable asig: PROCESS(b,c) VARIABLE a: std_logic; BEGIN a:= b and c; d<= a xor b; END PROCESS asig; Procesos. Diferencia entre variables y señales ( j (Ejercicio) ) Ej: j PROCESS ( (control,senal , _a) ) VARIABLE var_a: integer; BEGIN Var_a:=4; Senal_a<=4; Senal r1< var a; Senal_r1<=var_a; Senal_r2<=senal_a; IF ( (control = ’0’) ) THEN Senal_a <= 3; ELSE Senal_a <= 2; END IF; END PROCESS Ej_variable_v_señal; Ej variable v señal; Tema 3: Descripción de la funcionalidad 3.1 Introducción 3.2 Concepto de concurrencia 3.3 Procesos 3.4 Diseño de circuitos combinacionales 3.4.1. Sentencias concurrentes 4.4.2. Descripción mediante procesos Tema 3: Descripción de la funcionalidad 3.1 Introducción 3.2 Concepto de concurrencia 3.3 Procesos 3 4 Diseño de circuitos combinacionales 3.4 3.4.1. Sentencias concurrentes 4.4.2. Descripción mediante procesos Sentencias concurrentes. Asignación g simple p señal_destino <= señal_origen; Deben ser del mismo tipo (integer, std_logic, etc) señal destino puede ser: señal_destino – Señal – Puerto: OUT, INOUT (y BUFFER) señal_origen puede ser: – Señal – Puerto: IN, INOUT ( y BUFFER) PUEDEN USARSE DENTRO O FUERA DE UN PROCESS Sentencias concurrentes. Ecuaciones lógicas g Operador Ejemplo NOT a <= NOT b; AND, NAND a <= b AND c; OR,NOR,XOR a <= b OR c AND d; PUEDEN USARSE DENTRO O FUERA DE UN PROCESS Sentencias concurrentes. Ejemplo j p library IEEE; use IEEE.std_logic_1164.all; entity mux21 is port ( e1, e2: IN std_logic; sel: IN std_logic; _ o1: OUT std_logic); end mux21; arquitecture A of mux21 is begin o1 <= e1 and not not(sel) (sel) or e2 and sel; end A; Sentencias concurrentes. WHEN …. ELSE …. Señal Destino <= Expresión1 WHEN Condición ELSE Expresión2; Señal Destino <= Expresión1 WHEN Condición1 ELSE Expresión2 WHEN Condición2 ELSE Expresión3 WHEN Condición3 ELSE – .............. ExpresiónN WHEN CondiciónN ELSE Expresión; NO PUEDEN USARSE DENTRO DE UN PROCESS Sentencias concurrentes. WHEN …. ELSE …. library IEEE; use IEEE.std_logic_1164.all; entity mux21 is port ( e1, e2: IN std_logic; sel: IN std_logic; _ o1: OUT std_logic); end mux21; arquitecture A of mux21 is begin o1 <= e1 when sel=’0’ else e2; end A; Sentencias concurrentes. WITH … SELECT ... WITH expresión_selección SELECT Señal Destino <= Expresión1 WHEN Valor_Selección1, Valor Selección1 Expresión2 WHEN Valor_Selección2, –... ExpresiónN WHEN OTHERS; WITH sel SELECT o1 <= e1 WHEN ‘0’, e2 WHEN OTHERS; NO PUEDEN USARSE DENTRO DE UN PROCESS Tema 3: Descripción de la funcionalidad 3.1 Introducción 3.2 Concepto de concurrencia 3.3 Procesos 3 4 Diseño de circuitos combinacionales 3.4 3.4.1. Sentencias concurrentes 4.4.2. Descripción mediante procesos IF THEN ELSIF ELSE IF condición 1 THEN Consecuencia 1; ELSIF condición 2 THEN Consecuencia 2; ELSIF ... THEN ... ELSE Consecuencia; END IF; NO PUEDEN USARSE FUERA DE UN PROCESS IF THEN ELSIF ELSE arquitecture A of mux21 is begin g process(e1,e2, sel) begin if (sel (sel=‘0’) 0 ) then o1 <= e1; else o1<= e2; o1< endif; end process; end A; CASE WHEN CASE objeto IS WHEN caso1 => Código1; g ; WHEN caso2 => Código2; WHEN caso3 => Código34; WHEN OTHERS => > Código; END CASE; NO PUEDEN USARSE FUERA DE UN PROCESS CASE WHEN arquitecture A of mux21 is begin g process(e1,e2, sel) begin case sel is when ’0’ => o1<=e1; when others => > o1<=e2; end case; end process; end A; – WHEN OTHERS es obligatorio si no están cubiertos todos los casos Generación de LATCHES Ej. j Multiplexor p 3x1 ¿Qué Q é ocurre sii una sentencia condicional se deja incompleta? Se genera un LATCH Sentencias condicionales incompletas. No se define la condición (selector=”11”) ( ) Programación if (selector=”00”) then salida<=entrada_0; elsif (selector=”01”) then salida<=entrada_1; _ elsif (selector=”10”) then salida<=entrada_2;; endif; Circuito secuencial Sentencias condicionales incompletas. Circuito con un latch Ocupa más área No realiza la función lógica: – ¡¡Es E sensible ibl a pulsos l !! Sentencias condicionales incompletas. Código g correcto Descripción if (selector=“00”) then salida<=entrada_0; elsif (selector=“01”) (selector “01”) then salida<=entrada_1; elsif l if (selector=“10”) ( l t “10”) then th salida<=entrada_2; else l salida<=entrada_2; end d if; if Circuito combinacional bi i l Circuitos combinacionales y secuenciales. Conclusiones Los circuitos combinacionales deben estar completamente especificados. p q que: Se ggenera una celda de memoria siempre – No se especifica el valor de la salida para todos los posibles valores de las entradas Un latch es un circuito muy sensible a pulsos y timing: – Sólo debe ser utilizado en casos concretos.