RESUMEN

Anuncio

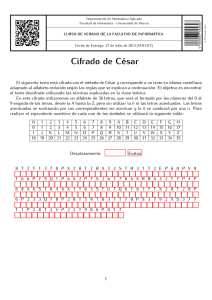

LCEL Sistema de difusión selectiva con cifrado RESUMEN El principal objetivo de esta práctica es diseñar y construir un sistema de envío de audio desde un emisor a una serie de receptores, implementados en uno solo, con la capacidad de elegir el receptor y de enviar la señal de audio cifrada o no. Para ello el sistema estará dividido en dos grandes módulos, emisor y receptor, y cada uno de estos dos en subbloques que a su vez pueden catalogarse en digitales y analógicos. A la hora de trabajar lo más cómodo será abordar cada subbloque por separado, diseñándolos y probándolos de manera independiente. Primero comenzaremos por la parte digital, continuando por la analógica, y reservando para el final la unión de ambas. La construcción inicial del diseño se realizará sobre placas de inserción, utilizando siempre que sea posible integrados que ahorren espacio y complejidad al circuito. Una vez depurado el mismo volveremos a construirlo, esta vez con un montaje wirewrapping para minimizar el espacio y obtener mayor robustez y fiabilidad. Memoria final Página 1 de 60 LCEL Sistema de difusión selectiva con cifrado INTRODUCCIÓN Como ya hemos comentado, la función principal de nuestro diseño será el envío de mensajes de audio desde un centro emisor a una serie de receptores, cada uno con un código distinto. Desde el emisor elegiremos sobre qué receptor queremos actuar (para simplificar el diseño supondremos un único receptor en el que podremos variar el código de su dirección para que coincida o no con la elegida en el emisor). Además, desde el centro emisor también podremos escoger si queremos enviar la señal cifrada o no. El cifrado lo realizaremos mediante la inversión espectral en frecuencia, que logra una señal con el mismo ancho de banda que la original, pero invertida en frecuencia. Es un método bastante sencillo, como más adelante veremos. A su vez, desde este centro emisor decidiremos si queremos transmitir la señal (abrir el canal de comunicación con el receptor) o no. El canal de comunicación entre ambos será un cable físico. También hemos comentado que para facilitar la tarea del diseño, trabajaremos con bloques que probaremos por separado para finalmente integrarlos (véase ilustración). Memoria final Página 2 de 60 LCEL Sistema de difusión selectiva con cifrado Arquitectura del sistema emisor: La arquitectura del emisor se muestra en la figura que sigue: Describiremos cada parte, que detallaremos a lo largo de esta memoria. - Para resumir lo dicho hasta ahora, desde el sistema emisor el operario puede decidir el código del receptor que desea que reciba la señal, si la quiere enviar cifrada o no y cuándo quiere abrir el canal para transmitir. Todo ello lo realizará desde la unidad de entrada. - Para observar la selección realizada, tendremos la unidad de visualización, que recogerá mediante un display la dirección del receptor, y mediante dos leds la opción de cifrado y la de apertura del canal. - Para transmitir la secuencia de bits con esta información, un transmisor digital procede a recoger los mismos en pararelo para enviarlos en formato serie a través de un cable al receptor. - La señal de audio la introduciremos en el sistema analógico, que comienza en un adaptador de señal. Éste se encarga de adaptar niveles de impedancia y tensión de la señal de audio a unos admisibles para el resto del circuito. - Un cifrador de audio tomará la señal original y la invertirá en frecuencia, para que pueda ser ininteligible para un miembro no autorizado que quiera escuchar. Además deberán filtrarse las señales de manera adecuada. Memoria final Página 3 de 60 LCEL Sistema de difusión selectiva con cifrado - Para salir al canal, la señal de nuevo deberá adaptar sus niveles de tensión mediante el adaptador a la línea de salida. Arquitectura del sistema receptor: La arquitectura del receptor se basa en los módulos que aparecen en la figura: Describiéndolo de manera concisa: - A través de la línea de datos, la secuencia de bits llega al receptor digital, que se encarga de transformar los bits en serie a la entrada en salidas en paralelo. - Mediante el selector de dispositivo escogemos el código del receptor, que se comparará con el de llegada en el controlador de selección. - La señal de audio llegará por otro canal. En primer lugar debería pasar por un nuevo adaptador de señal, pero podrá eliminarse finalmente porque se transmite con valores adecuados desde el emisor. - El descifrador de audio llevará a cabo la demodulación de la señal. También deberemos colocar filtros que adecúen la señal. - Un nuevo módulo, esta vez el selector de cifrado de la señal, deberá decidir si la señal que se debe escucharse es la señal cifrada o la original. - Por último necesitaremos una etapa de potencia para adaptar los niveles a la entrada de unos auriculares, que será lo que utilizaremos para oír la señal. Parte del conjunto, a su vez, estará sincronizado por dos relojes, uno para la parte digital y otro para la modulación analógica. Memoria final Página 4 de 60 Sistema de difusión selectiva con cifrado LCEL Opcionalmente se nos propusieron algunas mejoras que al ser implementadas producirán una serie de modificaciones y de módulos añadidos, que se explicarán con más detenimiento en el correspondiente apartado. Esta memoria recoge toda la labor de diseño y montaje del sistema propuesto, así como las simplificaciones, problemas y resultados obtenidos una vez construido el mismo . Memoria final Página 5 de 60 LCEL Sistema de difusión selectiva con cifrado EXPERIMENTOS PREVIOS: CARACTERIZACIÓN CARACTERIZACIÓN DIGITAL: FAMILIA LÓGICA 74HCXXXX. Para realizar la caracterización de la familia lógica 74HCXXXX escogeremos el integrado 74HC04, que consta de 6 puertas inversoras y entre las que elegiremos una para nuestro estudio. Una vez alimentada la pastilla con +5V y GND, introduciremos una señal triangular a la entrada de una las puertas. Con el canal X del osciloscopio mediremos ésta, y con el canal Y la salida del inversor. Utilizando el modo XY del osciloscopio obtendremos una curva de transferencia como la que aparece en la hoja de resultados que se adjunta al final de este apartado. Podemos observar que el flanco de bajada no es ideal, sino que hay una zona donde los valores no están bien definidos. Los niveles de tensión teóricos que aparecen en la hoja de características son muy parecidos a los medidos en el laboratorio, como veremos en la siguiente tabla: Valor teórico Valor (Vcc=4.5V) experimental Nivel alto mínimo de tensión a la entrada VIH 3.15 V 3V Nivel bajo máximo de tensión a la entrada VIL 1.35 V 1.8 V Nivel alto mínimo de tensión a la salida VOH 4.4 V 5V Nivel bajo máximo de tensión a la salida VOL 0.1 V 0V Para medir el tiempo de retardo utilizaremos, tal y como se nos indica, una onda cuadrada con los niveles adecuados de amplitud. No nos fue posible finalmente medirlo de manera experimental en el laboratorio por no poder encontrar una resolución adecuada del osciloscopio; igualmente nos ocurrió con el tiempo de subida. Así pues, nos guiaremos por los valores teóricos de la hoja de características: Tiempo de retardo = 11 nsg Memoria final Tiempo de subida = 8 nsg Página 6 de 60 LCEL Sistema de difusión selectiva con cifrado CARACTERIZACIÓN ANALÓGICA: AMPLIFICADOR OPERACIONAL LM324. 1 Medida del slew rate El slew rate es un factor limitante de la frecuencia máxima utilizable sin que se produzca distorsión. Se define como la máxima variación de señal de salida por unidad de tiempo. La medida de éste lo haremos implementando un seguidor de tensión basado en un operacional LM324 tal y como indica la figura. Introduciendo una señal cuadrada a la entrada, y variando MEDIDA DEL SLEW RATE amplitud y frecuencia, podremos observar los efectos del slew rate. En la hoja de características del amplificador operacional elegido aparece con una amplitud de entrada de 2,5 Vpp como slew rate 0,5V/µ µsg, muy parecido a los valores conseguidos experimentalmente a distintas frecuencias, tal y como aparece en la tabla de la hoja de resultados. 2 Efecto de la realimentación sobre la ganancia y el ancho de banda De nuevo trabajaremos con el amplificador operacional LM324. Nos dan un esquema del amplificador no inversor con los valores de resistencias R1=22kΩ, Memoria final Página 7 de 60 LCEL Sistema de difusión selectiva con cifrado R2=220kΩ, R4=100kΩ y C1=10nF, y se nos pide que calculemos los valores de R3 y C2. En las entradas del amplificador operacional, al ser un elemento no ideal, existen unas pequeñas corrientes contínuas que entran o salen de él, y que no son deseables. Son las corrientes de polarización Ibias,. La resistencia R3 tiene como fin compensarlas. Para calcular R3 debemos observar el circuito en contínua. Los condensadores quedan como circuitos abiertos, con lo que: V+ = R4 ∗ I bias Observamos que en la hoja de características de nuestro amplificador aparece una corriente Ibias de valor típico 45 nA, por lo que V+ = 4,5 mV. Para que se cumpla Vo = G*(V+ - V-) = 0 → V+ = V-, por lo tanto, como: V − = I bias * ( R3 + ( R1 R2 )) Tendremos que: R3 = 80 kΩ. El condensador C2 tiene como función conseguir que la resistencia R3 quede lo más parecida posible a un cortocircuito, para ello se pone en paralelo a ésta, para lograr una impedancia conjunta que sea pequeña. Cuanto mayor sea este condensador, menor será la impedancia. Hemos estimado que con un condensador de C2=100nF, tal y como recomiendan en el libro “Aspectos prácticos de diseño y medida en laboratorios de electrónica”1 será suficiente. Posteriormente se nos pide que calculemos las frecuencias de corte inferior y superior esperadas del circuito, dibujemos el diagrama de Bode y comparemos con las medidas realizadas experimentalmente. 1 J.Ferreiros, J.Macías Guarasa y otros. Aspectos prácticos de diseño y medida en el laboratorio de electrónica. Servicio de Publicaciones ETSIT: 2001. Pág 9. Memoria final Página 8 de 60 LCEL Sistema de difusión selectiva con cifrado a) frecuencia de corte superior Para calcular la frecuencia de corte superior necesitamos conocer el valor del polo de compensación, que una vez realimentado el circuito se verá multiplicado por el factor (1+ Avf*β), obteniendo de esta manera la frecuencia de corte superior. Según la hoja de características del LM324, la ganancia a frecuencias medias es Avm=100dB y el producto ancho de banda por ganancia unidad es BW*Av = 1MHz. Con ello obtenemos un polo de compensación: polo de compensación = 1MHz = 10 Hz Avm Para frecuencias medias nuestro circuito tiene el siguiente aspecto: Su realimentación es tensión-serie (siendo tensión la señal de muestreo y serie la asociación a la entrada). Con ello calculamos los siguientes parámetros: β= R11 = R 22 = Memoria final R1 = 0.09 R1 + R2 v1 i1 v2 = 0 v2 i2 i1 = 0 = R1 * R 2 = 20 k Ω R1 + R 2 = R1 + R 2 = 242 k Ω Página 9 de 60 LCEL Sistema de difusión selectiva con cifrado Siendo el circuito resultante: Rin es de valor muy alto, por lo que lo aproximaremos a un circuito abierto. Ro según la hoja de características del A0 tiene un valor cercano a 100Ω. Resolviendo el circuito que resulta, obtendremos: Az = v0 R22 = Av * R4 * ii R0 + R22 Avf = AvAO * R22 ≈ 10 5 R0 + R22 Luego resultará una frecuencia de corte superior: f cs = f p (1 + Avf * β ) = 90kHz b) frecuencia de corte inferior Para calcular la frecuencia de corte inferior debemos hallar el circuito equivalente para frecuencias bajas, que tiene la siguiente forma: Memoria final Página 10 de 60 LCEL Sistema de difusión selectiva con cifrado Mediante el método de las constantes de tiempo en cortocircuito, obtenemos: Rc1= R4 τ = C1*Rc1 =10-3 f ci = 1 1 1000 * = = 159 Hz 2 *π τ 2 *π Por todo el desarrollo anterior hemos calculado de manera teórica los valores: fcs = 90 KHz fci = 159 Hz El diagrama de Bode que recoge estos valores es el que aparece en la hoja de resultados. Memoria final Página 11 de 60 LCEL Sistema de difusión selectiva con cifrado MEJORAS Las mejoras voluntarias acometidas para esta práctica han sido: - Uso de un teclado sobre el que se implementa toda la unidad de entrada - Automatización del proceso de apertura y cierre del canal - Implementación de una dirección de difusión - Detección de palabras en línea y paridad o Generación y detección de paridad o Autómata de control de recepción de palabras - Montaje mediante técnica wire-wrapping 5.1 Uso de teclado Frente al gran número de interruptores y el pulsador propuestos en la práctica básica, nosotros hemos decidido utilizar un único teclado, que integra todas las funcionalidades de estos elementos ofreciendo, desde nuestro punto de vista una mejor operatividad y un acabado más parecido al que cabría encontrarse en un sistema comercial. Así, las teclas numéricas del teclado utilizado sirven para seleccionar de manera inmediata el receptor sobre el que se desea actuar, sin necesidad de tener que manejar microinterruptores. La tecla correspondiente al asterisco (*) actúa igualmente a modo de microinterruptor, encendiendo y apagando la opción de cifrado. La tecla almohadilla (#) actúa como pulsador y, al haber implementado la mejora de automatización en el proceso de apertura y cierre del canal, sirve también para conmutar entre canal abierto y canal cerrado, por lo que viene a sustituir al microinterruptor encargado de este cometido en la práctica básica. Los detalles técnicos referentes a la implementación de todos estos aspectos se describen en el apartado 1.1.1 de la sección “Diseño práctico”, referente a la unidad de entrada). Memoria final Página 12 de 60 Sistema de difusión selectiva con cifrado LCEL 5.1 Automatización del proceso de apertura y cierre del canal La realización de esta mejora hace que, en nuestro sistema, en lugar de seleccionar la apertura o cierre de canal mediante un microinterruptor, el usuario conmute automáticamente entre canal abierto y canal cerrado cada vez que actúa sobre el pulsador de transmisión (#). Para ello, hemos utilizado un biestable tipo T, tal y como se proponía en el enunciado de la práctica. En realidad, nosotros hemos considerado que la unidad de entrada sirve para seleccionar las opciones de transmisión deseadas y que el pulsador de transmisión sirve para confirmarlas y enviar la orden al receptor. Por esa razón, cuando el bit de canal del receptor esté a nivel alto, no quiere decirse que el bit de canal del receptor también lo esté, es decir, no quiere decirse que el canal esté de hecho abierto, sino que al enviar la orden pulsando la tecla de transmisión, el canal del receptor seleccionado se abrirá. Este hecho, unido a la automatización del proceso de apertura y cierre del canal, hará que los leds de canal del emisor y el receptor nunca deban estar encendidos o apagados simultáneamente (dejando a un lado estados iniciales inmediatamente posteriores al encendido, así como posibles fallos esporádicos en el circuito de captura y retención del teclado), ya que en realidad el led de canal del receptor nos va a indicar la situación del canal en ese instante (estado actual) y el del emisor nos va a indicar la nueva orden que nosotros deseamos enviar (como queremos que sea el siguiente estado), orden que “no entrará en vigor” hasta que se accione el pulsador de transmisión. 5.3 Implementación de una dirección de difusión Esta mejora consiste simplemente en utilizar un comparador más para hacer que cuando se seleccione el número 7 en el emisor actúemos simultáneamente sobre todos los receptores. Los detalles técnicos de su implementación se discuten en la sección en el apartado 1.2 de la sección “diseño práctico”. Memoria final Página 13 de 60 LCEL Sistema de difusión selectiva con cifrado 5.3 Detección de palabras en línea y paridad El planteamiento básico de esta doble mejora se describe a la perfección en el enunciado de la práctica, por lo que no lo repetiremos aquí. Generación y comprobación de paridad La primera parte de la mejora, corresponde a la introducción de un bit de paridad para añadir protección frente a errores. La idea fundamental es conseguir que el número de unos presentes entre los bits de código, cifrado y en el propio bit de paridad sea siempre impar. Para ello, utilizaremos dos generadores de paridad 74HC280, uno en el emisor y otro en el receptor, conectándolos al resto del subsistema digital tal y como se describe a en los apartados referentes al subsistema digital de la sección “Diseño práctico”. Autómata de detección de palabras Sin lugar a dudas, el diseño e implementación del autómata de detección de palabras constituye, tras el uso de la técnica wire-wrapping, la mejora de mayor complejidad de entre todas las acometidas. La idea general pasa por construir una máquina de estados que examine los datos que llegan por la línea de transmisión procedentes del emisor y que “dé su visto bueno” cuando la palabra recibida cumpla con las especificaciones deseadas. En nuestro caso, esto se traduce a que el autómata se encuentre en reposo mientras la línea de transmisión se encuentre en estado alto. En el momento en que se detecta un cero, que puede corresponder al bit de arranque, el autómata debe esperar un intervalo de 7 bits y observar el valor del bit situado siete posiciones por detrás de ese hipotético bit de arranque. Si dicho bit está a nivel alto, es decir, coincide con el valor esperado para el bit de parada o bit de stop, el autómata pondrá un nivel alto en su salida de validación (“validación autómata”) que se introducirá a través de una puerta AND junto a la señal “validación comparadores” y dará lugar a la línea de “validación general”, cuya función se describe detalladamente en el apartado correspondiente del diseño práctico. Memoria final Página 14 de 60 LCEL Sistema de difusión selectiva con cifrado Si consideramos dos posibles estados para el autómata: (R)eposo y (C)ontando (que a su vez se podría dividir en otros siete), y utilizamos la notación [bit recibido]/[próximo estado], el diagrama de estados para nuestro autómata es de la forma: 1/R 1/R R 0/C x/C 1 x/C 2 3 x/C Posible bit de parada 1 Q(t) Q(t+1)=D Contador 0 0 0 0 1 1 1 1 2 1 1 3 1 1 4 1 1 5 1 1 6 1 1 7 1 0 x/C 6 x/C 7 0/R R Y la tabla de estados viene dada por: E 1 0 X X X X X X 4 x/C 5 1 0 8 0 0 Clear Z 0 0 0 0 0 0 0 0 1 0 0 Este es el cronograma utilizado durante la fase de diseño: Memoria final Página 15 de 60 Sistema de difusión selectiva con cifrado LCEL El esquema lógico asociado es de la forma: Y, finalmente, la realización circuital del mismo es la siguiente: Memoria final Página 16 de 60 LCEL Sistema de difusión selectiva con cifrado 5.4 Montaje mediante técnica wire-wrapping Esta mejora ha sido, sin duda, la que ha supuesto un mayor número de horas de trabajo, aunque también ha sido la más enriquecedora al habernos permitido conocer una técnica, nueva para nosotros, que parece ofrecer opciones muy interesantes en todo lo referente al diseño y montaje de circuitos electrónicos. En el el apartado 5 del texto “Aspectos prácticos de diseño y medida en laboratorios de electrónica” se describen brevemente algunos aspectos interesantes en relación a la técnica de wire-wrapping, por lo que no los repetiremos aquí. En primer lugar, podemos hacer una relación del material empleado con motivo exclusivo de la utilización de esta técnica: - Placas para montaje en wire-wrapping. Las placas utilizadas son del tipo “Eurocard square pad prototyping card” y han sido adecuadas a las características de nuestro sistema concreto, tanto en lo referente al tamaño como a la disposición de los distintos conectores y visualizadores. - Zócalos para wire-wrapping (wire-wrap turned pin sockets D.I.L.). - Pistola wire-wrap. Herramienta necesaria para este tipo de montajes. El modelo utilizado (muy amablemente prestado por su propietario), es uno de los más básicos y funciona a 12V, conectándose a la red mediante un transformador. La pistola consta en su “boca” de un cilindro con dos orificios. Por uno de ellos se introduce el cable pelado y por el otro se introduce la patilla del zócalo al que se desea enrollar. Memoria final Página 17 de 60 LCEL Sistema de difusión selectiva con cifrado - Cable de diámetro fino, especial para wire-wrapping y pelacables graduado para asegurar una longitud apropiada y fija de la zona de cable pelada. - Soldador y trencilla desoldadota para soldar todos los zócalos a la placa y algunos de los componentes a los propios zócalos. Aunque finalmente, el prototipo presentado a examen será el montado con wirewrapping, el método de montaje utilizado durante toda la fase de diseño fue el de la tradicional placa de inserción. Estas fotos, tomadas con una cámara digital, corresponden a el montaje en placa de inserción durante la primera fase del diseño. Fue en una placa de este tipo donde fuimos probando todas las fases de nuestro diseño, tanto para el subsistema analógico, como para el digital, y donde fuimos Memoria final Página 18 de 60 LCEL Sistema de difusión selectiva con cifrado haciendo las correcciones pertinentes aprovechando las facilidades que estas placas ofrecen a tal efecto. Una vez que los resultados obtenidos fueron satisfactorios, y que todo parecía funcionar tal y como deseábamos, completamos nuestros esquemas circuitales en papel y los repasamos varias veces para estar seguros de que coincidían con el montaje realizado, y fuimos desmontando todos los componentes para pasar a utilizarlos en el montaje wire-wrapping. A continuación, describimos detalladamente el proceso de montaje: - Para empezar, nos encontramos con las placas de wrapping “desnudas”, sin un solo componente. - Lo primero que hicimos fue decidir la ubicación de los distintos bloques, estando para ello en posesión de todo el esquema circuital sobre papel. - Acto seguido, pasamos a colocar los distintos zócalos en los puntos apropiados, fijándolos a la parte superior de la placa con cinta aislante, dando la vuelta a la misma y soldándolos adecuadamente a la cara inferior, que es la que cuenta con los contactos metálicos apropiados. - A continuación, pasamos a hacer todos los taladros necesarios para acoplar los conectores banana hembras, los leds y los jacks de audio. - El siguiente paso consistió en etiquetar convenientemente toda la cara inferior de la placa, para agilizar el proceso de cableado, ya que de otro modo hubiéramos tenido que estar dándole la vuelta continuamente y eso habría sido muy negativo en términos de eficiencia. - Tras etiquetar todas las patillas convenientemente, pasamos a cablear todo el circuito, utilizando la herramienta en forma de pistola comentada con anterioridad. Memoria final Página 19 de 60 LCEL Sistema de difusión selectiva con cifrado - Una vez que todos los cables estuvieron conectados, tuvimos que comprobar con un polímetro todas las conexiones una a una, para asegurarnos de que todo estaba bien y para detectar algunos errores que habíamos cometido durante la etapa del cableado. - A continuación, colocamos todos los componentes, soldando resistencias, condensadores y leds y “pinchando” o encajando los distintos integrados sobre sus correspondientes zócalos. - Finalmente, incluimos todos los condensadores de filtrado de alimentación, soldándolos directamente entre las patillas correspondientes en la cara inferior de la placa, con el fin de optimizar el filtrado a través de una mayor proximidad a los puntos de alimentación. Tras hacer todo esto fuera de horas de laboratorio, tuvimos que volver a éste para comprobar el correcto funcionamiento de la nueva placa y depurar errores que sólo podían ser detectados mediante el uso del osciloscopio. En general, los errores de montaje que hemos detectado no han sido demasiados, aunque, como cabía esperar, tuvimos que corregir algunos cables que había ido a parar a patas equivocadas. Entre las ventajas obtenidas al utilizar este montaje, cabe destacar la reducción en el tamaño final del mismo (que en el otro caso venía a ocupar cuatro placas amarillas de tamaño estándar) y, sobre todo, la mayor robustez de éste si se le compara con su equivalente en inserción. Memoria final Página 20 de 60 Sistema de difusión selectiva con cifrado LCEL Aspecto final de emisor Aspecto final del receptor DISEÑO PRÁCTICO SUBSISTEMA DIGITAL Memoria final Página 21 de 60 LCEL Sistema de difusión selectiva con cifrado 1.0. GENERADOR DE RELOJES A la hora de diseñar nuestro circuito, hemos decidido utilizar dos señales de reloj independientes, una para el subsistema analógico y otra utilizada exclusivamente para las modulaciones analógicas. En ambos casos, hemos generado una señal unipolar de pulsos cuadrados con duty cycle del 50%, para lo cual hemos recurrido a dos temporizadores 555 en configuración aestable y a sendos divisores de frecuencia implementados a través de biestables J-K (74HC76) con las entradas J y K conectadas directamente a nivel alto (biestables tipo T). El esquema utilizado es de la forma: +5V R1 R2 8 7 6 5 NE555N 1 2 3 C1 C2 Reloj 2·f J 4 Reloj f Q CLK K La frecuencia escogida para el reloj encargado de controlar el subsistema digital ha sido de 10 khz. Para el cálculo de los valores de las resistencias y condensadores a utilizar, utilizamos las relaciones proporcionadas por el fabricante en la dataste del producto. La frecuencia viene dada por f = Memoria final 1 1.44 = T ( R1 + 2 R2 )C1 Página 22 de 60 LCEL Sistema de difusión selectiva con cifrado Y el valor del duty cycle D = R2 R1 + R2 A partir de estas relaciones, obtuvimos que un posible conjunto de valores es de la forma: f = 20 khz C1 10 nF C2 10 nF R1 2.4 kΩ R2 2.4 kΩ Tras el divisor de frecuencia la frecuencia de la señal será de 10 khz y su duty cycle será del 50%. En realidad, la tolerancia en los valores de las resistencias hace que la frecuencia no sea exactamente de 10 khz, sino algo inferior (en torno a 9.7-9.8 khz), pero dado que este parámetro no es crítico para el subsistema digital, no parece necesario ajustar con potenciómetros para obtener un valor más preciso. En el segundo reloj sí que nos interesa, en cambio, obtener un valor exacto de 6.4 khz a la salida del divisor de frecuencia, por lo que utilizaremos un potenciómetro para ajustar la frecuencia de señal proporcionada por el 555 hasta obtener f=12.8 khz. Utilizando las mismas ecuaciones que para el caso anterior, el conjunto de valores obtenidos ahora viene dado por la tabla: f = 12.8 khz 1.1. C1 10 nF C2 10 nF R1 6.2 kΩ R2 4.7 kΩ (potenciómetro) MÓDULO EMISOR Memoria final Página 23 de 60 LCEL Sistema de difusión selectiva con cifrado 1.1.1. Unidad de entrada La unidad de entrada constituye el primer bloque a tratar dentro del subsistema digital y va a permitir al usuario seleccionar las distintas opciones de transmisión. En la práctica básica, esta unidad debería estar constituida por un conjunto de microinterruptores con el que programar el código del periférico sobre el que actuar, dos microinterruptores independientes de los anteriores con los que seleccionar cifrado y apertura de canal, y un pulsador sobre el que actuar para enviar la orden de transmisión. En nuestro caso, todos estos elementos se han implementado a través de un teclado alfanumérico en el que se distinguen tres funcionalidades bien diferenciadas: - Bloque numérico, que permite seleccionar de un modo inmediato el receptor sobre el que se desea actuar. Los números válidos van del cero al siete, ambos inclusive y estando este último reservado para la dirección de difusión o broadcast. - Tecla de cifrado (∗). Permite seleccionar la el tipo de señal que se desea transmitir: señal cifrada o señal sin cifrar. - Tecla de transmisión (#). Esta tecla actúa como pulsador de transmisión y, a la vez, sirve para abrir y cerrar el canal gracias a la mejora de automatización en el proceso de apertura y cierre del mismo. A la hora de abordar la implementación de esta unidad de entrada, lo primero que tuvimos que hacer fue incluir resistencias de pull-up en todas las líneas del teclado que queríamos utilizar. La captura y retención del número seleccionado se ha hecho en diversos pasos. En primer lugar, las salidas del teclado correspondientes a los números en cuestión (del 0 al 7) se conectan a un codificador 74HC148, a la salida del cual obtendremos el valor binario de cada número cada vez que este se pulse, junto a una señal GotSomething. Tanto las tres líneas correspondientes al número en binario, como la de la señal GS se hacen pasar por un inversor con histéresis (74HC14) con la doble intención de que Memoria final Página 24 de 60 LCEL Sistema de difusión selectiva con cifrado pasen a ser activas a nivel alto y de que la propia característica de histéresis nos sirva para evitar transiciones espúreas de señal. A la salida del inversor, las líneas procedentes del codificador entran en lo que podríamos denominar “circuito de retención”. Este está compuesto por un multiplexor (74HC157) y seis flip-flops D (74HC174). En realidad, la idea es utilizar un multiplexor independiente para cada línea binaria y combinarlo con dos biestables tipo D en serie para muestrear el valor de la señal y realimentarla al multiplexor, tal y como se describe en la siguiente figura tomada del manual del laboratorio: La señal GS del codificador, tras pasar por el inversor con histéresis, será la que actúe como señal de selección común para los tres multiplexores. De este modo, cada vez que pulsemos un número del teclado, obtendremos el valor binario del mismo en las salidas Q1, Q3 y Q5 del 74HC174, que serán las que ataquen las entradas del codificador BCD7 segmentos, del registro de paridad y del registro de transmisión paralelo/serie. En lo que respecta a las teclas de cifrado y de canal, lo primero que cabe destacar es la necesidad de incluir un filtro antirrobotes para evitar transiciones espúreas de la señal. Éste está constituido por un filtro paso-bajo, seguido de un inversor con ciclo de histéresis. A la salida del inversor, ambas entradas atacan sendos flip-flops J-K (74HC86), que actúan como biestables tipo T por tener sus dos entradas J y K conectadas a nivel alto. De este modo, cada vez que pulsemos la tecla de cifrado o de transmisión/canal, el valor en las salidas de estos biestables cambiará de 0 a +5, o de +5 a 0, obteniéndose un comportamiento análogo al que cabría esperar de un microinterruptor. Memoria final Página 25 de 60 LCEL Sistema de difusión selectiva con cifrado Finalmente, llevando la señal procedente de la tecla de transmisión desde la salida del inversor hasta el registro paralelo/serie, y sin hacer que esta pase por ningún tipo de biestable, conseguimos que, al pulsar dicha tecla, se verifique el doble objetivo de abir/cerrar canal automáticamente y mandar la señal apropiada para que se active la transmisión de los datos seleccionados hacia el receptor. El esquema completo de la unidad de entrada es de la forma: 1.1.2. Módulo de Visualización El módulo de visualización nos permite conocer en cada momento cuál es el estado de las distintas opciones de transmisión seleccionadas en el módulo emisor. El bloque está compuesto por un display de 7 segmentos en el que se refleja el código del receptor sobre el que se desea actuar. La opción de cifrado o no viene determinada por el punto situado en la esquina inferior izquierda del display, mientras que la opción de apertura o cierre de canal se representa mediante el led de color verde situado junto al display. Para hacer que el visualizador funcione correctamente, hemos utilizado un decodificador apropiado (74HC4511), hasta el que llegan las líneas del número codificado en binario. Entre el decodificador y el display, se ha colocado una matriz Memoria final Página 26 de 60 Sistema de difusión selectiva con cifrado LCEL de resistencias de 220 ohmios, para asegurarnos de que las entradas de éste último se atacan con un voltaje adecuado. En lo que respecta a las líneas del canal y cifrado, hemos considerado apropiado incluir sendos transistores (BC109) para evitar insuficiencias en el suministro de corriente ante el hecho de tener que atacar simultáneamente a los leds, al registro paralelo/serie y, en el caso del cifrado, al comprobador de paridad. 1.1.3. Generador de Paridad Como parte de la mejora de generación y detección de paridad, en el emisor debemos incluir un generador de paridad que nos proporcione la señal adecuada para atacar al registro paralelo/serie.En nuestro caso, hemos utilizado el circuito 74HC280, en cuyas entradas se colocan los bits del código binario del receptor seleccionado y el bit de cifrado. Nuestro objetivo es que cuando consideremos los tres bits de código, el de cifrado y el de paridad, el número de bits con valor 1 (+5 V) sea siempre impar. Para ello, tomaremos la salida “even” (par) del 74HC280, que valdrá 1 cuando el número de unos de los otros bits sea par y cero cuando sea impar. Está salida irá directamente al registro de transmisión para ser comparada con la señal de paridad generada en el receptor. Memoria final Página 27 de 60 LCEL Sistema de difusión selectiva con cifrado 1.1.4. Transmisor digital El transmisor digital se ha implementado con un registro carga paralelo / salida serie (74HC165), al que se llevan todas las líneas de código del receptor, canal, cifrado y paridad. Siguiendo las especificaciones del enunciado, el primer bit del registro ha puesto a nivel alto para asegurar un nivel alto de la línea cuando el transmisor esté en reposo. A continuación de este se incluye un bit de arranque a nivel bajo y, acto seguido, se transmite el resto de bits siguiendo el modelo: ...1 0 B2 B1 B0 CH CF Par 1... Siguiendo este código de colores, el esquema del conexionado del registro paralelo/serie es de la forma: La línea discontinua es la línea de transmisión de datos que irá directamente al registro serie / paralelo del receptor. 1.1.5. Circuito de reset Para asegurarnos de que el estado inicial del subsistema emisor es conocido y siempre el mismo, parece interesante incluir un circuito de reset que se encargue de Memoria final Página 28 de 60 LCEL Sistema de difusión selectiva con cifrado inicializar los valores de los biestables cada vez que desconectemos y volvamos a conectar la alimentación. En nuestro caso, hemos optado por un circuito de reset típico consistente en un montaje RC entre tierra y Vcc, en el que la entrada de reset de los distintos chips que conectemos a él se sitúe durante unos instantes a nivel bajo para luego estabilizarse y quedarse a nivel alto. Esto se consigue con el circuito propuesto porque cada vez que concectamos la alimentación, la red RC actúa produciendo una subida de tensión exponencial en su punto medio, con una constante de tiempo τ = RC que vendrá dada por la expresión: − t Vo = Vcc (1 − e τ ) Como queremos que todos aquellos puntos a los que esté conectado el reset se pongan a nivel bajo durante un cierto tiempo, utilizaremos el valor VIL obtenido durante la caracterización para saber qué voltaje se considera bajo por la familia lógica utilizada, en nuestro caso: VIL=1.8 V. Conociendo esto, podemos tratar de despejar el valor de tau en la expresión anterior para un tiempo total en nivel bajo algo inferior a 1 segundo, que será más que suficiente para inicializar los biestables y no tendrá demasiada relevancia a escala humana. Si así lo hacemos, y después de utilizar valores normalizados para la resistencia y el consendador, el circuito de reset final es de la forma: τ = R·C = 2.02 tnivel bajo = 0.9019 sg 4.3KΩ R = 4.3 kΩ C = 470 uF 470µF En todos los esquemas de esta memoria, la presencia de un círculo azul se ha utilizado para referirse a las entradas de los circuitos hasta los que llega el reset. Las funciones más importantes de este reset son poner a cero las salidas de los biestables D (74HC174) y J-K (74HC76), así como inicializar a cero el valor del display Memoria final Página 29 de 60 LCEL Sistema de difusión selectiva con cifrado tras encender brevemente todos sus segmentos (para ello, atacamos la entrada LT del 74HC4511). En realidad, el circuito de reset sólo se ha implementado en el emisor a fin de ahorrar espacio y complejidad de cableado en el circuito receptor, y por considerar que lo que verdaderamente nos importa es que sea el bloque emisor el que se inicialice con unos parámetros preestablecidos. En cualquier caso, si este prototipo estuviera destinado a un ámbito profesional, sería necesario incluir también un circuito de reset en el receptor. 1.2. MÓDULO RECEPTOR 1.1.1. Receptor digital De manera complementaria a lo comentado para el transmisor digital, el núcleo de este bloque consta de un registro de entrada serie / salida paralelo (74HC164), hasta cuya entrada llega la línea de transmisión de datos procedente del emisor. Las líneas de salida atacarán a la lógica de comparación, al generador de paridad y, en el caso de las posiciones correspondientes a los bits de cifrado y canal, a un circuito de retención basado en biestables que describiremos con posterioridad. 1.1.2. Selector de dispositivo Este bloque está compuesto por tres micro-interruptores, que nos van a permitir seleccionar el código del dispositivo receptor. La posición baja de cada microinterruptor corresponderá a un uno binario, mientras que la posición alta será la correspondiente al cero binario. El bit más significativo del número programado es el situado más a la izquierda de los tres. [a modo de ejemplo, en esta figura se ha seleccionado el receptor de código 011 = 3] Memoria final Página 30 de 60 Sistema de difusión selectiva con cifrado LCEL El montaje en cuestión no es demasiado complicado, debiendo incluirse resistencias de pull-up como ya ocurría con el teclado en el emisor. 1.1.3. Detector de paridad El bloque utilizado para generar la paridad es completamente análogo al descrito para el emisor, por lo que las mismas consideraciones son aquí aplicables. Las líneas de entrada procederán del registro serie/paralelo y la salida EVEN (PAR) del 74HC280 se llevará a uno de los comparadores para intervenir directamente en la lógica de comparación. 1.1.4. Controlador de selección Como ya hemos comentado, el registro serie/paralelo está recibiendo en todo momento los datos procedentes del emisor, que se colocan en sus distintas salidas siguiendo algo similar a una rotación cíclica. Memoria final Página 31 de 60 LCEL Sistema de difusión selectiva con cifrado Pues bien, la idea para la detección de palabras está en observar el valor de dichas salidas en cada instante, en ir tomando “fotografías instantáneas” del valor de las mismas, y en comparar dichas “fotografías” con una serie valores (todos ellos prefijados, a excepción del de paridad, que se determina “en tiempo de ejecución” ) para detectar la posible transmisión de una orden procedente del emisor. Para la comparación, vamos a utilizar tres comparadores de 8 bits (74HC85). En el primero de ellos, que podríamos denominar “general” o “común”, comparamos el bit de arranque (siempre a cero), el bit de paridad y el bit de parada o stop (siempre a uno lógico). Cuando este comparador estime que el patrón observado a la salida del registro paralelo/serie puede corresponder al de una palabra válida, pondrá a uno su salida (O=), lo que a su vez habilitará a los otros dos comparadores para estudiar el la idoneidad del código númerico y su correspondencia con el del receptor. El hecho de tener que utilizar tres comparadores se debe a haber implementado la mejora de dirección de difusión o broadcast. Así, además del comparador “general” o “común”, tendremos un comparador que tratará de comparar el código procedente del emisor con el código programado en el receptor a través de los microinterruptores y otro que se encargará de comparar el código enviado por el emisor con el codigo 111 = 7 correspondiente a la dirección de difusión. Las salidas (0=) de estos dos últimos comparadores se harán pasar por una puerta OR (= NOR[74HC02] + INV [74HC04]) de manera que cuando cualquiera de las dos se ponga a nivel alto, la señal de validación también se ponga a dicho nivel. Así pues, a la salida del inversor, tenemos una línea de “validación comparadores” que se pondrá a nivel alto cuando recibamos una palabra con el formato correcto y en la que el código programado coincida con el del receptor o con el de difusión. Como hemos decidido implementar el autómata de detección de palabras (cuya descripción se realiza de manera más detallada en el apartado de “Mejoras”), a la salida del mismo tendremos también una línea de confirmación, que podemos denominar “validación autómata”, y que sólo se pondrá a nivel alto cuando el formato de la palabra concuerde con las especificaciones del formato de transmisión. La señal de “validación general”, deberá ponerse a nivel alto cuando y sólo cuando las señales de “validación comparadores” y “validación autómata” estén a nivel alto, Memoria final Página 32 de 60 LCEL Sistema de difusión selectiva con cifrado por lo que haremos pasar ambas por una puerta AND [=NAND(74HC00) + INV(74HC04) ]. A la salida de este último inversor tendremos la señal de validación deseada, que sólo se pondrá a nivel alto cuando se reciba una palabra correcta en todos los sentidos, incluyendo formato, código coincidente con el del receptor o broadcast y no solapamiento temporal con ninguna otra palabra. Una vez hecho esto, debemos asegurarnos de retener el valor de los bits de canal y cifrado cada vez que haya una detección válida de de palabra. Para ello, llevaremos las líneas del registro serie/paralelo correspondientes a dichas posiciones hasta sendos biestables tipo D (por comodidad, hemos utilizado un 74HC174) y capturaremos su valor utilizando como señal de reloj la señal de “validación general” que acabamos de describir en el párrafo anterior. Los valores de salida de estos biestables Q0 y Q1 se llevarán hasta los multiplexores analógicos para hacer efectiva la selección deseada y hasta sus respectivos leds de color rojo (cifrado) y verde (canal), utilizando dos transistores BC109 en estos dos últimos casos para asegurar un suministro apropiado de corriente. Memoria final Página 33 de 60 LCEL Sistema de difusión selectiva con cifrado SUBSISTEMA ANALÓGICO 2.1. Adaptador de señal Este módulo aparece a la entrada del bloque emisor y también en el bloque receptor. Su papel es el de adaptar impedancias, niveles de tensión y limitar el ancho de banda. Como simplificación, lo utilizaremos únicamente en el bloque emisor, ya que no es indispensable en el receptor. Adaptador de nivel e impedancia Esta parte del adaptador de señal tiene el esquema de la figura Para el diseño tenemos que cumplir una serie de requisitos: • Vo ≈ 1-2 V • Necesitamos la Zout de walkman, de donde obtendremos la señal de audio de entrada de nuestro sistema. En nuestro caso, según su manual, nuestro walkman tiene Zout = 50Ω • La función de C1 es el acoplo del circuito en alterna, parte además de un filtro paso alto, donde R1 y R2 (R2<<R1) marcan la frecuencia de corte inferior fci, que debe ser de 20Hz. La Zout de nuestro walkman será la Zin del adaptador. Así, pues, tenemos: Z in ≈ 50Ω = Memoria final 1 + R1 R2 ≈ R1 ⇒ R1 = 50Ω jwC1 Página 34 de 60 LCEL Sistema de difusión selectiva con cifrado Esta aproximación la realizamos ya que el paralelo de R1 y R2 tiende a R1 porque R2>>R1 como exigen las especificaciones. Conocido que fci debe ser de 20Hz, C1 es muy sencillo de calcular con el método de las constantes de tiempo en cortocircuito. f ci = 1 2π 1 ∑τ Siendo: τ = C1 * Req = C1 * R1 R2 ≈ C1 * R1 = C1 * 30Ω Luego, tendremos: C1=265 µF Como se verá a continuación, este valor lo modificaremos para simplificar el diseño, eliminando un filtro paso alto posterior y aumentando la frecuencia de corte inferior de éste. Escogeremos una fci de 250 Hz, más restrictiva, con lo que obtendremos un C1 final de 22µF. La función de transferencia o respuesta en amplitud teórica para este filtro, se puede calcular fácilmente con Maple y será de la forma: Memoria final Página 35 de 60 LCEL Sistema de difusión selectiva con cifrado R2 viene implementado por un potenciómetro y se hará lo suficientemente grande para que R2>>R1 y Vo≈1-2Vp. Tomamos un potenciómetro de valor 20KΩ. Filtro limitador de ancho de banda Este filtro tendrá como función principal limitar el ancho de banda de la señal procedente del adaptador de nivel e impedancia. Para lograr el filtrado paso banda necesitaremos, en principio, un filtro paso bajo conectado a uno paso alto. Veremos que el filtro paso alto no es necesario si el filtro paso alto del módulo anterior lo limitamos algo más, exigiendo una mayor frecuencia de corte inferior. Como filtros específicos utilizaremos los filtros de Sallen-Key, en su versión paso bajo y paso alto (aunque como acabamos de comentar, este último no será necesario) a. Desarrollo teórico: filtros paso alto y paso bajo Sallen-Key o Filtro paso bajo de Sallen-Key Un filtro paso bajo Sallen-Key de orden 2 tiene el siguiente aspecto: Este circuito es equivalente a: Memoria final Página 36 de 60 LCEL Sistema de difusión selectiva con cifrado Planteamos las ecuaciones de los nudos X e Y: Y: X: vi − V y R = vo * jwC1 + (V y − v o ) * jwC1 A V y − vo A R2 = jwC 2 * vo A Tendremos entonces: V y = jwC 2 * R2 * vo vo v o + = ( jwC 2 * R 2 + 1) A A A Sustituyendo en la ecuación X: vo v v ( jwC 2 R2 + 1) = 2 * o * jwC1 R1 − o * w 2 C 2 C1 R2 R1 − v 0 * jwC1 R1 A A A v vi = o * jw * (C 2 R2 + 2C1 R1 − C1 R1 A) + 1 − w 2 C 2 C1 R2 R1 A vi − [ ] Por lo tanto: vo A = = 2 vi − w C 2 C1 R2 R1 + jw * (C 2 R2 + 2 * C1 R1 − A * C1 R1 ) + 1 ↓ jw = s = - A s C 2 C1 R2 R1 + s * (C 2 R2 + 2 * C1 R1 − A * C1 R1 ) + 1 2 Debemos identificar Q y wo comparando la anterior ecuación con la que sigue: vo A = 2 vi s s + +1 2 w0 w0 * Q (1) De donde resultan: w0 = ± 1 C 2 C1 R2 R1 y Como simplificación tomaremos: Memoria final 1 1 =± * (C 2 R 2 + 2 * C1 R1 − A * C1 R1 ) Q C 2 C1 R2 R1 C1=C2=C y R1=R2=R. Página 37 de 60 LCEL Sistema de difusión selectiva con cifrado Con esto las fórmulas quedan de la forma: wo = 1/(RC) 1/Q =3-A - Obtendremos ahora la expresión de los polos en función de wo y Q, para una vez obtenidos los valores de éstos, sea sencillo calcular el valor de aquellos. Para conocer la expresión de los polos debemos igualar el denominador de (1) a 0 y despejar los valores de “s”. De esta forma tendremos: s2 + wo s + wo2 = 0 Q 2 w w − o ± o − 4 wo2 Q Q s= 2 A partir de esta expresión deducimos la existencia de dos polos de valores: 1 1 s1 = wo * − + − 1 2 4Q 2Q 1 1 s 2 = wo * − − − 1 2 4Q 2Q - Como valor óptimo de Q debemos elegir uno tal que nos asegure la máxima atenuación fuera de la banda de paso del filtro, es decir, una caída máxima de 40dB por década, que significa la existencia de un polo doble a wo. Con esto: s1 = s2 ⇒ − 1 1 + −1 = 1 ⇒ 2Q 4Q 2 1 1 = Q 2 Sin embargo, experimentalmente se comprueba que para valores mayores de Q= 1/√2 aparece un pico en la curva de respuesta frecuencial. Esto se demuestra teóricamente por la proximidad de los polos del filtro a los ejes imaginarios. Es por ello que tomaremos Q= 1/√2 como valor a tener en cuenta en el diseño Memoria final Página 38 de 60 LCEL Sistema de difusión selectiva con cifrado Aunque las características de los filtros de orden dos son suficientes para el cometido que se les encomienda en esta práctica, en algunos casos decidimos realizar filtros de orden cuatro y en otros de orden seis, con mayor caída a la frecuencia de corte deseada. Para realizar éstos elegimos como método de construcción el basado en el polinomio de Butterworth B(s) 2. De esta manera, la ganancia queda como función: T ( s) = 1 B(s) Para el orden cuatro, el factor B(s) será: B(s) = (s2+0,7654s+1)*(s2+1,8478s+1) Este filtro lo construiremos con dos filtros Sallen-Key de orden dos en cadena , los cuales hemos estudiado previamente a esto. De manera que obtendremos como parámetros: 1/Q1 = 0,7654 → A1 = 3-1/Q1 = 2,2346 1/Q2 = 1,8478 → A2 = 3-1/Q2 = 1,1522 El diagrama de Bode teórico para un filtro Butterworth de orden cuatro y frecuencia de corte superior de 4800 khz es de la forma: 2 N.R, Malik. ”Circuitos electrónicos. Análisis, simulación y diseño”. Prentice Hall. 1996. Pág 886 Memoria final Página 39 de 60 LCEL Sistema de difusión selectiva con cifrado Para el orden seis que queremos lograr, el factor B(s) será: B(s) = (s2+0,5176s+1)*(s2+1,4142+1)*(s2+1,9318+s) Este filtro de orden seis podemos implementarlo con tres filtros Sallen-Key de orden dos en cadena. Luego debemos equiparar : 1/Q1 = 0,5176 → A1= 3-1/Q1 1/Q2 = 1,4142 → A2 = 3-1/Q2 1/Q3 = 1,9318 → A3 = 3-1/Q3 El diagrama de Bode teórico para un filtro de Butterworth de orden seis y frecuencia de corte 4200 es de la forma: o Filtro paso alto de Sallen-Key El filtro paso alto de Sallen-Key es igual que su correspondiente paso bajo, cambiando resistencias por condensadores y viceversa. Memoria final Página 40 de 60 Sistema de difusión selectiva con cifrado LCEL Por tanto, tendrá el siguiente aspecto: Procediendo de nuevo al análisis del circuito de manera similar a la realizada con el filtro paso bajo, obtenemos que: A 2 * s2 vo wo = 2 vi s + (RC * (3 − A) )s + 1 wo2 Repetimos en este caso la suposición de que R1=R2=R y C1=C2=C. Volvemos a lograr como parámetros: w0=1/RC y 1/Q=3-A. b. Diseño práctico Utilizaremos para realizar el filtro limitador de ancho de banda un filtro paso bajo de orden 4, implementado con dos filtros Sallen-Key como indica la figura. Memoria final Página 41 de 60 LCEL Sistema de difusión selectiva con cifrado Para realizar el diseño tomamos valores normalizados: Rn = 1Ω y Cn = 1F. Para realizar el escalado de frecuencias necesitamos conocer el valor del escalado α. Si tomamos como frecuencia de corte superior 4,8KHz: α= 2π*4800 = 30159 Para un escalado razonable de impedancias tomaremos como factor de escalado Ro = 1 kΩ. Resultará entonces: C= Cn = 33ηF α * Ro R = Rn * Ro = 1kΩ Para un diseño Sallen-Key, como dedujimos anteriormente, necesitamos como ganancias: 1/Q1 = 0,7654 → A1 = 3-1/Q1 = 2,2346 (ganancia del primer filtro) 1/Q2 = 1,8478 → A2 = 3-1/Q2 = 1,1522 (ganancia del segundo filtro) Si incorporamos realimentación al circuito, como se mostraba en la figura anterior, tendremos: - A1=2,2346 10 5 − 1 2,2346 = 0,447 β1 = 10 5 RB1 1 − 0,447 1 β1 = ⇒ = = 1,23 R R A1 0,447 1 + B1 R A1 Resultando: RB1= 1,2kΩ RA1= 1kΩ Memoria final Página 42 de 60 Sistema de difusión selectiva con cifrado - LCEL A2 = 1,1522 10 5 − 1 1,1522 = 0,868 β2 = 10 5 RB 2 1 − 0,868 1 β2 = ⇒ = = 0,152 R B1 R A2 0,868 1+ R A1 De este modo obtendremos como resistencias de realimentación del segundo filtro de Sallen-Key: RB2= 150Ω RA2= 1kΩ La respuesta teórica en frecuencia de este filtro puede obtenerse representando con Maple el módulo de la función de transferencia (lo que equivale al diagrama de Bode, pero sin necesidad de emplear escala logarítmica): Las medidas experimentales vienen a confirmar estos cálculos teóricos, tanto en lo referente al valor máximo de amplitud como a la frecuencia de corte superior. Para compensar la amplificación introducida por el filtro, “jugaremos” con el potenciómetro situado en el módulo de adaptación de señal. Memoria final Página 43 de 60 LCEL Sistema de difusión selectiva con cifrado Tras el filtro limitador de ancho de banda conectaremos un seguidor de tensión para aislar impedancias de salida y entrada entre este módulo y el siguiente, operación que realizaremos en varias ocasiones dentro del diseño. Como seguidor utilizaremos el operacional LF356, cuya ventaja principal frente a otros, pese a venir uno en cada integrado, es que se puede regular su offset de manera fácil. Consta de dos patillas entre las que colocaremos un potenciómetro que se regulará para eliminar el offset. La operación es muy simple. Se conectan las entradas del operacional a masa y se mide con el osciloscopio la salida. Si se observa un nivel de contínua, variaremos la resistencia del potenciómetro hasta eliminarlo totalmente. El seguidor de tensión se logra interconectando salida y entrada inversora del operacional, como indica la figura. 2.2. Cifrador y descifrador de audio Desarrollo teórico: Modulación por amplitud de pulso con señales unipolar y bipolar Para obtener una modulación por amplitud de pulso es necesario multiplicar la señal moduladora por la portadora, en este caso un tren de pulsos, que bien podrá ser unipolar o bipolar. Esquema del proceso de modulación Memoria final Página 44 de 60 LCEL Sistema de difusión selectiva con cifrado Estudiemos ambos casos por separado: 1. Modulación por amplitud de pulso unipolar. y (t ) = x(t ). p (t ) siendo p(t ) = 1 !t!< T1 = 0 T1 <!t!< To 2 luego : Y ( w) = X (w) * P( w) siendo : Señal unipolar en dominio del tiempo P( w) = 2π ∞ ∑ a ∂(w − kw k k = −∞ p ) wp = 2π To Teniendo que: a k coeficiente de Fourier 1 a0 = T0 ak = 1 T0 T1 ∫ dt = −T1 T1 ∫e 2T1 T0 − jkw p t dt = −T1 sen(kw p T1 ) πk Modulación en dominio de la frecuencia como T0 = 4T1 en los requisitos a0 = 1 , a k = 0 para k = 2,4,6,... 2 π sen(k ) 2 para impares ak = πk Memoria final Página 45 de 60 LCEL Sistema de difusión selectiva con cifrado 2. Modulación por amplitud de pulso bipolar. En este caso, la señal bipolar tiene como valores: p(t ) = 1 t < T1 = −1 T1 < t < entonces, de T0 2 igual manera que antes: Y ( w) = P( w) * X ( w) siendo P( w) = 2π ∞ ∑ a ∂ ( w − kw k = −∞ k p ) wp = 2π To con a k : ao = 0 ak = Señal bipolar en dominio del T1 T0/2 −T 1 2.senkw pT1 1 − jkw p t − jkw p t − jkw p t e dt − e dt − e dt ∫ = ∫−T 1 ∫T 1 T0 −T 0 / 2 kπ pero como T0 = 4T1 en el caso que tomaremos ak = 2.senk kπ π 2 por lo tanto, para valores de k pares los coeficientes de Fourier tienen valor 0: [a k ] = 0, 1 ,0,− π 1 1 ,0, ,0,... 3π 5π Diseño práctico En principio, el cifrador y el descifrador de audio son exactamente iguales en emisor y receptor. La función del cifrador será modular la señal de audio para que sea transportada. El proceso consistirá en que la señal de entrada, una vez haya pasado por el adaptador de entrada, se multiplicará por la señal portadora y, una vez realizado esto, la filtraremos para quedarnos con el espectro invertido. El descifrador de audio se encontrará en el receptor y será exactamente igual que el cifrador. Invertirá el proceso de modulación de éste. La portadora será una señal cuadrada bipolar con un ciclo de trabajo del 50% y amplitud entre +1 y –1V. Como frecuencia de portadora escogimos un valor de 6,4 Hz. Memoria final Página 46 de 60 LCEL Sistema de difusión selectiva con cifrado Para generarla empleamos un reloj formado por un 555 que dará una onda cuadrada bipolar con el doble de frecuencia, y un JK que logrará dividir la frecuencia entre dos para conseguir un duty cicle del 50%, como ya se explicó en su momento. 1) Modulador: El modulador estará compuesto de varias partes: un inversor, un multiplexor analógico, un filtro de salida del módulo y un limitador de tensión. Para realizar la multiplicación de la señal con la portadora, lo que haremos será utilizar el multiplexor analógico, un 74HC4051. El proceso será muy simple. Como multiplicar la señal por la portadora cuadrada es trocear la señal de acuerdo con el periodo y la amplitud de la portadora (ciclos positivos darán lugar a la señal original; negativos darán lugar a la señal invertida), introduciremos, en una entrada del multiplexor, la señal original y, en la otra, la invertida. El reloj será la señal que elegirá en unos periodos la señal original o la invertida, obteniéndose a la salida una de las dos, en función con el valor de la portadora. El circuito inversor que tratará la señal estará formado por un operacional LF356, cuyas propiedades de eliminar offsets ya hemos comentado al hablar de los seguidores de tensión . Es muy importante que a la entrada del multiplexor analógico controlemos los offsets para evitar un tono a la salida a la frecuencia de la señal portadora. Memoria final Página 47 de 60 LCEL Sistema de difusión selectiva con cifrado Para realizar el inversor, tomaremos como modelo el de la figura. R12 es la Rbias que tiene como función eliminar la Ibias que circula de manera no deseada por las entradas del operacional, como comentamos en la caracterización de los operacionales, y como se describe en el apartado 2.2.1 del manual de “Aspectos prácticos de diseño y medida en laboratorios de electrónica”. Resultará Rbias = R11|| R13 = 5kΩ. El filtro de salida del módulo lo diseñamos de nuevo de orden 4. Para realizar el diseño tomamos valores normalizados: Rn = 1Ω y Cn = 1F. Para realizar el escalado de frecuencias necesitamos conocer el valor del escalado α. Si tomamos como frecuencia de corte superior 7,2KHz: α= 2π*7200 ≈ 45239 Para un escalado razonable de impedancias tomaremos como factor de escalado Ro = 1 kΩ. Resultará entonces: C= Cn = 22µF α * Ro R = Rn * Ro = 1kΩ Memoria final Página 48 de 60 LCEL Sistema de difusión selectiva con cifrado Para un diseño Sallen-Key, como dedujimos anteriormente, necesitamos como ganancias: 1/Q1 = 0,7654 → A1 = 3-1/Q1 = 2,2346 (ganancia del primer filtro) 1/Q2 = 1,8478 → A2 = 3-1/Q2 = 1,1522 (ganancia del segundo filtro) Si incorporamos realimentación al circuito, como se mostraba en la figura anterior, tendremos: - A1=2,2346 10 5 − 1 2,2346 β1 = = 0,447 10 5 RB1 1 − 0,447 1 β1 = ⇒ = = 1,23 R B1 R A1 0,447 1+ R A1 Resultando: RB1= 1,2kΩ RA1= 1kΩ - A2 = 1,1522 10 5 − 1 1,1522 β2 = = 0,868 10 5 RB 2 1 − 0,868 1 β2 = ⇒ = = 0,152 R R A2 0,868 1 + B1 R A1 De este modo obtendremos como resistencias de realimentación del segundo filtro de Sallen-Key: RB2= 150Ω RA2= 1kΩ Memoria final Página 49 de 60 LCEL Sistema de difusión selectiva con cifrado La respuesta en frecuencia teórica del filtro que acabamos de diseñar es de la forma: Y, una vez más, observamos que las medidas experimentales coinciden con la representación teórica obtenida con Maple, tanto en lo que respecta a la frecuencia de corte como al valor de la amplificación. Tras el filtro de salida del módulo colocaremos un adaptador de tensión para contrarrestar la ganancia 2 que hemos obtenido a la salida del filtro. Para ello, utilizaremos un divisor de tensión formado por una resistencia R1 de valor 80kΩ Y un potenciómetro de 100kΩ que regularemos para obtener la salida deseada. 2) Demodulador El demodulador consta de las mismas partes que el modulador: un circuito inversor igual al que hemos estudiado, un multiplexor semejante al comentado más arriba, un filtro de salida que en este caso hemos diseñado de orden seis en lugar de orden cuatro, para disminuir el ruido que pudiera llegar hasta aquí, y el adaptador de tensión. Debido a que previamente hemos descrito la mayor parte de los componentes, nos centraremos en el filtro paso bajo de orden seis. Como frecuencia de corte superior establecimos 4,12 KHz Memoria final Página 50 de 60 LCEL Sistema de difusión selectiva con cifrado Ya que comentamos el desarrollo teórico previo no entraremos en demasiados detalles. El conjunto estará formado por tres filtros concatenados que deben cumplir los siguientes valores de ganancias: 1/Q1 = 0,5176 → A1= 3-1/Q1= 2,28 1/Q2 = 1,4142 → A2 = 3-1/Q2 = 1,5858 1/Q3 = 1,9318 → A3 = 3-1/Q3 = 1,0682 Con lo que obtendremos, con el mismo desarrollo que en los filtros anteriores: R = 8,2 kΩ C = 4,7 ηF RA1 = 8,2kΩ RB1 =12kΩ RA2 = 8,2kΩ RB1 =4,7kΩ RA1 = 8,2kΩ RB1 =520Ω Y la respuesta en frecuencia teórica del nuevo filtro se obtiene, una vez más representando con Maple el valor absoluto de la función de transferencia: Memoria final Página 51 de 60 LCEL Sistema de difusión selectiva con cifrado Una vez más, observamos que los valores experimentales concuerdan con los teóricos, lo que nos obligará a introducir un atenuador resistivo para compensar la elevada ganancia introducida por el filtro (superior a 4). Este atenuador estará formado por una resistencia de valor 82kΩ y un potenciómetro de 100kΩ para lograr contrarrestar el incremento de ganancia del filtro. 2.3. Selector de señal de cifrado Aparece tanto en emisor como en receptor. Se encarga de seleccionar la señal que obtendremos a la salida dependiendo de lo que escojamos en la unidad de entrada del emisor y lo que aparezca en el selector del receptor. De nuevo utilizaremos un multiplexor analógico semejante al utilizado en el apartado anterior. Memoria final Página 52 de 60 LCEL Sistema de difusión selectiva con cifrado o En el emisor las entradas al multiplexor serán la señal cifrada y la original. Según que el bit de cifrado esté activado, escogerá una u otra. o En el receptor mediante el bit de cifrado y el de canal, escogeremos entre la señal cifrada, la que llega del canal, y masa (permite la implementación de canal cerrado). Tras ambos selectores de cifrado colocamos un seguidor de tensión como el comentado al hablar del filtro limitador de ancho de banda. Su función, de nuevo, será aislar la impedancia de salida del selector frente a la siguiente etapa. 2.4. Etapa de salida de potencia (en receptor) La etapa de salida es la encargada de atacar los auriculares. Para ello en las especificaciones del fabricante aparece un montaje con un LM386 como el de la figura. Memoria final Página 53 de 60 LCEL Sistema de difusión selectiva con cifrado ESQUEMAS FIN ESQUEMAS FINALES +5V R1 R2 8 7 6 5 NE555N 1 2 3 C1 C2 Reloj 2·f J 4 Reloj f Q CLK K GENERADOR RELOJ Memoria final Página 54 de 60 Sistema de difusión selectiva con cifrado Memoria final LCEL Página 55 de 60 Sistema de difusión selectiva con cifrado Memoria final LCEL Página 56 de 60 Sistema de difusión selectiva con cifrado Memoria final LCEL Página 57 de 60 Sistema de difusión selectiva con cifrado LCEL CONCLUSIONES Una vez concluido el trabajo podemos asegurar que estamos bastante satisfechos con los resultados. A pesar de que hemos dedicados muchas horas al diseño y construcción, y sobre todo al paso de las placas de inserción al sistema de wire-wrapping, el resultado ha estado a la altura de nuestras expectativas. No nos vamos a engañar: el resultado no es perfecto, hay ciertos aspectos que no hemos logrado solucionar completamente. Por ejemplo, el sistema digital presenta ciertos problemas con el bit de cifrado en el receptor. La mayor parte de las veces no surge ningún error, pero de manera aleatoria, y donde normalmente funciona bien, cada cierto numero de ocasiones, al cambiar el estado del canal, se enciende el bit de cifrado sin que se haya activado en el emisor. Suele suceder una de cada veinte o treinta veces que se cambia el estado del canal. No obstante hemos comprobado en numerosas ocasiones que cuando sucede este problema no es por una falsa detección en el autómata. Si hubiera un mal diseño el error se produciría siempre, o al menos siempre que transmitiésemos la misma palabra en las mismas condiciones, pero en este caso no hay un patrón común para confirmarlo, por lo que deducimos que no se debe a esto. Tras consultarlo con el profesor de nuestro turno, nos aseguró que el problema no era demasiado grave y que las causas podían ir más allá de nuestra capacidad resolutiva. En realidad, las opciones que barajamos con un mayor grado de probabilidad para explicar estos fallos aleatorios son: - Las posible existencia de algún mal contacto o de algún punto en el que, al pulsar sobre la tecla de transmisión, la propia presión que se ejerce sobre la placa provoque algún tipo de cortocircuito entre cables pelados muy próximos. - La presencia de ruido que, a pesar de haber filtrado todos los integrados de la parte digital, podría ocasionar errores aleatorios de ese tipo. - La posible existencia de problemas relacionados con el skew o con pequeños retardos en las líneas de transmisión que son prácticamente imposibles de subsanar con nuestros medios. Por otro lado, consideramos que la calidad del audio es bastante buena, aunque no hemos logrado eliminar un pequeño pitido de fondo que en realidad permite escuchar Memoria final Página 58 de 60 LCEL Sistema de difusión selectiva con cifrado perfectamente el audio. Acotamos la zona de introducción del mismo a uno de los potenciómetros que regula la amplitud de la señal cifrada. Si desconectábamos este, el desaparecía, pero aumentaba considerablemente el volumen de la señal cifrada/descifrada respecto a la transmitida sin cifrar. Es por ello que preferimos mantener un compromiso entre ambas cuestiones intentando equiparar volúmenes de todas las señales y a la vez disminuyendo el pitido de fondo, aunque sin eliminarlo del todo. En cualquier caso, lo cierto es que estas pequeños detalles no sirven sino para confirmarnos la elevada complejidad de todo diseño electrónico y los muchos factores que en él intervienen condicionando pequeños aspectos de su funcionamiento. Una vez más, reiteramos que, desde nuestro punto de vista, el resultado final ha sido altamente positivo y que, a nivel personal, lo cierto es que este laboratorio nos ha parecido ciertamente estimulante y nos a ayudado a ver por primera vez desde una nueva perspectiva – la del diseñador – todos esos pequeños aparatos electrónicos que hoy por hoy forman parte de nuestra realidad cotidiana. Memoria final Página 59 de 60 LCEL Sistema de difusión selectiva con cifrado BIBLIOGRAFÍA 1) Circuitos electrónicos. Análisis, Simulación y Diseño. N.R. Malik. Prentice Hall. 1998. 2) Signals and Systems. Oppenheim, Willsky . Prentice-Hall 1997 3) Enunciado de la práctica del Laboratorio de Electrónica de Circuitos del curso 2001-2002, Sistema de difusión selectiva de mensajes con cifrado de audio y control digital. Departamento de Ingeniería Electrónica. ETSI Telecomunicación. Universidad Politécnica de Madrid 4) Aspectos prácticos de diseño y medida en laboratorios de electrónica. Departamento de Ingeniería Electrónica. ETSI Telecomunicación. Universidad Politécnica de Madrid Memoria final Página 60 de 60