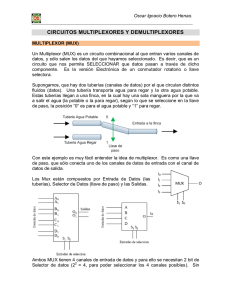

FPGA: Herramientas de diseño

Anuncio

FPGA: Herramientas de diseño Proceso diseño Design and implement a simple unit permitting to speed up encryption with RC5-similar cipher with fixed key set on 8031 microcontroller. Unlike in the experiment 5, this time your unit has to be able to perform an encryption algorithm by itself, executing 32 rounds….. Especificación (Enunciado del problema) Descripción VHDL Library IEEE; use ieee.std_logic_1164.all; use ieee.std_logic_unsigned.all; Simulación funcionalidad entity RC5_core is port( clock, reset, encr_decr: in std_logic; data_input: in std_logic_vector(31 downto 0); data_output: out std_logic_vector(31 downto 0); out_full: in std_logic; key_input: in std_logic_vector(31 downto 0); key_read: out std_logic; ); end AES_core; Síntesis Simulación post-síntesis 2 Proceso diseño Implementación Simulación temporal. Configuración Test en el chip 3 Herramientas simulación Y otras muchas… 4 5 6 Herramientas de síntesis … y otras 7 Síntesis lógica Descripción VHDL Netlist circuito architecture MLU_DATAFLOW of MLU is signal A1:STD_LOGIC; signal B1:STD_LOGIC; signal Y1:STD_LOGIC; signal MUX_0, MUX_1, MUX_2, MUX_3: STD_LOGIC; begin A1<=A when (NEG_A='0') else not A; B1<=B when (NEG_B='0') else not B; Y<=Y1 when (NEG_Y='0') else not Y1; MUX_0<=A1 and B1; MUX_1<=A1 or B1; MUX_2<=A1 xor B1; MUX_3<=A1 xnor B1; with (L1 & L0) select Y1<=MUX_0 when "00", MUX_1 when "01", MUX_2 when "10", MUX_3 when others; end MLU_DATAFLOW; 8 Estrategia • Simulación + Xilinx • Xilinx como herramienta única. 9 Implementación con Xilinx 10 Translation Synthesis Circuit netlist Electronic Design Interchange Format EDIF Timing Constraints Constraint Editor Native Constraint File NCF UCF User Constraint File Translation NGD Native Generic Database file 11 Netlist del circuito 12 Mapping LUT4 LUT1 FF1 LUT5 LUT2 FF2 LUT3 13 Placing FPGA CLB SLICES 14 Routing FPGA Programmable Connections 15 Configuration • Una vez implementado el diseño, se debe generar un fichero para configuración de la FPGA. • bit stream (.bit) • El fichero BIT puede ser utilizado directamente con la FPGA o puede ser convertido a un fichero PROM para almacenar la información de programación. 16 Flujo de diseño: Download Unprogrammed device Programmed device (a) Host computer (b) Device programmer 17 ISE 6.X: Descripción de la herramienta Project Navigator Sources in project HDL editor Processes for Current Source Message Console 19 Xilinx: Proceso de diseño • Paso 1: Diseño • HDL • Esquemáticos. • Paso 2: Síntesis diseño (generación netlist). • Paso 3: Implementación del diseño: • Translate, Map, Place&Route • Paso 4: Configuración de la FPGA. 20 Procesos Paso 1: Diseño Paso 2: Síntesis (generación netlist). MODELO PULL Paso 3: Implementación Paso 4: Configuración 21 Flujo de diseño: Implementación • Implementación incluye varias fases: • Translate: Combina múltiples ficheros en un único netlist. • Map: Agrupa los símbolos lógicos del netlist (puertas) en componentes físicos (slices y IOBs). • Place & Route: Distribuye los componentes en el chip, los conecta y genera informes con análisis temporales. 22 Flujo de diseño: Download • Una vez que el diseño es implementado, se debe generar un fichero final para volcar en la FPGA (bitstream .bit) • El fichero BIT puede ser volcado directamente en la FPGA o convertido a un fichero PROM, que almacena la información de programación. 23 Flujo de diseño: Download Unprogrammed device Programmed device (a) Host computer (b) Device programmer 24 Generando ficheros de informes • La mayoría de los informes se generan de forma automática durante la implementación: • • • • • • Translation Map Place & Route Asynchronous Delay Pad Post Place & Route Static Timing Report 25 Ficheros de informes • Translation (menos importante) • Map. • Importante chequearlo antes de seguir con P&R. • Resumen diseño: Recursos usados (slices, flip-flops, LUTs...). • Lógica eliminada (por falta de recursos disponibles). • Propiedades IOB: Si un flip-flop es usado o no... • Place & Route • Utilización del dispositivo. • Caminos (“nets”) que no se han podido cablear. • Resumen de la temporización: retardos y funcionamiento. • Asynchronous Delay • Información sobre los 20 caminos más largos. • Pad • Post Place & Route Static Timing Report 26