p.32 diseño de un procesador elemental de 8 bits utilizando flex10k

Anuncio

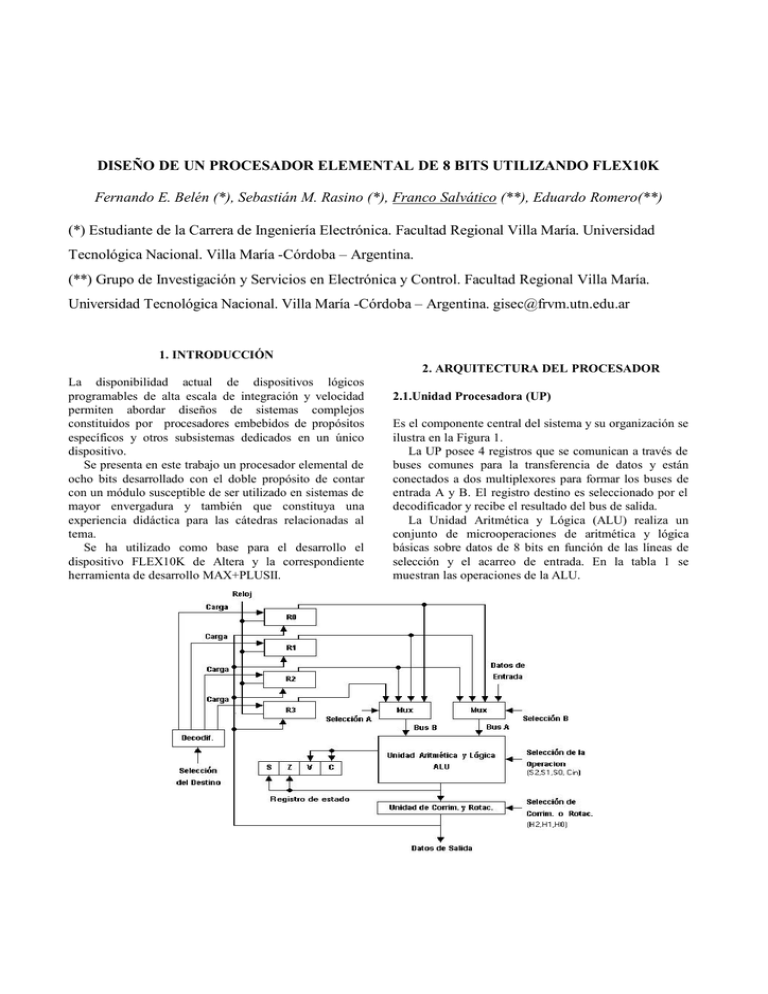

DISEÑO DE UN PROCESADOR ELEMENTAL DE 8 BITS UTILIZANDO FLEX10K Fernando E. Belén (*), Sebastián M. Rasino (*), Franco Salvático (**), Eduardo Romero(**) (*) Estudiante de la Carrera de Ingeniería Electrónica. Facultad Regional Villa María. Universidad Tecnológica Nacional. Villa María -Córdoba – Argentina. (**) Grupo de Investigación y Servicios en Electrónica y Control. Facultad Regional Villa María. Universidad Tecnológica Nacional. Villa María -Córdoba – Argentina. [email protected] 1. INTRODUCCIÓN 2. ARQUITECTURA DEL PROCESADOR La disponibilidad actual de dispositivos lógicos programables de alta escala de integración y velocidad permiten abordar diseños de sistemas complejos constituidos por procesadores embebidos de propósitos específicos y otros subsistemas dedicados en un único dispositivo. Se presenta en este trabajo un procesador elemental de ocho bits desarrollado con el doble propósito de contar con un módulo susceptible de ser utilizado en sistemas de mayor envergadura y también que constituya una experiencia didáctica para las cátedras relacionadas al tema. Se ha utilizado como base para el desarrollo el dispositivo FLEX10K de Altera y la correspondiente herramienta de desarrollo MAX+PLUSII. 2.1.Unidad Procesadora (UP) Es el componente central del sistema y su organización se ilustra en la Figura 1. La UP posee 4 registros que se comunican a través de buses comunes para la transferencia de datos y están conectados a dos multiplexores para formar los buses de entrada A y B. El registro destino es seleccionado por el decodificador y recibe el resultado del bus de salida. La Unidad Aritmética y Lógica (ALU) realiza un conjunto de microoperaciones de aritmética y lógica básicas sobre datos de 8 bits en función de las líneas de selección y el acarreo de entrada. En la tabla 1 se muestran las operaciones de la ALU. Figura 1. Unidad Procesadora. Tabla 1. Operaciones de la ALU Código binario S2 Cin S1 S0 Símbol o 0 0 0 0 TSF Transferencia A 0 1 0 0 INC Incremento de A 0 0 0 1 ADD Adición A + B 0 1 1 0 SUB Resta A – B 0 1 0 1 ADC 0 0 1 0 CO1 0 0 1 1 DEC 0 1 1 1 TRC 1 0 0 0 AND Adición con acarreo A más complemento a 1 de B Decremento de A en uno Transferencia de A con reiniciación de acarreo A AND B 1 0 0 1 OR A OR B 1 0 1 0 XOR A XOR B 1 0 1 1 COM Complemento de A Rotación transfiere la información, o la rota hacia la derecha o izquierda. Las funciones de esta unidad se muestran en la Tabla 2. Función Se implementa un registro de estado de cuatro bits útil para verificar ciertas relaciones de A y B después de una operación de la ALU. Los bits de estado son: S (signo), Z (cero), C (acarreo) y V (desbordamiento). La Unidad de Corrimiento transfiere la información corriéndola a la derecha o a la izquierda perdiendo el bit más o menos significativo respectivamente. La Unidad de Tabla 2. Funciones de la Unidad de Corrimiento y Rotación Cod. binario Símbolo Función H0 H1 H2 0 0 0 NSH No hay corrimiento Corrimiento a la izquierda con 0 0 1 SHL entrada en serie en 0 Corrimiento a la derecha con entrada 0 1 0 SHR en serie en 0 Sólo ceros a la salida de la unidad 0 1 1 ZERO de corrimiento 1 0 0 RLC Rotación a la izquierda con acarreo 1 0 1 ROL Rotación a la izquierda 1 1 0 ROR Rotación a la derecha 1 1 1 RRC Rotación a la derecha con acarreo 2.2.Control de la unidad Procesadora El sistema de control (figura 2) se basa en una memoria ROM de 64 palabras de 31 bits, un Registro de Direcciones de Control (CAR) y dos multiplexores (MUX1 y MUX2). Las operaciones de MUX2 se muestran en la Tabla 3. Figura 2. Unidad de Control Tabla 3. Operaciones de MUX2 Selección Símbolo V0 V1 V2 0 0 0 NEXT 0 0 1 LAD 0 1 0 LC 0 1 1 LNC 1 0 0 LZ 1 0 1 LNZ 1 1 0 LS 1 1 1 LV Función Ir a la siguiente dirección incrementando CAR Carga de dirección en CAR (bifurcación incondicional) Carga en acarreo (bifurcar si C = 1) Carga cuando no hay acarreo (bifurcar si C = 0) Carga en cero (bifurcar si Z = 1) Carga cuando no es cero (bifurcar si Z = 0) Carga en signo (bifurcar si S = 1) Carga en desbordamiento (bifurcar si V = 1) Cada microinstrucción de la memoria de control (tabla 4) contiene 13 bits de una palabra de control para el procesador, 10 bits para seleccionar la siguiente dirección de CAR y 8 bits de datos través de Datos de Entrada como alternativa a la carga de datos externa. Tabla 4. Palabra de Control y Microinstrucción Posición del bit de la palabra de control T30 – T23 T22 – T17 T16 – T14 (V0-V1-V2) T13 T12 – T11 (W0-W1) T10-T9 (Q0-Q1) T8 – T7 T6 – T5 – T4 – T3 (S2-S1S0-Cin) T2 – T1 –T0 (H0-H1-H2) Contenido memoria de control. Esta contiene una microinstrucción especificando una microoperación de la UP. MUX1 y MUX2 establecen la siguiente operación de CAR. En la siguiente transición del reloj se transfiere el resultado al registro destino, se actualizan los bits de estado y se coloca una nueva dirección en CAR. 3. PROGRAMACIÓN DE LA MEMORIA ROM Y SIMULACIÓN. A modo de ejemplo se implementa una rutina que utiliza algunas de las microinstrucciones disponibles: ?? Carga dato externo en el registro R2 (00001111). ?? Realiza la operación lógica OR entre el contenido del registro R2 y el dato (01010101) contenido en la microinstrucción (T23 – T30) y lo almacena en el registro R0. ?? Rota el contenido del registro R0 a la izquierda. ?? Realiza el corrimiento del contenido del registro R0 a la izquierda. ?? Realiza el complemento del contenido del registro R0. ?? Decrementa el contenido del registro R0. ?? Realiza la operación de sustracción siguiente R0 ? R0 – T, llamando T a T23 – T30, cuyo contenido es 00000001. El contenido de la ROM se muestra en la figura 3. Dato. Dirección de Memoria Selección del MUX2. Selección de MUX1. Selección del BUS A. Selección del BUS B. Selección del registro destino Selección de Unidad Aritmética y Lógica Selección de Unidad de Corrimiento y Rotación. La selección de la entrada 0 de MUX2 habilita la operación de incremento en CAR, mientras que la de la entrada 1 carga una nueva dirección en el registro. Esto produce una bifurcación incondicional a la dirección dada por los bits 17 a 22 de la microinstrucción presente (con bit T13 en 0). Los bits de estado de la UP y también los valores complementados de C y Z se aplican a las entradas de MUX2. La carga de direcciones en CAR a través de MUX1 depende del valor del bit T13. Si es 0, se carga el campo de direcciones de la microinstrucción; si es 1, se carga una dirección especificada por un medio externo. Una operación comienza cuando en la transición del reloj el registro CAR recibe una nueva dirección de la Figura 3. Contenido de la ROM Figura 4. Resultados de simulación La simulación realizada en MAX+plus ll de ALTERA (figura 4), muestra la secuencia realizada, donde ENT[7..0] representa el dato externo, y Z[7..0] muestra los datos de salida de la unidad procesadora. 4. CONCLUSIONES Se presentó en este trabajo el desarrollo de un procesador elemental de 8 bits con control microprogramado implementado en el dispositivo FLEX10K de Altera. Se cuenta de esta manera con un sistema susceptible de ser integrado en sistemas de mayor complejidad. Como trabajo futuro se prevé desarrollar un ensamblador que permita una rápida y más cómoda programación del procesador. 5. BIBLIOGRAFÍA G. Jaquenod y M. De Giusti. “Diseño de microcontroladores empotrados mediante procesamiento serial: análisis usando FLEX10K para sintetizar un microcontrolador COP8Sax”, Memorias VII Workshop IBERCHIP IWS’2001, Montevideo, Uruguay, Marzo 2001. V. Nelson, H. Troy Nagle, B. Carrol, J. Irwin. Análisis y diseño de circuitos lógicos digitales. Prentice Hall, 1996. Z. Salcic , A. Smailagic. Digital Systems Design and Prototyping Using Field Programmable Logic. Kluwer Academic Publishers, 1997. Altera Corporation. Max+Plus II. Getting Started. 1997. M. Morris Mano. Ingeniería Computacional. Diseño del Hardware. Prentice Hall, México, 1992.