Aritmetica Computacional 2ª Parte

Anuncio

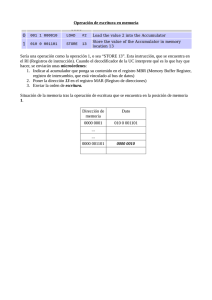

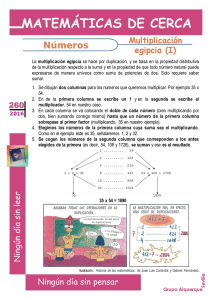

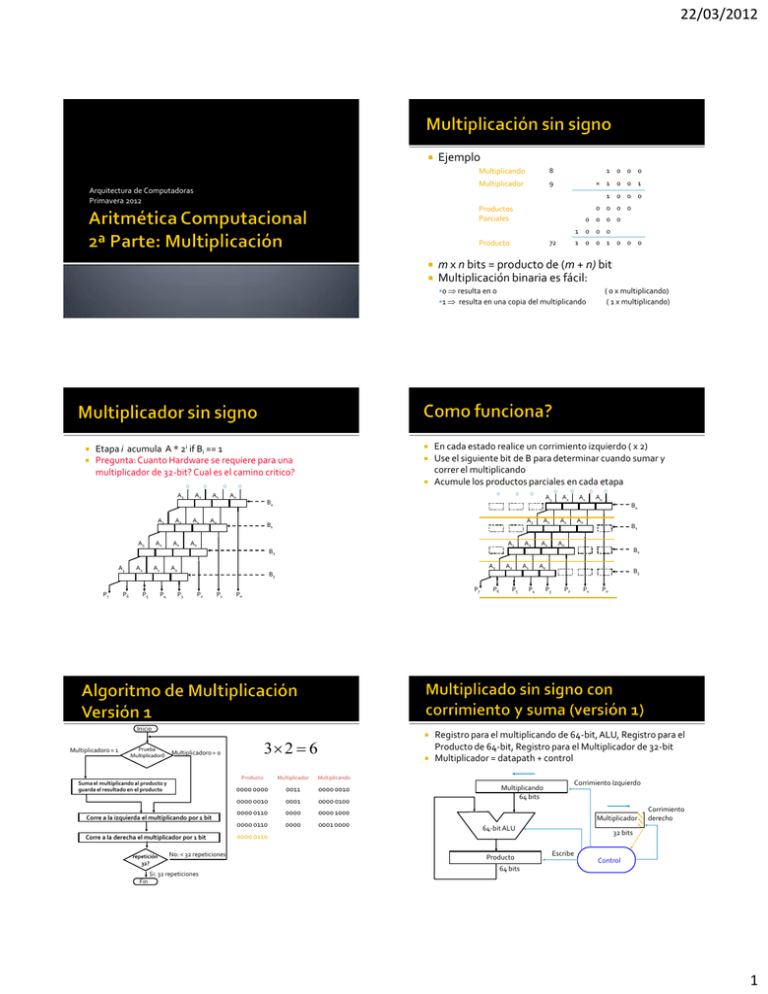

22/03/2012 Arquitectura de Computadoras Primavera 2012 Ejemplo Multiplicando 8 1 0 0 0 Multiplicador 9 × 1 0 0 1 1 0 0 0 0 0 0 0 Productos Parciales 0 0 0 0 1 0 0 0 72 Producto 1 0 0 1 0 0 0 m x n bits = producto de (m + n) bit Multiplicación binaria es fácil: 0 resulta en 0 1 resulta en una copia del multiplicando Etapa i acumula A * 2i if Bi == 1 Pregunta: Cuanto Hardware se requiere para una multiplicador de 32-bit? Cual es el camino critico? 0 A3 A3 A3 A2 A2 A1 0 0 A2 A1 A1 0 En cada estado realice un corrimiento izquierdo ( x 2) Use el siguiente bit de B para determinar cuando sumar y correr el multiplicando Acumule los productos parciales en cada etapa 0 A0 0 0 0 A3 B0 A0 ( 0 x multiplicando) ( 1 x multiplicand0) 0 A2 0 A1 0 A0 B0 A3 B1 A0 A3 A2 A2 A1 A1 A0 B1 A0 B2 B2 A3 P7 P6 A2 A1 P5 A3 A0 P4 Prueba Multiplicador0 P3 P2 P1 P7 P0 Corre a la izquierda el multiplicando por 1 bit Corre a la derecha el multiplicador por 1 bit No: < 32 repeticiones Si: 32 repeticiones 3 2 6 Multiplicador0 = 0 Suma el multiplicando al producto y guarda el resultado en el producto repetición 32? A1 A0 B3 B3 Inicio Multiplicador0 = 1 A2 Producto Multiplicador Multiplicando 0000 0000 0011 0000 0010 0000 0010 0001 0000 0100 0000 0110 0000 0000 1000 0000 0110 0000 0001 0000 P6 P5 P4 P3 P2 P1 P0 Registro para el multiplicando de 64-bit, ALU, Registro para el Producto de 64-bit, Registro para el Multiplicador de 32-bit Multiplicador = datapath + control Corrimiento Izquierdo Multiplicando 64 bits Multiplicador 64-bit ALU 32 bits 0000 0110 Producto Corrimiento derecho Escribe Control 64 bits Fin 1 22/03/2012 Registro para el multiplicando de 64-bit, ALU, Registro para el Producto de 64-bit, Registro para el Multiplicador de 32-bit Multiplicador = datapath + control Corrimiento Izquierdo Multiplicando 64 bits Multiplicador 64-bit ALU Muchos de los 64-bits son desperdiciados Los bit menos significativos del producto nunca Corrimiento derecho cambian una vez formados Escribe Control 64 bits 0 A3 0 0 A2 A1 A2 Inicio B0 A0 B1 A3 A2 A1 En lugar de realizar el corrimiento al multiplicando a la izquierda, corre el producto a la derecha? 0 A0 A1 Los ceros insertados a la izquierda del multiplicado son corridos (shifted) 32 bits Producto A3 La mitad de l0s bits en el multiplicando siempre son cero A0 Multiplicando permanece sin moverse y el producto se mueva a la derecha. B2 Multiplicador0 = 1 Prueba Multiplicador0 3 2 6 Multiplicador0 = 0 Suma el multiplicando con la mitad izquierda del producto y guarda el resultado en la mitad izquierda del producto Corre a la derecha el producto por 1 bit Corre a la derecha el multiplicador por 1 bit A3 A2 A1 A0 B3 repetición 32? Product0 Multiplicador Multiplicando 0000 0000 0011 0010 0000 0010 0001 0000 0001 0010 0011 0000 0001 0010 0001 1000 0000 0010 0000 1100 0000 0010 0000 0110 0000 0010 No: < 32 repeticiones Si: 32 repeticiones P7 P6 P5 P4 P3 P2 P1 Fin P0 Registro para el Multiplicando de 32-bit, 32 -bit ALU, registro para el producto de 64-bit, registro para el multiplicador de 32-bit Multiplicand0 32 bits Multiplicad0r 32-bit ALU 32 bits 64 bits El registro del producto desperdicia espacio. Este espacio desperdiciado corresponde exactamente al tamaño del registro del multiplicador Solución: Combina el registro del multiplicador y el producto Shift derech0 Product0 Shift Derecho Control Escribe 2 22/03/2012 Inicio Registro para el multiplicando 32-bit, 32 -bit ALU, Registro del Producto de 64-bit, (Registro del Multiplicador 0-bit) Multiplicador0 = 1 3 2 6 Prueba Multiplicador0 Multiplicador0 = 0 Multiplicando Suma el multiplicando con la mitad izquierda del producto y guarda el resultado en la mitad izquierda del producto 32 bits 32-bit ALU Corre a la derecha el producto por 1 bit Shift Derecho Producto (Multiplicador) 64 bits Control Multiplicando 0000 0011 1 0010 0011 0010 0010 0001 0001 0010 2 0011 0001 3 0001 1000 0010 0010 4 0000 1100 0010 0000 0110 0010 Escribe repetición 32? Producto/Multiplicandor No: < 32 repeticiones Si: 32 repeticiones Fin En un solo paso se realizan dos acciones: corrimiento a la derecha del Producto y del Multiplicador (debido a que están combinados) El resultado requiere un registro especial de 64-bits. En la arquitectura MIPS este registro es Hi and Lo para la parte izquierda y derecha del producto Como lo podemos hacer mas rápido? Como se puede realizar la multiplicación entre números con signo? Ejemplo Multiplicando -5 1 0 1 1 Multiplicador 3 × 0 0 1 1 1 1 1 1 0 1 1 1 1 1 0 1 1 Productos Parciales 0 0 0 0 0 0 0 0 0 La solución mas fácil es convertir los dos números a positivos y recordar complementar el producto cuando termine la multiplicación (el bit del signo no se toma en cuanta, por lo cual solo se requieren 31 repeticiones) Aplicar la definición del complemento a 2’s ▪ Necesitan realizarse la extensión del signo en los productos parciales y restarlo al final El algoritmo de Booth es una forma elegante de multiplicar números con signo usando el mismo hardware y ahorrando algunos ciclos Producto -15 1 1 1 0 0 0 1 Lo único que se debe incluir es la extensión de signo del multiplicando ▪ Puede manejar múltiples bits al mismo tiempo El algoritmo Booth disminuye el número de productos parciales por medio de agrupar los bits del multiplicador en pares Dependiendo de la combinación de bits decide que acción tomar Acelera la ejecución del multiplicador usando corrimientos y disminuyendo el número de productos parciales Instrucción Ejemplo Multiplicación con mult $s1,$s2 signo significado Comentario Hi:Lo = $s1 × $s2 Multiplica el contenido del registro S1 por el registro S2 y el resultado es almacenado en Hi y Lo Multiplicación sin signo Multiplica el contenido del registro S1 por el registro S2. multu $s1,$s2 Hi:Lo = $s1 × $s2 Asume que ambos números son sin signo. El resultado es almacenado en Hi y Lo Mueve desde Hi mfhi $s1 $s1 = Hi Obtiene la parte alta del resultado de la multiplicación Mueve desde Lo mflo $s2 $s2 = Lo Obtiene la parte baja del resultado de la multiplicación 3 22/03/2012 Instrucción and or xor nor and immediate or immediate xor immediate shift left logical shift right logical shift right arithm. Ejemplo and $1,$2,$3 or $1,$2,$3 xor $1,$2,$3 nor $1,$2,$3 andi $1,$2,10 ori $1,$2,10 xori $1, $2,10 sll $1,$2,10 srl $1,$2,10 sra $1,$2,10 Significado $1 = $2 & $3 $1 = $2 | $3 $1 = $2 $3 $1 = ~($2 |$3) $1 = $2 & 10 $1 = $2 | 10 $1 = ~$2 &~10 $1 = $2 << 10 $1 = $2 >> 10 $1 = $2 >> 10 shift left logical shift right logical shift right arithm. sllv $1,$2,$3 srlv $1,$2, $3 srav $1,$2, $3 $1 = $2 << $3 $1 = $2 >> $3 $1 = $2 >> $3 Comentarios 3 registros ; AND Logico 3 registros; OR Logico 3 registros; XOR Logico 3 registros; NOR Logico AND reg y constante OR reg y constante XOR reg y constante Corrimiento Izq. por constante Corrimiento der. por constante Corrimiento der. (extensión de signo) Corrimiento Izq. por variable Corrimiento der. por variable Corrimiento aritmético derecho por variable Bloque básico Que se debe introducir en el MSB? Cuantos niveles se requieren para un shifter de 32-bits? Que tal si se usan Multiplexores de 4-bits? A7 A6 A5 A4 sel A B 1 0 D A3 A2 A1 S2 S 1 S0 A0 1 0 1 0 1 0 1 0 1 0 1 0 1 0 1 0 1 0 1 0 1 0 1 0 1 0 1 0 1 0 1 0 Dos clases de corrimientos: • lógico - valor recorrido es siempre “0” "0" • msb lsb "0" aritmético – en corrimientos derechos el signo se extiende msb lsb "0" S0 (0,1) S1 (0, 2) S2 (0, 4) S3 (0, 8) 1 8-bit shifter derecho 0 1 R7 0 1 R6 R5 0 1 1 0 R4 R3 0 1 R2 0 1 0 R1 1 0 Si se agregan conexiones de izquierda a derecha, entonces también se puede realizar la rotación. (MIPS no incluye rotaciones pero algunas otras arquitecturas lo soportan) R0 Technology-dependent solutions: transistor per switch Extrae 32-bits de 64 bits Y SR3 SR2 SR1 SR0 X D3 Shift derecho D2 A6 R D1 Corre A por i bits (sa= cantidad de corrimiento derecho) Logico: Y = 0, X=A, sa = i Aritmetico? Y = _, X=_, sa= __ Rotación? Y = _, X=_, sa= __ Shift izq.? Y = _, X=_, sa= __ Y A5 X 32 32 D0 A4 Shift Derecho 32 A3 A2 A1 A0 R 4