0 ADD b,f,r/m ADD w,f,r/m ADD b,t,r/m ADD w,t,r/m ADD b,ia ADD w

Anuncio

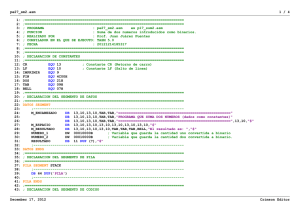

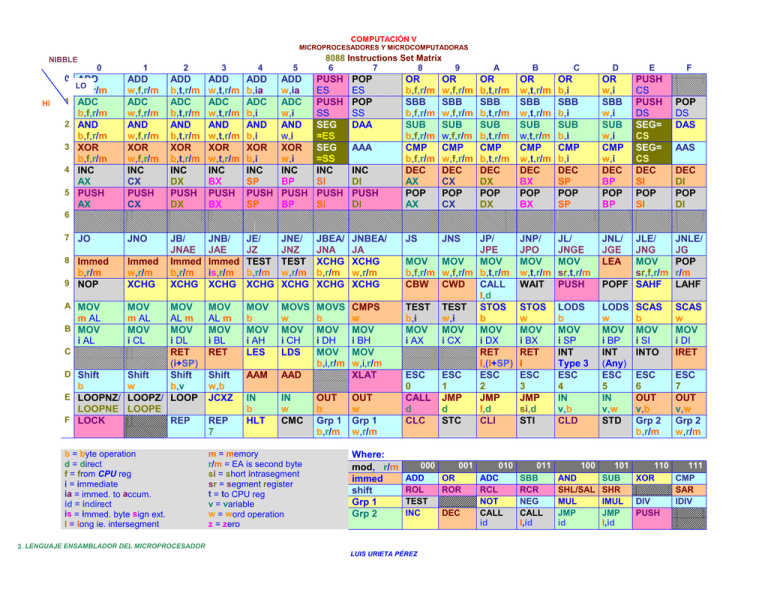

COMPUTACIÓN V MICROPROCESADORES Y MICROCOMPUTADORAS NIBBLE 0 2 3 4 5 ADD w,f,r/m ADC w,f,r/m AND w,f,r/m XOR w,f,r/m INC CX PUSH CX ADD b,t,r/m ADC b,t,r/m AND b,t,r/m XOR b,t,r/m INC DX PUSH DX ADD w,t,r/m ADC w,t,r/m AND w,t,r/m XOR w,t,r/m INC BX PUSH BX ADD b,ia ADC b,i AND b,i XOR b,i INC SP PUSH SP ADD w,ia ADC w,i AND w,i XOR w,i INC BP PUSH BP PUSH ES PUSH SS SEG =ES SEG =SS INC SI PUSH SI POP ES POP SS DAA 7 JO JNO 8 Immed Immed w,r/m XCHG JB/ JNAE Immed b,r/m XCHG JNB/ JAE Immed is,r/m XCHG JE/ JZ TEST b,r/m XCHG JNE/ JNZ TEST w,r/m XCHG JBEA/ JNA XCHG b,r/m XCHG JNBEA/ JA XCHG w,r/m XCHG MOV AL m MOV i DL C RET (i+SP) D Shift Shift Shift b w b,v E LOOPNZ/ LOOPZ/ LOOP LOOPNE LOOPE F LOCK REP MOV AL m MOV i BL RET MOV b MOV i AH LES MOVS w MOV i CH LDS MOVS b MOV i DH MOV b,i,r/m Shift w,b JCXZ AAM AAD CMPS w MOV i BH MOV w,i,r/m XLAT IN b HLT IN w CMC b = byte operation d = direct f = from CPU reg i = immediate ia = immed. to accum. id = indirect is = immed. byte sign ext. l = long ie. intersegment m = memory r/m = EA is second byte si = short intrasegment sr = segment register t = to CPU reg v = variable w = word operation z = zero 0 ADD LO b,f,r/m HI 8088 Instructions Set Matrix 6 7 8 1 1 ADC 2 3 4 5 b,f,r/m AND b,f,r/m XOR b,f,r/m INC AX PUSH AX AAA INC DI PUSH DI 9 A B OR b,f,r/m SBB b,f,r/m SUB b,f,r/m CMP b,f,r/m DEC AX POP AX OR w,f,r/m SBB w,f,r/m SUB w,f,r/m CMP w,f,r/m DEC CX POP CX OR b,t,r/m SBB b,t,r/m SUB b,t,r/m CMP b,t,r/m DEC DX POP DX OR w,t,r/m SBB w,t,r/m SUB w,t,r/m CMP w,t,r/m DEC BX POP BX OR b,i SBB b,i SUB b,i CMP b,i DEC SP POP SP C OR w,i SBB w,i SUB w,i CMP w,i DEC BP POP BP D E JS JNS JP/ JPE MOV MOV MOV b,f,r/m w,f,r/m b,t,r/m CBW CWD CALL I,d TEST TEST STOS b,i w,i b MOV MOV MOV i AX i CX i DX RET I,(I+SP) ESC ESC ESC 0 1 2 CALL JMP JMP d d I,d CLC STC CLI JNP/ JPO MOV w,t,r/m WAIT JL/ JNGE MOV sr,t,r/m PUSH JNL/ JGE LEA JLE/ JNG MOV sr,f,r/m POPF SAHF JNLE/ JG POP r/m LAHF STOS w MOV i BX RET I ESC 3 JMP si,d STI LODS b MOV i SP INT Type 3 ESC 4 IN v,b CLD LODS w MOV i BP INT (Any) ESC 5 IN v,w STD SCAS b MOV i SI INTO SCAS w MOV i DI IRET ESC 6 OUT v,b Grp 2 b,r/m ESC 7 OUT v,w Grp 2 w,r/m 000 001 ADD OR ROL ROR TEST INC DEC 011 SBB RCR NEG CALL I,id PUSH CS PUSH DS SEG= CS SEG= CS DEC SI POP SI F POP DS DAS AAS DEC DI POP DI 6 b,r/m 9 NOP A MOV m AL B MOV i AL MOV m AL MOV i CL REP 7 OUT b Grp 1 b,r/m OUT w Grp 1 w,r/m Where: mod, r/m immed shift Grp 1 Grp 2 3. LENGUAJE ENSAMBLADOR DEL MICROPROCESADOR LUIS URIETA PÉREZ 010 ADC RCL NOT CALL id 100 101 110 111 AND SUB XOR CMP SHL/SAL SHR SAR MUL IMUL DIV IDIV JMP JMP PUSH id I,id