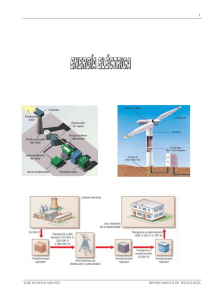

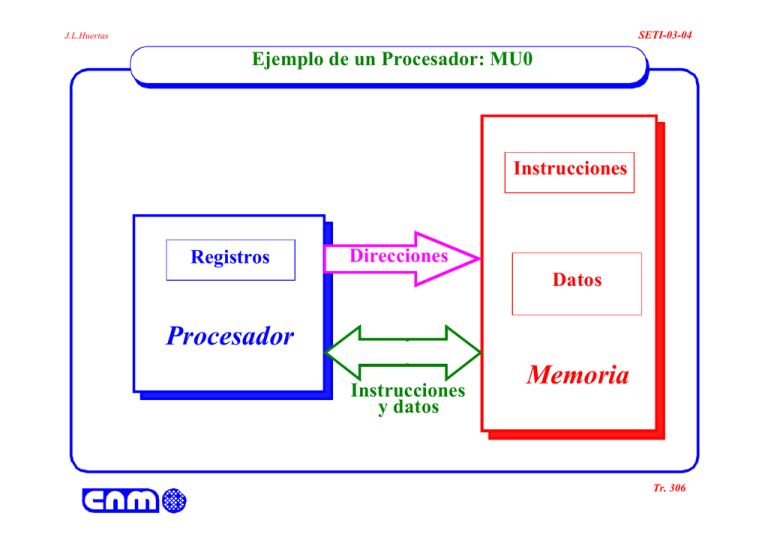

Memoria Procesador

Anuncio

SETI-03-04

J.L.Huertas

Ejemplo de un Procesador: MU0

Instrucciones

Registros

Direcciones

Datos

Procesador

Instrucciones

y datos

Memoria

Tr. 306

SETI-03-04

J.L.Huertas

float fir_filter(float input, float *coef, int n, float *history

{

int i;

float *hist_ptr, *hist1_ptr, *coef_ptr;

float output;

hist_ptr = history;

hist1_ptr = hist_ptr;

/* use for history update */

coef_ptr = coef + n - 1;

/* point to last coef */

/*form output accumulation */

output = *hist_ptr++ * (*coef_ptr_);

for(i = 2; i < n; i++)

{

*hist1_ptr++ = *hist_ptr; /* update history array */

output += (*hist_ptr++) * (*coef_ptr-);

}

output += input * (*coef_ptr); /* input tap */

*hist1_ptr = input;

/* last history */

return(output);

}

Tr. 307

SETI-03-04

J.L.Huertas

Elementos del MU0

·

·

·

Componentes:

Un conjunto de dispositivos que configuran la estructura del MU0

Conjunto de Instrucciones:

Las operaciones que pueden ejecutarse con la estructura del MU0

Configuración Lógica:

La estructura operativa del MU0, formada por dos elementos:

w El Camino de Datos

w La Lógica de Control

q MU0 tiene 16 bits, con 12 bits de espacio de direcciones:

4 bits

cod.op.

12 bits

Dirección (S)

Tr. 308

SETI-03-04

J.L.Huertas

Componentes del MU0

·

·

·

·

·

Contador de Programa (PC)

Acumulador (ACC)

Unidad Aritmético-Lógica (ALU)

Registro de Instrucciones (IR)

Lógica de control y de decodificación de instrucciones

Tr. 309

SETI-03-04

J.L.Huertas

Instrucciones del MU0

Instrucción

Cod.Oper.

Efecto

LDA S

0000

ACC:=mem16[S]

STO S

0001

mem16[S]:=ACC

ADD S

0010

ACC:=ACC+mem16[S]

SUB S

0011

ACC:=ACC-mem16 [S]

JMP S

0100

PC:=S

JGE S

0101

if ACC > 0 PC:=S

JNE S

0110

if ACC = 0 PC:=S

STP

0111

stop

Tr. 310

SETI-03-04

J.L.Huertas

Tipos de Instrucciones

·

·

·

·

·

Procesamiento de datos (ej. ADD, SUB)

Movimiento de datos (copian datos de un lugar de la memoria

a otro o de la memoria a los registros del procesador, ej. STO, LDA)

Control de flujo (cambia la ejecución de una parte del

programa a otra diferente, ej. JMP)

Especiales (controlan el estado de ejecución del procesador, ej. STP)

Puede haber instrucciones que entren en más de una categoría

Tr. 311

SETI-03-04

J.L.Huertas

Direccionamiento de Instrucciones

Toda instrucción precisa:

wel nombre de la instrucción

wel lugar de memoria donde están los operandos

wel lugar de memoria donde debe guardarse el resultado

wla dirección de la próxima instrucción a ejecutar

Forma “natural” de una instrucción: 4-direcciones

q bits

cod.op.

m bits

m bits

m bits

m bits

direcc. op.1 direcc. op.2 direcc. dest. direcc. próx

Ejemplo: ADD d, s1, s2, next_i; d:=s1+s2

Tr. 312

SETI-03-04

J.L.Huertas

Direccionamiento simplificado de Instrucciones

Instrucción 3-direcciones: suponiendo que la próxima instr.

está en la dirección siguiente

q bits

m bits

m bits

m bits

cod.op.

direcc. op.1 direcc. op.2 direcc. dest.

Ejemplo: ADD d, s1, s2, ; d:=s1+s2

Instrucción 2-direcciones: suponiendo que el registro de destino

es el mismo que el registro fuente

q bits

m bits

m bits

cod.op.

direcc. op.1 direcc. dest.

Ejemplo: ADD d, s1 ; d:=d+s1

Instrucción 1-dirección: suponiendo implícito el registro de destino

q bits

m bits

cod.op.

direcc. op.1

Ejemplo: ADD s1 ; acumulador:=acumulador+s1

Tr. 313

SETI-03-04

J.L.Huertas

Camino de Datos del MU0

Bus de Direcciones

Control

Contador de

Programa

Registro de

Instrucciones

Memoria

ALU

Acumulador

Bus de Datos

Tr. 314

J.L.Huertas

SETI-03-04

Tr. 315

SETI-03-04

J.L.Huertas

Organización a nivel de Transferencias de Registro del MU0

Reset

Ex/ft (execute/fetch)

Memoria

Mux 1

MEMrq

IRce

IR

RnW

MU0

opcode

0

PC

PCce

Asel

ALUfs

B

ALU

ACCoe

A

ACCce

ACC[15]

ACCz

Bsel

ACC

0 Mux 1

Tr. 316

SETI-03-04

J.L.Huertas

Unidad de Control del MU0: Comandos de cada Instrucción

a

b

c

d α β

γ

δ

ε

φ

η

ϕ κ

λ

Reset

xxxx

1

x

x

x

0

0

1

1

1

0

=0

1

1

0

LDA S

0000

0

0

x

x

1

1

1

0

0

0

=B

1

1

1

0000

0

1

x

x

0

0

0

1

1

0

B+1

1

1

0

0001

0

0

x

x

1

x

0

0

0

1

x

1

0

1

0001

0

1

x

x

0

0

0

1

1

0

B+1

1

1

0

0010

0

0

x

x

1

1

1

0

0

0

A+B

1

1

1

0010

0

1

x

x

0

0

0

1

1

0

B+1

1

1

0

0011

0

0

x

x

1

1

1

0

0

0

A-B

1

1

1

0011

0

1

x

x

0

0

0

1

1

0

B+1

1

1

0

JMP S

0100

0

x

x

x

1

0

0

1

1

0

B+1

1

1

0

JGE S

0101

0

x

x

0

1

0

0

1

1

0

B+1

1

1

0

0101

0

x

x

1

0

0

0

1

1

0

B+1

1

1

0

0110

0

x

0

x

1

0

0

1

1

0

B+1

1

1

0

0110

0

x

1

x

0

0

0

1

1

0

B+1

1

1

0

0111

0

x

x

x

1

x

0

0

0

0

x

0

1

0

STO S

ADD S

SUB S

JNE S

STP

Entradas

Salidas

Tr. 317

SETI-03-04

J.L.Huertas

Entradas

Salidas

a

Reset

b

Ex/ft

c

ACCz

d

ACC15

α

Asel

α

Bsel

β

ACCce

γ

PCce

δ

IRce

ε

ACCoe

φ

ALUfs

η

MEMrq

ϕ

RnW

κ

Ex/ft

Tr. 318

SETI-03-04

J.L.Huertas

Evolución

Hasta 1980-85: Sólo sistemas CISC

q Instruciones muy complejas

q Uso de microcódigo en ROM para implementar las operaciones más frecuentes.

q Instrucciones de tamaño variable y nuchos formatos diferentes

q Valores en memoria pueden ser utilizados directamente como operandos

q Cada instrucción requiere muchos ciclos de reloj

Desde 1985: Aparecen sistemas RISC

q Instruciones más simples

Desde 1985:

q

tamaño

fijo (32-b) y pocos formatos distintos

q Instruciones

Instruciones de

más

simples

q

banco de de

registros

32-b) y pocos formatos distintos

q Un

Instruciones

tamaño(32

fijode(32-b)

q

instrucciones

que procesan

datos operan sólo sobre los registros

q Las

Un banco

de registros

(32 de 32-b)

q

instruccionesque

están

“separadas”

las que

a memoria

q Estas

Las instrucciones

procesan

datos de

operan

sóloacceden

sobre los

registros

q

Cada

instrucción

requiere

un

único

ciclo

de

reloj

q Estas instrucciones están “separadas” de las que acceden a memoria

q

lógica

de decodificación

se haceciclos

con puertas

q La

Cada

instrucción

requiere muchos

de relojlógicas

q Las instrucciones se ejecutan en “pipeline”

Tr. 319

SETI-03-04

J.L.Huertas

Ejecución de Instrucciones

Ejecución de una instrucción típica: 6 pasos

fetch

decodif.

registr.

ALU

memor.

result.

ejecución

tiempo

1.- Sacar la instrucción de la memoria

2.- Decodificar para saber de qué instrucción se trata

3.- Acceder a los operandos que puedan ser necesarios desde el banco de registros

4.- Combinar los operandos para formar:

a) el resultado

b) una dirección de memoria

5.- Acceder a la memoria para obtener un dato-operando

6.- Escribir el resultado en el banco de registros

Tr. 320

SETI-03-04

J.L.Huertas

Pipelining

Métodos para acelerar la ejecución de instrucciones:

a.- Varios/muchos registros en “pipeline”

b.- Caché

3.- Instrucciones super-escalares

fetch

decodif.

fetch

registr.

decodif.

fetch

ALU

registr.

decodif.

memor.

result.

ALU

memor.

result.

ALU

memor.

registr.

result.

tiempo

Tr. 321

SETI-03-04

J.L.Huertas

Pipelining: Conflictos

fetch

fetch

decodif.

fetch

decodif.

registr.

ALU

fetch

decodif.

registr.

registr.

decodif.

ALU

memor.

memor.

result.

ALU

memor.

result.

result.

espera

registr.

ALU

memor.

result.

tiempo

Tr. 322

SETI-03-04

J.L.Huertas

Evolución de los Sistemas de Tratamiento de Información

RISC

CISC

SPARC

INTEL

AMD

MIPS

ARM

LEON

Virtex

Tr. 323

SETI-03-04

J.L.Huertas

ALU para ARM6

Registro Oper. A

Registro Oper. B

Puertas XOR

Puertas XOR

Invierte A

Invierte B

Cin

Funciones Lógicas

Función

Selector

Sumador

C

V

Mux Resultados

Detector de Cero

N

Z

Tr. 324

SETI-03-04

J.L.Huertas

Buses y Registros en ARM6

Registro de Direcciones

Incrementador

Ad

A

B

Banco de Registros

PC

Inc

Multiplicador

W

ALU

Desplazador

shift out

Data In

Tubería de Instrucciones

Data Out

Din

Tr. 325

SETI-03-04

J.L.Huertas

Estructura de Control de ARM6

Coprocesador

Instrucción

Control

Multiplicac.

PLA Decodif.

Cuenta

Ciclo

Load/Store

Control

Direcciones

Control

Registros

Control

ALU

Control

Desplazador

Tr. 326

SETI-03-04

J.L.Huertas

Organización a nivel de Transferencias de Registro del MU0

MEMrq

IRce

RnW

MU0

opcode

PCce

Asel

ACCoe

ALUfs

ACCce

ACC[15]

ACCz

Bsel

Tr. 327

SETI-03-04

J.L.Huertas

Organización de ARM con pipeline de 3 etapas

·

·

·

·

·

·

·

Un banco de registros

Un desplazador/rotador (barrel

shifter)

Una ALU

Registro de direcciones e increm.

Registros de datos

Decodificador de instrucciones

Lógica de control

Tr. 328

SETI-03-04

J.L.Huertas

Organización de ARM con pipeline de 5 etapas

Tr. 329

J.L.Huertas

SETI-03-04

Actividad de una instrucción de procesamiento de datos

Tr. 330

SETI-03-04

J.L.Huertas

Actividad de una instrucción de almacenamiento

Tr. 331

SETI-03-04

J.L.Huertas

Los dos primeros ciclos de actividad de una instrucción de salto

Tr. 332

SETI-03-04

J.L.Huertas

Ejemplo: ARM7100

Tr. 333

SETI-03-04

J.L.Huertas

Ejemplo: ARM7500 en un sistema

Proceso: 0,6 µm

Transistores: 550.000

Niveles de metalización: 2

Area: 70 mm2

MIPs: 30

Potencia: 690 mW

VDD: 5 V

MIPs/W: 43

Reloj: 33 MHz

Tr. 334

SETI-03-04

J.L.Huertas

Ejemplo: SA-1100

Proceso: 0,35 µm

Transistores: 2.500.000

Niveles de metalización: 32

Area: 75 mm2

Potencia: 330/550 mW MIPs: 220/250

VDD: 1,5/2 V

MIPs/W: 665/450

Reloj: 190/220 MHz

Tr. 335

SETI-03-04

J.L.Huertas

Ejemplo: LEON e implementaciones

Tr. 336

SETI-03-04

J.L.Huertas

Evolución actual y en el futuro cercano

Tr. 337

SETI-03-04

J.L.Huertas

Evolución actual y en el futuro cercano

Tr. 338

J.L.Huertas

SETI-03-04

Tr. 339

SETI-03-04

J.L.Huertas

Evolución actual y en el futuro cercano

Tr. 340

SETI-03-04

J.L.Huertas

Proceso: 0,25 µm

Transistores: 110.000

Niveles de metalización: 3

Area: 2,1 mm 2

Potencia: 150 mW

VDD: 2,5 V

Reloj: 200 MHz

MIPs: 220

MIPs/W: 1500

Tr. 341