INTRODUCCIÓN A SISTEMAS EMBEBIDOS, VHDL, ISE (XILINX

Anuncio

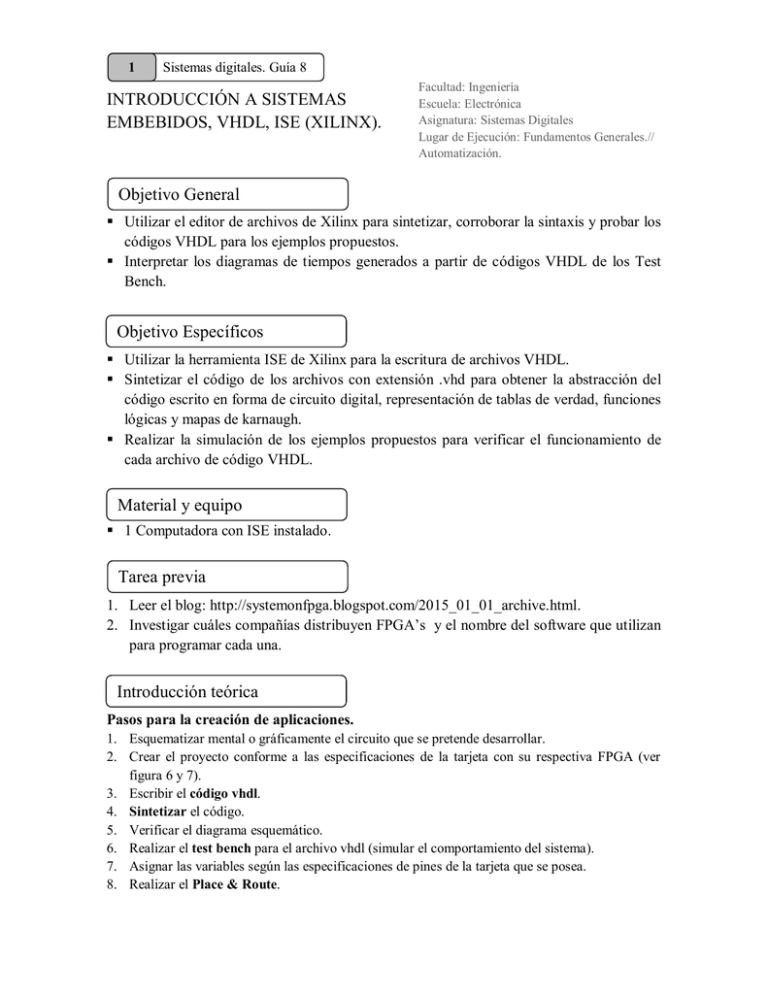

1 Sistemas digitales. Guía 8 INTRODUCCIÓN A SISTEMAS EMBEBIDOS, VHDL, ISE (XILINX). Facultad: Ingeniería Escuela: Electrónica Asignatura: Sistemas Digitales Lugar de Ejecución: Fundamentos Generales.// Automatización. Objetivo General Utilizar el editor de archivos de Xilinx para sintetizar, corroborar la sintaxis y probar los códigos VHDL para los ejemplos propuestos. Interpretar los diagramas de tiempos generados a partir de códigos VHDL de los Test Bench. Objetivo Específicos Utilizar la herramienta ISE de Xilinx para la escritura de archivos VHDL. Sintetizar el código de los archivos con extensión .vhd para obtener la abstracción del código escrito en forma de circuito digital, representación de tablas de verdad, funciones lógicas y mapas de karnaugh. Realizar la simulación de los ejemplos propuestos para verificar el funcionamiento de cada archivo de código VHDL. Material y equipo 1 Computadora con ISE instalado. Tarea previa 1. Leer el blog: http://systemonfpga.blogspot.com/2015_01_01_archive.html. 2. Investigar cuáles compañías distribuyen FPGA’s y el nombre del software que utilizan para programar cada una. Introducción teórica Pasos para la creación de aplicaciones. 1. Esquematizar mental o gráficamente el circuito que se pretende desarrollar. 2. Crear el proyecto conforme a las especificaciones de la tarjeta con su respectiva FPGA (ver figura 6 y 7). 3. Escribir el código vhdl. 4. Sintetizar el código. 5. Verificar el diagrama esquemático. 6. Realizar el test bench para el archivo vhdl (simular el comportamiento del sistema). 7. Asignar las variables según las especificaciones de pines de la tarjeta que se posea. 8. Realizar el Place & Route. Sistemas digitales. Guía 8 2 9. Generar el Programming File. 10. Descargar el archivo con extensión .bit sobre la FPGA. 11. Realizar las pruebas de funcionamiento. Procedimiento Parte I: Creación de proyectos con ISE y Spartan-6 LX9 CSG324. 1) La primera aplicación es realizar el código VHDL para sintetizar el funcionamiento de 3 compuertas básicas, ver figura 1. Figura 1: Circuito a generar con el VHDL. a) Iniciar el software ISE. 2) Dé doble clic en el archivo de script de ISE en el escritorio con la imagen 3) Seleccione la opción Ejecutar. . b) Creación de un Proyecto en ISE. 4) En la barra de menús seleccione File/New Project. Aparecerá la ventana de opciones de un nuevo proyecto (New Project Wizard), ver figura 2. 5) Introduzca el nombre del ejercicio de laboratorio, y navegue para encontrar el directorio ya creado o cree uno, como se muestra en la figura 2 y seleccione tipo HDL desde la opción TopLevel Source Type y presione el botón Next, lo cual desplegará la ventana de la figura 3. Figura 2: Creación de un nuevo proyecto, pasos 4) y 5). 3 Sistemas digitales. Guía 8 6) Seleccione las opciones de la figura 3 (conforme a la tarjeta sobre la que desarrollará la aplicación, acorde al hardware real sobre el cual se descargará la síntesis del circuito) y luego presione el botón Next lo que desplegará la ventana de la figura 4. Property Name Family Device Package Speed Preferred language VHDL Source Analysis Standard Value Spartan6 XC6SLX9 CSG324 -2 VHDL VHDL-200X Figura 3: Creación de nuevo proyecto, paso 6). Figura 4: Configuración de nuevo proyecto, paso 6). Sistemas digitales. Guía 8 4 7) Presione el botón Finish para crear el proyecto. c) Creación de archivo VHDL (Very High Speed Integrated Circuit Hardware Description Language). 8) Dé clic derecho sobre la segunda línea (xc6slx9-2csg324) del cuadro superior izquierdo de la ventana de navegación del proyecto (figura 5). 9) Elija la opción New Source… Figura 5: Creación de archivos, pasos 8) y 9). 10) En la ventana New Source Wizard, seleccione la opción VHDL Module, colóquele un nombre al archivo en el campo File Name:, este será el nombre que adopte la entidad dentro de nuestro bloque o circuito a describir, verifique que el check box Add to Project esté activo y dé clic en el botón Next tal como lo indica la figura 6. Figura 6: Creación de archivos, paso 10). 5 Sistemas digitales. Guía 8 11) Como puede observar en la figura 7 ya aparece el nombre de la entidad, coloque en las filas los nombres de las variables de entrada (a, b) y salida (x, y, z) de su sistema, así como la longitud de los vectores o buses a utilizar (considerando que la posición 0 cuenta como valor) para este caso son bits individuales, por lo que no se especificará nada adicional. Con la lista desplegable elija la dirección del flujo de datos (in, out o inout) tal como lo indica la figura 7 y dé clic en el botón Next. Figura 7: Creación de archivos, paso 11), elección de entradas y salidas del componente. 12) La figura 8 muestra un breve resumen de los atributos seleccionados en la creación del modulo VHDL. Dé clic izquierdo en el botón Finish. Figura 8: Creación de archivos, paso 12). 13) Se mostrará en el editor de código VHDL de ISE, en dicha ventana modifique el código VHDL para que se vea igual al mostrado a continuación (Código 1): Sistemas digitales. Guía 8 library IEEE; --Uso de Librería IEEE use IEEE.STD_LOGIC_1164.ALL; entity SDI111_G1_EJ1 is Port ( a : in STD_LOGIC; b : in STD_LOGIC; x : out STD_LOGIC; y : out STD_LOGIC; z : out STD_LOGIC); end SDI111_G1_EJ1; 6 --Estándares lógicos de la Librería IEEE --Nombre de la entidad --Declaración de variables a, b --como entradas --Declaración de variables x, y, z --como salidas --Finalización de la entidad architecture Behavioral of SDI111_G1_EJ1 is --Descripción del comportamiento de la begin --entidad x <= a or b; --Compuerta or con entradas a y b, salida x y <= a and b; --Compuerta and con entradas a y b, salida y z <= a xor b; --Compuerta exor con entradas a y b, salida z end Behavioral; --Finalización del comportamiento Código 1: Código VHDL, archivo SDI111_G1_EJ1.vhd, paso 13). d) Sintetizar el código. Este proceso permite: Verificar la sintaxis del código VHDL escrito. La conversión del código VHDL a un circuito digital equivalente ya sea a LUT’s o circuitos MSI. Abrir una vista del circuito digital equivalente al código VHDL escrito. 14) De clic izquierdo sobre el nombre del archivo VHDL debajo de la línea xc6slx9-2csg324, del cuadro superior izquierdo de la ventana de navegación del proyecto (figura 9) para habilitar las funciones de este archivo en el cuadro inferior. 15) En el cuadro inferior izquierdo, de clic derecho sobre la opción Synthetize – XST, elija la opción Run del menú desplegable. Figura 9: Sintetizar código VHDL, pasos 14) y 15). 7 Sistemas digitales. Guía 8 e) Verificar el diagrama esquemático detallado. 16) Dé clic izquierdo sobre el nombre del archivo VHDL debajo de la línea xc6slx9-2csg324, del cuadro superior izquierdo de la ventana de navegación del proyecto (figura 9), para habilitar las funciones de este archivo en el cuadro inferior. 17) De doble clic izquierdo sobre la opción View Technology Schematic, ver figura 10. Figura 10: Verificar el diagrama esquemático detallado, paso 17). 18) Dé clic izquierdo en el botón OK de la figura 11. Figura 11: Verificar el diagrama esquemático detallado, paso 18). 19) En la ventana desplegable dé clic en el botón Add -> y luego el botón Create Schematic (figura 12). Figura 12: Verificar diagrama esquemático simplificado, paso 19). Sistemas digitales. Guía 8 8 20) Dé doble clic izquierdo sobre la caja de dos entradas y tres salidas. 21) Dé doble clic izquierdo sobre cada una de las cajas que tengan la palabra LUT1 incluida y verifique cada una de las opciones. f) Verificar el diagrama esquemático de un circuito complejo (abstracción del diseño): 22) Dé clic izquierdo sobre el nombre del archivo VHDL debajo de la línea xc6slx9-2csg324, del cuadro superior izquierdo de la ventana de navegación del proyecto (figura 9), para habilitar las funciones de este archivo en el cuadro inferior. 23) Dé doble clic izquierdo sobre la opción View RTL Schematic, ver figura 10. 24) En la ventana (figura 13) que se despliegue presione el botón Ok. Figura 13: Verificar diagrama esquemático, paso 24). 25) Dé clic en el botón Add -> y luego el botón Create Schematic (figura 14). 26) Se desplegará una figura de bloque que al hacer doble clic izquierdo sobre la misma mostrará el circuito equivalente al código VHDL. Figura 14: Verificar diagrama esquemático, paso 25). 1 LUT: Look-Up Tables (Tabla de consulta). 9 Sistemas digitales. Guía 8 g) Realizar el test bench para el archivo vhdl (simular el comportamiento del sistema). 27) De clic derecho sobre la segunda línea (xc6slx9-2csg324) del cuadro superior izquierdo de la ventana de navegación del proyecto (figura 5). 28) Elija la opción New Source… 29) En la ventana New Source Wizard, seleccione la opción VHDL Test Bench, colóquele un nombre al archivo en el campo File Name:, la extensión del archivo será .vhd al igual que al archivo del código fuente en VHDL por lo que si escribe el mismo nombre para el test bench estará intentando sobre escribir el código VHDL, por lo que se recomienda agregar _tb al final del nombre del archivo del test bench para diferenciarlo del código VHDL. 30) Verifique que el check box Add to Project este activo y de clic en el botón Next tal como lo indica la figura 15. Figura 15: Creación de archivo test bench, pasos 29) y 30). 31) De clic izquierdo en el botón Next -> de la figura 16. 32) Para finalizar de clic izquierdo en el botón Finish -> de la figura 17. Figura 16: Creación de archivo test bench, paso 31). Sistemas digitales. Guía 8 10 Figura 17: Creación de archivo test bench, paso 32). 33) Comente o elimine las partes referidas al clock porque el circuito de la figura 7 no utiliza el reloj. De tal manera que el código VHDL del Test Bench se vea como el siguiente: LIBRARY ieee; USE ieee.std_logic_1164.ALL; ENTITY SDI111_G1_EJ1_tb IS END SDI111_G1_EJ1_tb; ARCHITECTURE behavior OF SDI111_G1_EJ1_tb IS -- Component Declaration for the Unit Under Test (UUT) COMPONENT SDI111_G1_EJ1 PORT( a : IN std_logic; b : IN std_logic; x : OUT std_logic; y : OUT std_logic; z : OUT std_logic ); END COMPONENT; --Inputs signal a : std_logic := '0'; signal b : std_logic := '0'; --Outputs signal x : std_logic; signal y : std_logic; signal z : std_logic; BEGIN -- Instantiate the Unit Under Test (UUT) uut: SDI111_G1_EJ1 PORT MAP ( a => a, b => b, x => x, y => y, z => z ); 11 Sistemas digitales. Guía 8 -- Stimulus process stim_proc: process begin -- hold reset state for 10 ns. wait for 10 ns; -- insert stimulus here a <= '0'; b <= '0'; wait for 10 ns; a <= '0'; b <= '1'; wait for 10 ns; a <= '1'; b <= '0'; wait for 10 ns; a <= '1'; b <= '1'; wait for 10 ns; wait; end process; END; Código 2: Código VHDL del Test Bench, archivo SDI111_G1_EJ1_tb.vhd, paso 33). 34) De clic izquierdo en el botón de opción Simulation en el cuadro superior izquierdo. 35) Seleccione el nombre del archivo del test bench: SDI111_G1_EJ1_tb.vhd (este es el nombre del ejemplo que se está realizando) tal como lo indica la figura 18. 36) Luego en el cuadro inferior izquierdo de clic derecho sobre la opción Behavioral Check Syntax y elija la opción Run tal como se muestra en la figura 18. Si usted no ha guardado el archivo antes de correr esta opción le pedirá guardar el archivo del test bench tal como se indica en la figura 19 a lo que deberá contestar en el botón Yes. Figura 18: Creación de archivo test bench, pasos 34) al 36). Sistemas digitales. Guía 8 12 Figura 19: Creación de archivo test bench, paso 36). 37) En el cuadro inferior izquierdo de clic derecho sobre la opción Simulate Behavioral Model y elija la opción Process Properties… Esto abrirá una ventana en la que fijaremos el valor de Simulation Run Time a 50 ns, tal como se indica en la figura 20. Figura 20: Asignación de tiempo a simular en el Test Bench, paso 37). 38) En el cuadro inferior izquierdo de clic derecho sobre la opción Simulate Behavioral Model y elija la opción Run. Esto abrirá el software Isim donde podrá corroborar las respuestas en el diagrama de tiempos de la figura 21. 39) De clic en el icono Zoom to Full View y verifique que a medida que las entradas (a, b) toman valores cada 10 ns las salidas obtienen el valor correspondiente a la tabla de verdad de las compuertas programadas en las variables x, y, z. Figura 21: Creación de archivo test bench, paso 39). Parte II: Realización de ejemplos guiados. 40) Repita los pasos del 1 al 39 para los siguientes ejemplos. 13 Sistemas digitales. Guía 8 h) Función lógica. 4 F= 1,3,5,7,9,11,13,14,15 = d ab + c + abc abcd Figura 22: Función lógica, ejemplo 2. Figura 23: Declaración de variables, Función lógica, ejemplo 2. library IEEE; use IEEE.STD_LOGIC_1164.ALL; entity SDI111_G1_EJ2 is Port (a, b, c, d: in std_logic; F: out std_logic); end SDI_G1_EJ2; architecture Behavioral of SDI_G1_EJ2 is begin F <= (d and (not(a and b) or not(c))) or ((a and b) and c); end Behavioral; Código 3: Código VHDL, archivo SDI111_G1_EJ2.vhd, ejemplo 2. 41) Verifique la expresión, tabla de verdad, mapa de Karnaugh y circuito esperado con la herramienta de ISE, pasos 16 al 21. library IEEE; use IEEE.STD_LOGIC_1164.ALL; entity SDI111_G1_EJ2_tb is end SDI_G1_EJ2_tb; Sistemas digitales. Guía 8 ARCHITECTURE behavior OF SDI111_G1_EJ2_tb IS -- Component Declaration for the Unit Under Test (UUT) COMPONENT SDI111_G1_EJ2 PORT( a : IN std_logic; b : IN std_logic; c : IN std_logic; d : IN std_logic; F : OUT std_logic ); END COMPONENT; --Inputs signal a : std_logic := '0'; signal b : std_logic := '0'; signal c : std_logic := '0'; signal d : std_logic := '0'; --Outputs signal F : std_logic; BEGIN -- Instantiate the Unit Under Test (UUT) uut: SDI111_G1_EJ2 PORT MAP ( a => a, b => b, c => c, d => d, F => F ); -- Stimulus process stim_proc: process begin -- hold reset state for 10 ns. wait for 10 ns; -- insert stimulus here a <= '0'; b <= '0'; c <= '0'; d <= '0'; wait for 10 ns; a <= '0'; b <= '0'; c <= '0'; d <= '1'; wait for 10 ns; a <= '0'; b <= '0'; c <= '1'; d <= '0'; wait for 10 ns; a <= '0'; b <= '0'; c <= '1'; d <= '1'; wait for 10 ns; a <= '0'; b <= '1'; c <= '0'; d <= '0'; 14 15 Sistemas digitales. Guía 8 wait for 10 ns; a <= '0'; b <= '1'; c <= '0'; d <= '1'; wait for 10 ns; a <= '0'; b <= '1'; c <= '1'; d <= '0'; wait for 10 ns; a <= '0'; b <= '1'; c <= '1'; d <= '1'; wait for 10 ns; a <= '1'; b <= '0'; c <= '0'; d <= '0'; wait for 10 ns; a <= '1'; b <= '0'; c <= '0'; d <= '1'; wait for 10 ns; a <= '1'; b <= '0'; c <= '1'; d <= '0'; wait for 10 ns; a <= '1'; b <= '0'; c <= '1'; d <= '1'; wait for 10 ns; a <= '1'; b <= '1'; c <= '0'; d <= '0'; wait for 10 ns; a <= '1'; b <= '1'; c <= '0'; d <= '1'; wait for 10 ns; a <= '1'; b <= '1'; c <= '1'; d <= '0'; wait for 10 ns; a <= '1'; b <= '1'; c <= '1'; d <= '1'; wait for 10 ns; wait; end process; END; Código 4: Código VHDL del Test Bench, archivo SDI111_G1_EJ2_tb.vhd, ejemplo 2. Sistemas digitales. Guía 8 Figura 24: Asignación de tiempo a simular en el Test Bench, Función lógica, ejemplo 2. Figura 25: Diagrama de tiempo de funcionamiento del circuito, Función lógica, ejemplo 2. i) Tabla de verdad. Entradas Salidas # A B C D M O 0 0 0 0 0 0 1 1 0 0 0 1 0 1 2 0 0 1 0 0 1 3 0 0 1 1 0 1 4 0 1 0 0 0 0 5 0 1 0 1 1 1 6 0 1 1 0 0 0 7 0 1 1 1 1 1 8 1 0 0 0 0 1 9 1 0 0 1 0 1 10 1 0 1 0 1 1 11 1 0 1 1 1 1 12 1 1 0 0 0 0 13 1 1 0 1 1 1 14 1 1 1 0 1 0 15 1 1 1 1 1 1 Tabla 1: Tabla de verdad del ejemplo SDI111_G1_EJ3.vhd. 16 17 Sistemas digitales. Guía 8 42) Para este ejemplo se considerará que las variables se escribirán como vectores de la siguiente manera: Dirección de Flujo de datos Entrada Entrada Entrada Entrada Salida Salida Variable de la Tabla A B C D M O Variable en el código VHDL Data_In[3] Data_In[2] Data_In[1] Data_In[0] Data_Out[1] Data_Out[0] Tabla 1: Asignación de variables SDI111_G1_EJ3.vhd. Figura 26: Declaración de variables, Tabla de verdad, ejemplo 3. library IEEE; use IEEE.STD_LOGIC_1164.ALL; entity SDI111_G1_EJ3 is Port ( Data_In Data_Out end SDI111_G1_EJ3; : in STD_LOGIC_VECTOR (3 downto 0); : out STD_LOGIC_VECTOR (1 downto 0)); architecture Comportamiento of SDI111_G1_EJ3 is begin with Data_In select Data_Out <= "00" when "0100" | "0110" | "1100", "01" when "0000" | "0001" | "0010" | "0011" | "1000" | "1001", "10" when "1110", "11" when others; end Comportamiento; Código 5: Código VHDL, archivo SDI111_G1_EJ3.vhd, ejemplo 3. 43) Escriba la expresiones del circuito esperado (haciendo uso de mapas de Karnaugh) para la tabla de verdad de SDI111_G1_EJ3. 44) Dibuje el circuito de las expresiones obtenidas en el punto anterior. Sistemas digitales. Guía 8 CD AB 00 00 AB 00 01 11 10 10 1 3 2 4 5 7 6 12 13 15 14 8 9 11 10 10 CD 11 0 01 11 01 00 01 18 11 10 0 1 3 2 4 5 7 6 12 13 15 14 8 9 11 10 45) Verifique los mapas de Karnaugh, expresiones y circuito esperado con la herramienta de ISE, pasos 16 al 21. LIBRARY ieee; USE ieee.std_logic_1164.ALL; ENTITY SDI111_G1_EJ3_tb IS END SDI111_G1_EJ3_tb; ARCHITECTURE behavior OF SDI111_G1_EJ3_tb IS -- Component Declaration for the Unit Under Test (UUT) COMPONENT SDI111_G1_EJ3 PORT( Data_In : IN std_logic_vector(3 downto 0); Data_Out : OUT std_logic_vector(1 downto 0) ); END COMPONENT; --Inputs signal Data_In : std_logic_vector(3 downto 0) := (others => '0'); --Outputs signal Data_Out : std_logic_vector(1 downto 0); BEGIN -- Instantiate the Unit Under Test (UUT) uut: SDI111_G1_EJ3 PORT MAP ( Data_In => Data_In, Data_Out => Data_Out ); -- Stimulus process 19 Sistemas digitales. Guía 8 stim_proc: process begin -- insert stimulus here Data_In <= "0000"; wait for 50 ns; Data_In <= "0001"; wait for 50 ns; Data_In <= "0010"; wait for 50 ns; Data_In <= "0011"; wait for 50 ns; Data_In <= "0100"; wait for 50 ns; Data_In <= "0101"; wait for 50 ns; Data_In <= "0110"; wait for 50 ns; Data_In <= "0111"; wait for 50 ns; Data_In <= "1000"; wait for 50 ns; Data_In <= "1001"; wait for 50 ns; Data_In <= "1010"; wait for 50 ns; Data_In <= "1011"; wait for 50 ns; Data_In <= "1100"; wait for 50 ns; Data_In <= "1101"; wait for 50 ns; Data_In <= "1110"; wait for 50 ns; Data_In <= "1111"; wait for 50 ns; wait; end process; END; Código 6: Código VHDL del Test Bench, archivo SDI111_G1_EJ3_tb.vhd, ejemplo 3. Figura 27: Asignación de tiempo a simular en el Test Bench, Tabla de verdad, ejemplo 3. 1111 𝑀= 1111 5,7,10,11,13,14,15 𝑎𝑏𝑐𝑑 𝑂= 0,1,2,3,5,7,8,9,10,11,13,15 𝑎𝑏𝑐𝑑 Sistemas digitales. Guía 8 20 Figura 28: Diagrama de tiempo de funcionamiento del circuito, Tabla de verdad, ejemplo 3. Bibliografía 1. http://systemonfpga.blogspot.com/2015_01_01_archive.html 2. http://www.xilinx.com/products/boards-and-kits/1-3i2dfk.html 3. All Programmable Low-End Portfolio Product Selection Guide: http://www.xilinx.com/publications/prod_mktg/low-end-portfolio-product-selectionguide.pdf 4. Xilinx® Spartan®-6 FPGA LX9 MicroBoard User Guide: http://opencores.org/websvn,filedetails?repname=openmsp430&path=%2Fopenmsp430 %2Ftrunk%2Ffpga%2Fxilinx_avnet_lx9microbard%2Fdoc%2FXilinx_Spartan6_LX9_MicroBoard_Rev_B2_Hardware_User_Guide.pdf 5. http://www.xilinx.com/products/silicon-devices/fpga/spartan-6.html 6. http://community.em.avnet.com/t5/Spartan-6-LX9-MicroBoard/LX9-PinoutDiagram/td-p/3749 7. TE CONNECTIVITY INTERCONNECT SOLUTIONS FOR THE XILINX® SPARTAN®-6 FPGA LX9 MICROBOARD http://www.em.avnet.com/en-us/design/drc/Documents/Xilinx/TE-AES-S6MB-LX9-G13.2-V2.pdf 8. Configuring the Xilinx Spartan - 6 LX9 MicroBoard: http://www.em.avnet.com/Support%20And%20Downloads/Avnet_Spartan6_LX9_MicroBoard_Configuration_Guide_v1_1.pdf 9. Tutorial 1 Creating an AXI – based Embedded System: http://www.eeworld.com.cn/uploadfile/Xilinx/uploadfile/201107/20110712024756897. pdf 10. Spartan-6 Family Overview: http://www.xilinx.com/support/documentation/data_sheets/ds160.pdf 11. Spartan-6 FPGA Data Sheet: DC and Switching Characteristics: http://www.xilinx.com/support/documentation/data_sheets/ds162.pdf 12. Spartan6 Product Brief: http://www.xilinx.com/publications/prod_mktg/Spartan6_Product_Brief.pdf 21 Sistemas digitales. Guía 8 13. Spartan-6 FPGA Packaging and Pinouts: Product Specification: http://www.xilinx.com/support/documentation/user_guides/ug385.pdf 14. Driver (C:\Xilinx\14.7\ISE_DS\common\bin\nt64\digilent): http://forums.xilinx.com/t5/General-Technical-Discussion/xilinx-spartan-6-lx9microboard-ise-driver/m-p/317679#M13784 15. http://xgoogle.xilinx.com/search?output=xml_no_dtd&ie=UTF-8&oe=UTF8&client=support&proxystylesheet=support&site=Answers_Docs&filter=0&resultsVie w=category&tab=sd&num=1000&sortBy=displayOrder&show_dynamic_navigation=1 &sort=date%3AD%3AR%3Ad1&documentClass=Document&requiredfields=Archived%3Atrue&getfields=*&q=+inmeta:Document%2520Type%3DPackage%2520 Specifications+inmeta:Devices%3DSpartan%252D6+inmeta:Document%2520Class%3 DDocument+inmeta:Product%2520Type%3DSilicon%2520Devices&dnavs=inmeta:Do cument%2520Type%3DPackage%2520Specifications+inmeta:Devices%3DSpartan%2 52D6+inmeta:Document%2520Class%3DDocument+inmeta:Product%2520Type%3D Silicon%2520Devices 16. http://xgoogle.xilinx.com/search?output=xml_no_dtd&ie=UTF-8&oe=UTF8&client=support&proxystylesheet=support&site=Answers_Docs&filter=0&resultsVie w=category&tab=sd&num=1000&sortBy=date&show_dynamic_navigation=1&sort=d ate%3AD%3AR%3Ad1&documentClass=Document&requiredfields=Archived%3Atrue&getfields=*&q=+inmeta:Document%2520Type%3DApplication%2 520Notes+inmeta:Devices%3DSpartan%252D6+inmeta:Document%2520Class%3DDo cument+inmeta:Product%2520Type%3DSilicon%2520Devices&dnavs=inmeta:Docum ent%2520Type%3DApplication%2520Notes+inmeta:Devices%3DSpartan%252D6+in meta:Document%2520Class%3DDocument+inmeta:Product%2520Type%3DSilicon% 2520Devices 17. http://www.fpga4fun.com/JTAG.html 18. http://linuxzone.es/crear-lanzadores-dentro-de-los-menus-de-gnome/