Práctica 6. Circuitos Secuenciales I. Ejercicios teóricos

Anuncio

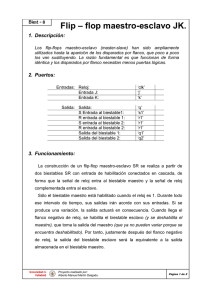

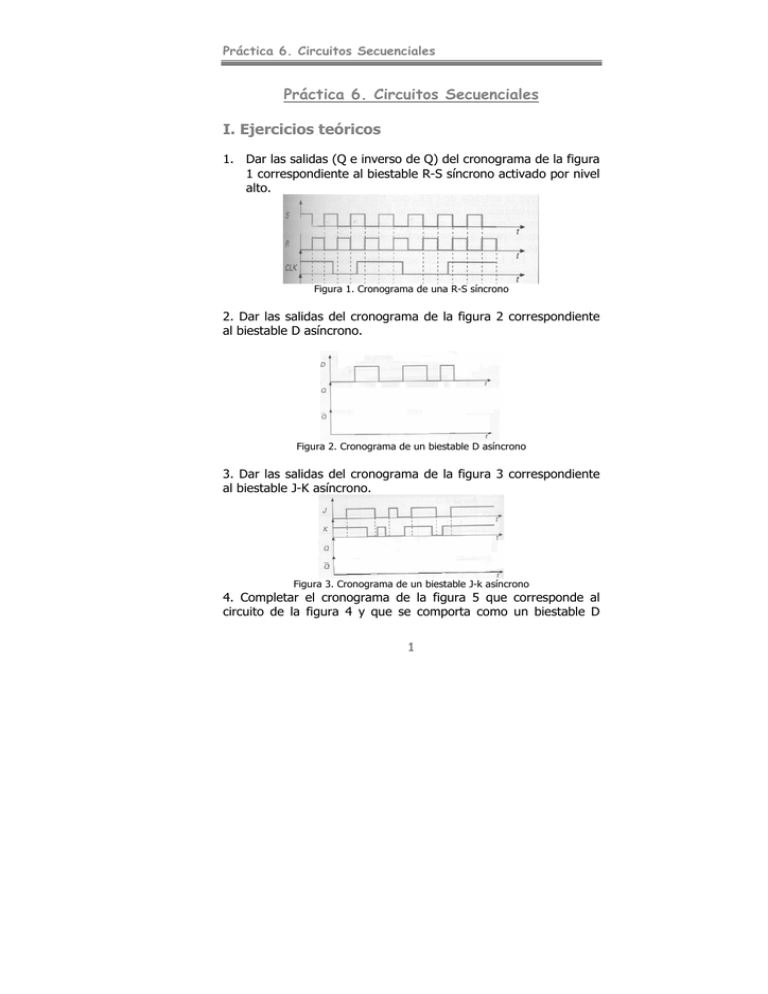

Práctica 6. Circuitos Secuenciales Práctica 6. Circuitos Secuenciales I. Ejercicios teóricos 1. Dar las salidas (Q e inverso de Q) del cronograma de la figura 1 correspondiente al biestable R-S síncrono activado por nivel alto. Figura 1. Cronograma de una R-S síncrono 2. Dar las salidas del cronograma de la figura 2 correspondiente al biestable D asíncrono. Figura 2. Cronograma de un biestable D asíncrono 3. Dar las salidas del cronograma de la figura 3 correspondiente al biestable J-K asíncrono. Figura 3. Cronograma de un biestable J-k asíncrono 4. Completar el cronograma de la figura 5 que corresponde al circuito de la figura 4 y que se comporta como un biestable D 1 Práctica 6. Circuitos Secuenciales realizado con un CI 7476 que no es más que un biestable J-K tipo Master-Slave. Figura 4. Biestable D implementado con un biestable J-K C.I. 7476 Figura 5. Cronograma correspondiente a la figura 4 5. Si a un biestable D del tipo 7474 se le introducen las señales del cronograma siguiente, completar el cronograma obteniendo las señales de salida. Figura 6. Cronograma de funcionamiento del biestable D tipo 7474 6. Dado el siguiente cronograma, que corresponde a un biestable comercial, obtener su tabla de funcionamiento e indicar su función. ¿De qué circuito integrado se trata? Figura 7. Cronograma correspondiente al biestable X-Y 2 Práctica 6. Circuitos Secuenciales 7. Representar el cronograma y tabla de verdad correspondiente a un biestable D activado por nivel bajo. La entrada del clock o reloj es una señal cuadrada con frecuencia y amplitud constante. II. Ejercicios prácticos 1. Dar el diseño lógico, tabla de verdad, cronograma de la figura 8 y montaje del R-S asíncrono con puertas NOR. Figura 8. Cronograma del biestable R-S 2. Dar el diseño lógico, tabla de verdad y montaje del R-S asíncrono con puertas NAND. 3. Dar el diseño lógico, tabla de verdad y montaje del J-K asíncrono con puertas lógicas de la figura 9. Figura 9. Biestable J-K asíncrono con puertas lógicas 4. Dar el diseño lógico, tabla de verdad, cronograma de la figura 1 y montaje de un R-S síncrono activado por nivel alto. 3 Práctica 6. Circuitos Secuenciales Comprobar si el cronograma obtenido coincide con el obtenido en el ejercicio 1 de la parte de ejercicios teóricos. 5. Dar el diseño lógico, tabla de verdad, cronograma de la figura 6 y montaje de un biestable D síncrono activado a nivel alto con puertas lógicas. Comprobar si el cronograma obtenido coincide con el obtenido en el ejercicio 5 de la parte de ejercicios teóricos 6. Dar el diseño lógico, tabla de verdad, cronograma de la figura 10 y montaje de un biestable D síncrono activado por flanco ascendente con puertas lógicas e incluir además para el clock el montaje de un antirrobote. Figura 10. Cronograma del biestable D síncrono 7. Dar el diseño lógico, tabla de verdad y montaje de un biestable J-K sincronizado por flanco maestro-esclavo con puertas lógicas. 8. Montar con el integrado 7474 de la familia TTL el biestable D y dar su tabla de verdad (realizar el montaje del antirrebote para el clock). CLR 1 1 0 1 PR 1 1 1 0 Entradas CLK X X X X D 0 1 X X Salida QT Tabla 1. Tabla de verdad del biestable D 4 Práctica 6. Circuitos Secuenciales 9. Dar el diseño lógico, tabla de verdad y montaje de un J-K sincronizado por flanco de bajada con el circuito integrado 74LS76 (realizar el montaje del antirrebote para el clock). PR CLR 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 0 1 1 0 0 0 Tabla 2. Tabla de Entradas Salidas J K CK QT-1 QT 0 0 0 0 0 1 0 1 0 0 1 1 1 0 0 1 0 1 1 1 0 1 1 1 X X X X X X X X X X X X verdad del biestable J-K sincronizado por flanco 10. Obtener la tabla de verdad del circuito de la figura 11, analizando todos los posibles valores que pueden darse en las entradas X, Y y Qt-1. Comprobar si corresponde a alguno de los biestables que se han estudiado en este tema. Figura 11. Tabla de verdad y esquema lógico del biestable X-Y 5 Práctica 6. Circuitos Secuenciales 11. Montar el biestable de la figura 12 correspondiente a un J-K sincronizado por nivel y dar su tabla de verdad. Tabla 3. Tabla de verdad del biestable J-K Figura 12. Esquema lógico del biestable J-K sincronizado por nivel 12. Suponiendo que la entrada del circuito de la figura 13 se le introducen una serie de impulsos de frecuencia y amplitud constante, realizar el cronograma de tiempos de para cada una de las salidas. Figura 13. Diseño lógico del problema 12. 6 Práctica 6. Circuitos Secuenciales 13.Construir un biestable J-K asíncrono a partir de una báscula R-S con puertas NOR. 7