TP 4. Arquitectura Básica

Anuncio

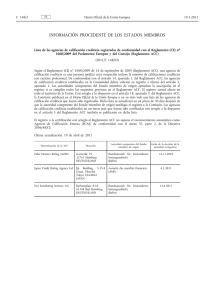

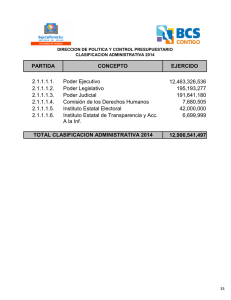

Facultad de Ingeniería. UNJu TP 4 LABORATORIO DE COMPUTADORAS Tema: Arquitectura Apellido y Nombre: LU: Carrera: Fecha: 2013 CONCEPTOS A. Considerando la arquitectura de la computadora sencilla, indique la longitud de sus registros, número de instrucciones, cantidad de palabras de memoria y las microoperaciones que es capaz de realizar. B. Describa el funcionamiento interno de la arquitectura básica o mejorada, e indique todas las microoperaciones que se pueden realizar. Ejemplifique el uso de las microoperaciones ROR y ROL. C. Describa la secuencia de microinstrucciones correspondientes al ciclo de búsqueda de la arquitectura mejorada. ¿Pueden dos instrucciones diferentes tener ciclos de búsqueda distintos? Justifique. D. Consigne y explique el ciclo de instrucción de CSR dirección (llamado subrutina). EJERCICIOS 1. Considerando la arquitectura de la computadora sencilla presentada a continuación: TERMINALES DE LA ARQUITECTURA Registro PC IPC: Incrementar PC. Registro MAR TPC: Transferir PC a MAR TIR: Transferir IR(AD) a MAR Registro IR TB: Transferir bus a IR Memoria E: Habilitar operación sobre memoria R/W!: Leer/Escribir memoria Registro CI W: Escribir CI R: Leer CI C: Complementar CI I: Incrementar CI Registro ACC WA: Escribir ACC RA: Leer ACC Escriba el ciclo de búsqueda y ejecución para Acc0; MM-1, MAcc-3M y AccM-2Acc, indicando en cada caso los terminales de la arquitectura que se activan al ejecutar estas operaciones. UNJU. FACULTAD DE INGENIERÍA Página 1 LABORATORIO DE COMPUTADORAS 2. Considerando la arquitectura de una computadora sencilla, suponga que las siguientes tablas representan el contenido de una porción de memoria y los códigos de instrucción definidos para dicha máquina. Establezca el contenido y significado de cada dirección de memoria y determine qué es lo que se quiere realizar. Suponga que el Acc, inicialmente, vale -4310. Determine el contenido de la posición de memoria 1010112. Dirección de Memoria Contenido de Memoria 000000 01101000 000001 01101010 000010 10101001 000011 11101011 000100 00XXXXXX Código : Instrucción (descripción) 00 Alto 01 Suma al Acc 10 Resta del Acc 11 Transfiere el contenido del Acc a memoria : 101000 01000111 101001 01000100 101010 01100011 101011 XXXXXXXX 3. Suponiendo una arquitectura que posee el siguiente set de instrucciones: Código Instrucción Descripción 000 HLT Detiene el sistema 001 CRA Borra el contenido del acumulador 010 CA Complementa (base -1) el contenido del acumulador 011 INCA Incrementa en 1 el contenido del acumulador 100 ADDM Suma el contenido de un registro de memoria al acumulador 101 STAM Transfiere el contenido del acumulador a un registro de memoria 110 DECA Decrementa en 1 el contenido del acumulador 111 INCM Incrementa en 1 el contenido de un registro de memoria a) Escriba la secuencia de instrucciones apropiada para calcular ACCM1+ACC b) Escriba la secuencia de instrucciones apropiada para calcular ACCM1-M2 c) Escriba la secuencia de instrucciones que ejecute M1M1+ACC-2 d) Escriba la secuencia de instrucciones que ejecute M2 ACC+2*M1 Considere que los registros de memoria M1 ($10) y M2 ($F4) contienen los valores $07 y $C2 respectivamente, y que el acumulador almacena el valor $06. Indique los resultados de cada operación. 4. Considerando el esquema de la arquitectura básica mejorada, complete el siguiente cuadro con las longitudes apropiadas de los registros, de acuerdo a las características arquitectónicas indicadas: Palabras de Memoria Nº de Instrucc. 256 8 512 16 UNJU. FACULTAD DE INGENIERÍA Bits por Palabra PC MAR ACC OPR GPR GPR(OP) GPR(AD) Página 2 LABORATORIO DE COMPUTADORAS Palabras de Memoria Nº de Instrucc. 1024 20 65.536 32 524.288 64 1.048.576 80 Bits por Palabra PC MAR ACC OPR GPR GPR(OP) GPR(AD) 5. Considerando la arquitectura básica, analice la ejecución de las siguientes instrucciones y determine el código de operación de las instrucciones, las posiciones de memoria implicadas en la operación, el tamaño de la memoria direccionable, la longitud de las palabras de memoria y la cantidad de instrucciones de la arquitectura. Además indique el resultado final de cada operación ejecutada. PC Operación Instrucción $020 MM+Acc $100 OPCODE Acumulador F Memoria (M) $122 $011 $1 $020 AccM-Acc $3B0 $25B $0 $010 $A10 AccAcc+F $B77 $833 $1 - $470 MM-1 $781 $019 $0 $F06 $E7F MM-3F $F14 $00A $1 $E03 $220 MAcc-M+4F $250 $10D $1 $642 6. Indique la secuencia de microinstrucciones del ciclo de ejecución de las instrucciones de la arquitectura básica presentadas a continuación. Considere que Q y P son posiciones de memoria: Nº Mnemotécnico Modo de direccionamiento Operación 1 CLRA Implicado Acc’0 2 CLR P Indirecto M’0 3 ADMF Q Directo Acc’Acc+M+F 4 SUBA P Indirecto Acc’Acc-M-1 5 INCA Implicado Acc’Acc+1 6 INC Q Directo M’M+1 7 SUBA Indirecto Acc’Acc-M 8 COMA Implicado Acc’ Acc 9 NEGA Implicado Acc’0-Acc 10 NEG P Indirecto M’0-M 11 DECA Implicado Acc’Acc-1 12 DEC Q Directo M’M-1 13 LDAA P Indirecto Acc’M 14 STAA Q Directo M’Acc 15 SUBFA P Directo Acc’M-(Acc+F) 16 M5A Indirecto M’5Acc 17 OP1 Implicado Acc’F UNJU. FACULTAD DE INGENIERÍA Página 3 LABORATORIO DE COMPUTADORAS Nº Mnemotécnico Modo de direccionamiento Operación 18 OP2 Implicado F1 19 OP3 Implicado Acc’$F 20 OP4 Q Directo M’3M+1 21 OP5 P Indirecto M’Acc-𝐹 22 OP6 Q Directo M’3Acc/4-F 23 OP7 P Indirecto M’M/4+2F 24 OP8 Q Directo M’5Acc-M/2-F 25 ROR Q Indirecto 26 LSR P Directo 27 ASL Q Indirecto 28 ROL Q Directo 29 ASR P Indirecto 30 ASL Q Directo UNJU. FACULTAD DE INGENIERÍA Página 4 LABORATORIO DE COMPUTADORAS ARQUITECTURA BÁSICA PC + 1 PC GPR(AD) PC Contador de Programa (PC) 8 bits 8 R (Leer) M GPR 8 M Memoria 12 bits 8 PC GPR(AD) MAR MAR Registro de Dirección de Memoria (MAR) 8 bits W (EScribir) GPR M 8 12 M 8 GPR(OP) OPR Registro de Operación (OPR) 4 bits 12 bits Registro de Propósito General (GPR) 4 GRP ACC GPR PC GPR (AD) GPR + 1 4 12 GPR 12 Z Sumador 12 bits Controlador F ... GPR + ACC Salidas a los terminales de control de todos los registros, memoria y ALU 0 F 0 F F F Registro Acumulador 12 bits ACC ACC ROR F ACC ROL F ACC ACC ACC + 1 ACC ACC UNJU. FACULTAD DE INGENIERÍA Página 5