. REPORTE DE PWOYECTCJ TERMINAL I

Anuncio

.

REPORTE

DE

PWOYECTCJ TERMINAL I

I

Universidad Autonoma: *tropo¿ i tuna

-

2ztcrpaLapa

Departamento de Ingeniaria EZdctrica

Areu de Ingenieria ELcPctrdniccr

Seminario de Proyectos

1,

Asesor de proyec to

Ing.

I :

Febrero de

I-

Mdxico D. F.

Sergio Pcupz Rodea

I

2

-..

4

s

I

AGRADECIMIENTOS

4 r a d e s c o eL apoyo deL ing. S e r g i o Paez Fadea,

de manera especial el apoyo i n c o n d i c i o n a l y

m L g o Josd Ma.

Lu

así

mismo

agradcrsco

p a c ~ e n c i c ! de

mi

Dorningez G.

Agradesco eL apoyo brLndado por m i s c o d e r o s y amigos Jorge

Meza y Roberto Montoya C .

etapa.

gran

e72

Los

momentos

criticos

de

esta

VeLez

primera

\

f

-._

6

Introduccidn

CcyrjtuLo I

E1 microprocessador

8031

7

1.1

Vista genera¿ de La arquitactura d e 1 8051

I. 2

Arquitectura deL CPW

I. 3

iunciones ferifericas

7

805r

7

9

1.4 Sistema de Interrupciones

10

I. 5

Capacidades de E n t r a W S a l i d a

11

I. 6

Pines de entrada/saLida de drenaje abierto

X3

r . 7 Pines de entrada/saLida CwrsidireccionaLes

13

r . 8 Bus de microprocesadur

13

r . 9 Contadores de liempo/Eventos

14

CajAtuLo 1 1

16

Comunicacidn Serial

I

2.x El rnicroprocesador -5r

2.2 Modos

y su comunicacidn serial

de Operacidn de puerto seria2

rd

18

2.3 Cotnunicacidn Muttiprocesador

30

a . 4 Registro de control d e 1 puerto serial

ai

2 . 5 Baud Rate

32

a . 5 . r Uso deL

temporizudor/contador de eventos una

conw generador de baud rate

33

I

-..

2.6 interface RS-as

2.7 Consideraciones

2.8

*3

UL

Software de soporte

L a íBM PC y su comunicacidn asincrona

a6

a8

2.8. I Adaptador de comunicacich Asincrone

2.8.2

de la IBM PC

a8

Consideraciones al Software de soporte

99

RasuL tados y c o w Lysiones

B i b 1 iugraf C a

ApeFndicas

..

1

I

,

4

-..

1

bntro

del

avance

tecnotcjgico

moderno,

electrdnica se han visto en constante

los

desarroiLo,

L

considerable at c"p0 conyrutacionaZ y de

los microprocesadurss han revolucionado

camps

de

afectando

procesaninto

forma

7

de, informaci¿n.

drew

distintas

la

cow

quehacer

del

humano, permitiendo con ello un mejor aprovechamiento de Los recursos

de su dirtribucidn, liberando

b&re

al

de

repetitivas

y

complej*as

y

~

tareas, consiguiendo con e220 en la mayoria de los casos un producto

m~ej'orcalidad,

-

Algunos de

de

en un menor tiempo y costo.

Los

mTrocesadores

control, tal es eL caso de

la

ftzcultudes que le permiten

desarrollar

hcrn

fmilia

sido

orientados

8 0 5 ~ . la

sistemas

tiam

cual

de

hcrcia

el

amplias

crplicc~~idn,para

encargarse de tareas dirigddas hcrcia la crdministracich de los recursos.

El objetivo del presente reporte es la investigacidn y

de la

comunicacidn

entre

una

--

. '-

microconyiutadora

mi crocontro Ldor &sr.

construccidn

_-_-_------personal CPC)

y

el

.

-----------------....--

- _

w-

Para

alcanzar

el

objetivo

--

antes

mencionad^,

es

necesaria

t m p t o n r o n t a c i d n cie La u~quitectur.ae i e ~microcontrotador -9.

___

-

-

6

ES por el10

--._

--_

.

que se comeward por discribirlo, para posteriormente lograr

perseguido.

la

el

enlace

-..

En un enscywutado de Sitice, el microcornputador

no

cuatro Kilobytes de memoria

treinta

i

y

dos

' Eventos/Te-riaador

Zinears

de

CPW,

de

memoria

RAM,

bytes

dos

EntrWSalida,

estructura

y

ser iat ,

Entrada/Sal ida

de

r28

china

de diecisdis bits, cinco fuentes de

de nivel de prioridad dos,

puerto

volatil,

805.r

de

m

contadores

interrupciones

interrupciones

a

multiprocesadores, expasidn de €ntrcrdcr/Srrlida, o

de

anidadas,

comunicacith

FulL-Dupplex

entre

UART

y

circuitos de r e l o j contruidos c o n un oscilador.

I . ;z

EL CPW

ARWiTECTURA DEL CPU 8 0 5 r

805.r morniputa operandos en cuatro espacios de memoria, estos

1

son

:

- La

- La

I

memoria de sesenta y cuatro Kilobytes

memoria de datos externa de sesenta y cuatro Kiiobytes

- L a memoria de datos interna de trecientos ochenta y cuatro

bytes y

- Un contador

de prograna de diecisdis bits

7

El espacio de direccioncuniento para la

nlemoria de

&tos

estd

interna

dividido en docientos cincuenita y seis bytes de R A M de &tos

interna y

u n bloque de registros de funcidn especial SFR <Special Function Register).

El 8op proporciona un espacio de

direccionamiento

programu paro acomdar cddigo r e l o c a l i d l e . Brincos

nrrenmria

de

de

son

condicionales

ejecutados y son relativos al contador de progrwna. El salto por registro

c o n respscto,a un registro

indirecto permite brincar relativ-nte

d e diecis&s

bits dentro de u n

indice de ocho

bits.

Saltos

offset

de

proporcionado

diecis&s

cualquier LocaLidad de Los sesenta y

bits

por

permiten

Kito&ytes

cuatro

un

de

base

registro

brincar

a

de

espacio

‘direccionouniento para w m o r i a de programus contiguos.

El -5r

tiene cinco dtodos para direccionar operandos fuente :

Modo registro

M

o

directo

Modo registro indirecto

M o d o inmediato y

Modo registro base mbs direccionamiento indirecto de registro indexado

Los primeros tres modos pueden ser usados para direccionur el destino de

los

operandos.

ia

mayoria

de

?fusnte/destino que especifica el

las

t i p

kperandos i n v o l u c r d s . ios registros

iregistros, pueden

ser

crccesados

por

intrucciones

de

en

un

direccionamiento,

tos

medio

cuatro

del

kegistro directo, o registro indirecto, los ciento

8

tienen

bancos

caap

&to

y/o

de

ocho

direccionauioiento

veitiocho

bytes

de

de

.

I

. ,

'5

-._

R A M tie datos internos pueden ser direccioturdos de la m i s m a forma, y

los

registros de función especial CSFRJ a t r d s del direccioncuniento directo

unicamen te.

La memoria de

datos

es

externa

uccesada

micamente

del

atrads

d i r a c c i o m i e n t o de registro indirecto.

~t

-51

esta cLasijicado c o w una

dquina de ocho bits,

ya

RUM interno, la RAM y los registros de funct¿n especial, l a

!de un bus de datos externu son

todos

de

ocho

opracines de bits, nibbles, bytes y datos del

bits,

que

ALU

tambien

t i p o doble byte.

el

CrdsRSds

ej'ecutu

Tanbien

'tiene extensas facilidades para transferir bytes.

El uso eficiente de la memoria de

conjunto de instrucciones que

se

programa

constan

de

cuarenta

logra

y

mediante

nueve

de

un

byte

,sencillo,cuarenta y cinco de. dos bytes y diecisiete de tres.

Cuando

usa

un

de

oscilador

doce

HegaHertz,

sesenta

y

cuatro

intrucciones son ejecutadas en un microsegundo y cuarenta y cinco pueden

~

per

ejecutadas

restantes

c&

una

en

CmuL t ipi icacidn

dos

microsegundos.

divisidn)

y

Las

requieren

instrucciones

sdlo

cuatro

microsegundos.

I. 3 F'UNCiONES

En d i c i d n at CPU y

msmoria,

un

PERI FERICAS

sistemu

de

interrupción

y

OVnpLias

1

.

-..

tupacidades de EntradajSalitia &m¿s

& varias funciones perifdricas ron

integradas para liberar al CPU de relpetitivas, y coapticadas tareas, las

cuales son criticas en tiempo, parra permitir el control en

concatenando interfaces del sistema externo. L a s

funciones

integradas en e ¿ chip son dos contadores de dieoiseis bits y

serial. Todo esto traba3.a en

conjunto

para

aumentar

real

tiempo

perifericas

un

puerto

grandemcPnte

La

eficiencia del sistema.

Eventos externos y manipuladores de tiempo rea¿ para los porifdricos

linternos del chip requieren servicio asincrono del CPU para la ejecucidn

I

be

cualquier seccidn particular de caigo. Para atender las

itsincroncrs de estas funciones en u-

ejecucidn de

programa

activiws

normat,

un

sofisticado sistema de interrupcidn de fuente multipEe, con dos nivetes

prioridad anidado es proprcionado. Los rangos de latencia en

*.

respuesta estan entre tres y siete microsegundos cuando se usa un cristal

de doce Megdertz. El 8 0 5 r reconoce peticiones de informacidn de

Yuentes, dos de fuentes externas v i a pines C I N T O e IiWr>,

una

cinco

de

cada

irno de Los contadores internos y una del puerto serial.

Cada

..

vector de interrtqci¿n apunta a una tocaLidad en

.

memoria

del

I

I

-

,

i

-.

’programa

en La cual se encuentra et progrcuñrr de servicio.

1

as

cinco fuentes puede ser asignada a cualguieru cie

interrupciA y

ser independientemente

Cada

LOS dos

w i t &

una

de

nivetes

de

deswilitadu.

o

I

‘Adicionalmente todas 1-

fuentes M i l i t a d u s pueden ser

tierhabititadas en conj’wato, cada

interr-ich

externa

Militadus

es

o

programable

para ser activada p r transición o nivel y es activa cero para

permitir

hacer ‘un or aLambrado c o n varias fuenkes de interrupcidn.

Las interrupciones estan distribuidas de la siguiente manera:

0003H para ínterrupcicjn Externa o

OOOBH para el ContadorAemporizudor o

oox3H paru interrupcidn Externa

x

ooxBH para el Cont&rAenyx>ria&rdor

I

ma3H para el puerto serial y

O O ~ Hpura ContadorAcmporizadur

I,

El

I

003~

puede

5 CAPACIDADES

m r r n ~ j * a sus

r

2

DE EKTRADA/SALíDA

treinta y

dos

lineas

de

Entrada/Salida

individualmente o como cuatro pvertos paralelos de ocho bits. Estos

bl

puerto ceroI el qusrto unoI el puerto

puertos c’broI dos y tres

pueden

tambien

dos

aswngr

puerto cero proporciona la parte b a j a de las

1

y

el

puerto

otras

direcciams

tres.

funciones.

son

Los

EL

muttiplgxadus

-5

con los datos, usado para expander el -51.

El puerto

dos proporcionar l a

I

parte alta de las direcciones cwndo se expande el h51. Los

puerto tres pYeden ser comfigurcrdos

indiuidwrlmsnte

pura

del

pines

proporcionar

entradas externas de p e t i c i h de intarrupcirh, entradas para contadores,

entrada y salida del receptor y transmisor sericrt

y

jxzra

I

I

las.

generur

1

señales de control usadas pura Lectura y

datos externa, E l uso de una

funcidn

escritura

alternativa

puerto tres es hecha automarticamente por el -5x,

configurado como

I.

UM

entrada, ver f i g u r a

en

en

microprocesdor se programa c&

pin.

que&¿

de1

entruda

pin

us

salida

de

i ~ b c r n c i a . Reseteando

al

el

x

6 PINES DE EWRADA/SALIDA DE DRENAJE ABIERTO

drenaje abierto o como una entrada de

estd

la

de

mumoria

en cuanto

Cada pin del puerto cero puede ser configurado c o w

*uno' e n ese

la

alta

pin como

una

entrada

unar

escribiendo

S i u n 'cero' es escrito posteriormente a l

configurado

cow

una

salida

y

mismo

continuamente

un

pin,

drenard

corriente. Reescribiendo e n el pin u n 'uno', este pondra su manejador de

salida en alta impedancia y c o n f i g u r a d el pin corn una entrada.

I.

7 P I E S DE ENTRADA/SAlIDA CUASi DIRECCiONAiES

Los puertos uno, dos y

tres son buffer

cwuidireccionales.

Despues

12

,

--

r

L

F,

.

-..

jde

resetear

programa&

et

microprocesdr

como entra&

cacia

pin

cie

estos

queda

puertos

escribiendo un *uno’ en e2 pin. Si un ‘cero’

,escrito posteriormente, et pin se c o n f i g u r a d como

corriente continuamente. Cualquier pin que es

li>uz

y drenard

salida

configurado

es

conm

salida

serd reconfigurado como wm entrada cuando un *uno’ sea escrito en et pin.

Simuttcuneo a esta ieconfiguracicin

el

manejador

de

salida

dos

puerto cuasidireccionales proporcionad corriente durante

de

et

periodos

de oscilactdn. Ya que la corriente sdlo se proporciona cuando u n bit que

prevLavnente estaba escrito c o n

programado como

UM

‘cero’

esta

a?wra

en

entrada no proporcionad corriente

I.

8

Q

*uno’, u n

una

pin

compuerta

BUS DEL MICROPROCESADUR

La señal Address Latch Enable CAL€> se proporcina para almacenar

la

parte baja de la direccidn e n u n cerrojo <Latch) externo.

ia seña1 habititador de proQrcuna externo CPS€N> se proporciona para

habilitar un dispositivo de memoria externo, hacia el cual el procesador

bnvia datos atravds del puerto cero de l a memoria externa al

procesador

ptmante La iectwra de la memoria c i e progrcuAcr. cuando l a intrvccirjn

es efecutadu el puerto tres autoribzrticaribente genera la señal

FRDJ para M i l i t a r la memoria de &tos

externa y leer et

wx

tie

lectura

dato

atravds

13

-

-

I

I

,

-._

, &t

puerto cero o genere una seaal de escritura CWR) para

idato e n et d i r p s i t i v o de -moria

I

direccich y el &to

la

a

iArsh/Atll que puede & e m

del

final

ciclo

de

Et

externo.

memoria

externa

puerto

el

mornefardor

cargas T i i

cero

puerto

La

emite

un

a dos

o proporcionar corriente

lecto/escritura

cero

de

atrad

él

almacenar

al

regresa

automaticaarsnte a su estado d e alta impedancia y el puerto dos al estado

en que se encontraba antes

del ciclo de

canal C B U S ) .

tiempo del Qccseso a memoria de progrcuilp es de

A

doce HagaHertz el

ncmoreQundos

tiempos requeridos para u n direccionwniento estable y tambien

CPSEN> son

de

aproximadamente

respectivamente. El

ciclo

de

3po

nanosegundos

memoria

de

y

datos

r p

la

y

Los

señal

nanosegundos

externos

un

de

es

microsegunclo y los tiempos de acceso requeridos para el d i r e c c i o m i e n t o

estable y para comondos de lectura y escritura

son

de

aproximudcmente

boo nanosegundos y 350 nanosegundos respectivamente.

I.

E l &5x

g CONiADOES

DE T2€~F'O/€V€NiOS

contiene dos contadores de diecisdis bits para

medicidn

de

tntervatos de tiempo, d i c i c j n de anchos de pulso, contador de eventos y

peneruci¿n de p e t i c i h e s de interrupci¿n periodicas precisus.

+

Cada

uno

al

ser independientemente p r o g r e para operar en formor simiLar

fomporizardor h 4 8 de ocho b i t s el cual tiene un divisor

I

20s

€modo

cero)

programado

como

contador

de

ocho

por

bits,

treinta

o

y

cow

‘teniporizrrdor de intervalo o contador de

dtesiseis

Cmdo

bits

finalmente coma temprizador de intervalo de o contador de

‘recarga autonrrtica

al

momento

de

sobreflujo

uno>

eventos

o

intervato

lo

y

un

e

ser

eventos

de

contador

dos>

que

adicionalmente el contador cero quede ser pregrcwpdo en u n rnodo

divide en un temporizador de

con

Cmodo

Coverflow>

y

tsniporizzador de intervalo de ocho bits.

C u a n d o el. contador o esta e n llbodo tres el

contador. ww

programado e n cualquiera de los modos antes rmirncionados aunque no

encender La bandera de peticidn de interrupcidn. Este modo es

pUe el sobreflu-io e n el contador puede ser

usado

benerador de razdn de transmisidn. Junto

con

pultiples y su

bits,

precisidn

de

diecisdis

como

pulso

modos

sus

los

de

pueda,

usual

ya

para

el

operacidn

contaddres

pueden

I

aansjar muy altas frecuencias de entrada.

Este rango v a de

0.1

EkrgcrHertz a I MegcrHertz C-a

cristal de

a

1.2

02

HegcrHertz) cuando es programado para una entrada que es una

be

doce d e l a frecuencia del oscilador y de cero u un limite superior de

cincuenta a quinientos KiloHertz (para cristal de

1.2

a

13

zuando es progrouncrdo para entradas externas. A m b a s entrudas

divisi&

MegaHertzJ

internas

Pxternas pueden ser conectadas al contador a t r a d s de una segun&

y

fuente

externa para mediciones directas de ancho de pulso.

2

Los contadores

softtare.

bundo e s t e pasa

son

activados

c o n t e r p a w su

o

bajo

el

control

peticidn

&

inperrtyxidn

detenidos

baridora

de

de su cuenta d x i m a a cero €o al

15

vater

de

del

autocarga3.

COWNICACION S E R I A L

EL MICROPROCESADOR &5x

I

L a familia &pudeser

Y SU C O M N I C A C I O N SERIAL

cunta c o n un puerto

de

que

E~truda0SuLidcr serial

dtil para ligar dispositivos p r i f d r i c o s serialmente

asd

como

multiples & 5 x 8 s atraués de protocolos asincronos standart c o n opercrcibn

FuLl+hplex.

El puerto serial

tdien

I

adncrono

modo

un

tiene

1

para

I

1

iexpansibn de lineas de Entada/SarLida

usando

de

registros

corrimiento

CM3S y Til.. Este Hardware de comunicaciones serial ahorra c&igo

¡permite una razdn de transmisidn mucho

mayor

que

¿a

)alcanzuda por software. En respuesta a La peticidn de

que

RON

F.>odria

y

ser

del

interrupcich

p e r t o serial, el CPU tiene unicamente que Leer o escribir el b u f f e r d e l

puerto serial pura el servicio del enlace serial.

asincrows

para

facilitar las comunicaciones c o n dispositivo4 UART standart, tales

como

E l puerto serial

FulL-duppLex

proporciona

modos

limpresoras y terminates C??T, o comvnicuciones con otro 8 0 9 en

sistemas

para

eliminar

nultiprocesador. El receptor esta debidamente buffereado

oi overrun que podria ocurrir si el procesador falla at responder

tnterrupcibn antes que empiece el siguiente w c o C i n i c i o de

a

datos).

la

En

pdos asincronos, el rechazo del bit de inicio faLso es proporcionado en

LCDS

de reoepcidn.

O

P a r a rechaso de rvido, tres

muestras

son

tomadas

1

kerca de¿ centro de cada bit recibido.

C u a n d o se interfacea c o n dispositivos UARi estandar el canal

serial

I

I

l p ~ t s d eser

programcrdo e n modo uno tal

Q U ~transmita

o reciba e n u n

m c o

'de diez bits o prograriMld0 en modo dos o tres, que transmita o reciba

en

f

¡un m c o de once bits.

y un

El marco consiste e n un bit de arranque

de

bit

modos uno y tres, et circuito de temporiracich de r-dn

paro

de

los

en

transmisicin

recibe u n pulso del contador uno cadu ves que u n sobreflujo sucede e n el

contador. La entrada del contador uno puede ser una fuente externa o

UM

1

ldivisidn por doce de ta frecuencia del oscilador. El

modo

autorrecarga

del contador proporciona razones de comunicacidn de ciento

treinta y un mil docientos cincuenta bits por segundo

b inicio

ueintidos

Cincluysndo

y bits de puro> pura u n cristal de doce Hegdiertz.

dos la ras&

de comunicacdn es una division por sesenta

frecuencia del oscilaüor produciendo una

pchenta y siete mil quinientos bits

inicio y paro) para u n

por

de

cristal

segundo

doce

Fiistribuido ofrece u n sistema mds rdpido y mds

proporcionado con un simple

CPW.

Esto

de

entrada

y

bicroprocesador Spsr Cmorerstro)

salida.

controla

su

ER

una

IonfiQUrados para t r d a j a r simuttaneaurrente e n

mogrQñbeL, c&

:nterconecta&s

uno controlando U M

potente

resulta

Drocesadores interconectables, cada uno con

bropios puertos

El

el

de

UM

propia

modo

y cuatro de

<incluyendo

MegcrHertz.

bits

En el

r d n de transmisith de

la

ciento

bits

de

procesamiento

que

cry&

ser

jerarqda

memoria

y

multiprocescmiento

ñcultiplicidad

porciones

a

de

de

spls

un

805~'s

separadas

&L

porcidn del proceso t o t a l . Los - 5 ~ ' s

reducen l a carga del procesador anfitrtin, rciiisultando u n

17

I

.

'I

-..

jsistema

de

bajo

costo

trunsmisicjn .de datos.

para

Esta

forma

de

I

donde

'procesamientodistribuido es especificamente efectivo en sistemas

el control en un proceso complejo se requiere

en

diferentes

de

areas

msnroria.

En

modos dos

esclaves

atrds

manejado

por

y

tres

del

el

reconocimiento

es

interrupcidn

c o m u n i cac i dn i n t srprocesador

€1

despertador

del

automatico

de

inarco

proporcionado

de

procesadores

direccionamiento

pura

facilitar

LO

.

puerto serial recibe y t r a n s m i t e atraw&

de un registro localizado

en el bloque de registros de funcidn especial C S F m , y

Escribiendo en este registro, se carga el

registro

demoninado

de

SBUF.

transmisidn,

y

Leyendo de este CSBUFD se accesa un registro separado fisicavloente.

2.2

I

EEODUS DE OPERACION DEL PUERTO S E R I A L

E l puerto serie puede operar en cuatro

diferentes

nwdalidades

que

son :

mlD0

CERO.

:

Los

datos

entran

y

salen

sincronizados mediante el -yo

atrads

de

RXD

y

TXD

de una señal de reloj,

Ocho bits son t r a n s m i t i d o s o recibidos, es decir, ocho

bits de datos CiSB primero).

El baud rate es f i l o a un

doceavo de La frecuencia del oscilcrdor.

EfoDs

U . .: Diez bits son transmitidos Catrads de TXD3

o

recibidos

18

I

Y

r

-5

de RXD>

<o>, ocho

un bit de inicio

bits

de

Para

La

recepcidn, eL bit de paro queda dentro del bit R00 e n

eL

Catrat&

:

datos CLSB primero>, y

rsgi.r.tro de

un

bit

de

especia¿ %O¡+.

funci¿n

Cr).

paro

batid

EL

rats

es

var i ab ¿ e.

mm

Dios : Once bits son transmitidos C a t r d s de

C a t r a d s de

:

RDX)

un bit de inicio Co>,

ocho

u n noveno bit de datos

datos CLSB primero),

y un bit de parro

TXD> o

(I>.

recibidos

de

bits

progromrable,

wwno

Para La trarvhisibn, e ¿

bit

de datos CT88 en el registro SCOND pude ser puesto a cero

o a uno. T d i e n , por ejempLo, el bit & paridad CP en el

registro PSWD puede ser enviado a el

TB8,

bit

Para

La

RB8

recepcibn, el noveno bit de datos se carga en et bit

dentro del registro de funcidn especial SCON, mientras et

bit de paro es ignorado.

por

Los

valores

1/32

EL

baud

o' r / 6 4

rate

de

La

programabte

es

frecuencia

del

osci Lador.

MODO TUES : Once bit son transmitidos Catravds de TXD>

C a t r a d s de RXD>

:

u n bit de inicio Co),

o

ocho

datos CLSB primero), u n novena bit de datos

y un bit de puro Cr).

que

el

dos

ntodo

recibidos

bits

de

programuble

De hecho eL modo tres es el

mismo

la

unica

en

todos

Los

aspectos,

diferencia es que e n este modo el baud rate es variable.

19

.

-..

in Los

1

I

cuatro

modos,

La

instruccidn que usa at SBUF

transmisidn

como

registro

es

por

iniciada

destino.

La

es

recepcick

;iniciada en e1 mido cero por tos condicionantes RI igurri a

y

cero

Iigual a uno. La recepcith es i n i c i w en otros modos por la

bit

cualquer

REN

&i

puesta

RE”

LOS

modos

tomunicacieh

dos

y

tres

tienen

multiprocesador.

En

una

estos

previsidn

modos,

el

especial

noveno

para

la

bit

es

heservado. EL noveno bit se coloca en el bit RB8, cuando un bit de

puro

ps

paro

bi t

registrado. El puerto puede ser programado para que el

de

kea reservado, el puerto serial solo padra interrumpir cuavldo el bit UB8

~

S h

frste puesto. L a anterior conducta es habilitada por el bit

Uncr

Pncuentra dentro dol registro de funcidn especial SCON,

que

se

manera

de

I

$titizar esta comunicacidn muttiprocesodor se describe a continuacidn.

Cuando el procesador maestro desea transmitir

un

btoqtte

de

datos

I

m i a alguno de sus escLavos, mancia

bara identificar

h a direccith y

sin ambigüedad

un &to

Q

UM

direccidn

atravis

el esclavo aL que se esta

pueden ser diferenciados

dol

puerto

refiriendo.

por

la

iaracteriaacidn c i e ~nnverto bit, una posible convencich seria ctguoL1a

en

I

a que a1 estar puesto eL n o v ~ n o bit,

omada cotno

MQ

tar

en

el

infor-mncidn

canal

de1

canal

sea

direccidn, de o t r a manera se considerara dato.

F

P

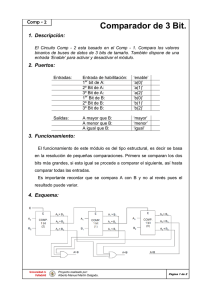

2 . 4 REGISTRO

DE CONTROL DEL WERTO SERIAL

El control del puerto serial asi cotno su status s o n controlados por

I

u n registro de funcidn especial llamado Control Serial

<SON),

que

se

nnsastrtz a continuactch

W D

W B

SYO

dYf

SY2

RPN

TBO

-8

Tí

Rá

I

DONDE SYO Y O Y í W F S C I I I I Q I N

SL MODO DE OCERAQON DXL PUPITO,

COMO S I W E :

SHIFT-IIEaf8'1PII

6-bit UART

*bit

UAIT

BAUD RATE

fosc/f2

variabLo

f omc/64

*bit

fo+c/'lu

variable

YODO DESCRUCTON

SYO

O

O

O

O

1

f

í

O

2

O

1

í

*

sY2

*

RXN

*L

TB8

'

*

*

*

ID8

Tí

Rf

s

UART

Habilita La comunicercidn muLiiproc.na¿or atrovóm ¿e L o s modor

do8 y t-8.

XabiLita La recepción s o r i d .

p u d e mor puosio o Limpiado por

oof tvarea habiLiicu.

Es OL

noveno brt de datos que

pude m o r e n v i d en Loo m o d o s &o

y irom.

p u d e sor manipuLado por s o f t v a r r .

En m o d o r dos y tres e m eL novono

m recibido.

bit que e

D a d a r a de rntorrupcibn de transmiridn

PUO&

borrarme por Softvaro

Bandera do intorrupcibn & rrcopcibn.

~ u o & borrarme por s o f t v a r o

Registro de control del puerto serial CSCON)

21

=

.-

.-

-

-..

2 . 5 BAUD RATES

EL baud r a t e es fijado en el modo cero conw :

WODO

CERO DAUD RATE = Frecuenc iu de Osci t&r

EL baud rate en

modo dos depende

del

/ 12

SPWD

bit

del

valor

en

el

registro tie funcidn especial PCON. Si SMOD es cero Clo cual es almomento

'de reset).

el baud rate ser¿ r/64

J

de la

frecuenciu

del

Si

oscilador.

1

SEfioD es uno, el b a d rate es 1/32 de la frecuencia del oscilador, u s C :

MODO

DOS BAUD RATE =

*

Cos%o~f64>

En l a fandlia w z , el

baud

rate

C lu frecvenc i a del osc i Lador)

en

modos

los

uno

y

tres

es

rdeterrntnacdo por el sobrefZujo en el timer uno.

2 . 5 . I USO DEL T€WORIZAWRfCONTADOR DE EVENTOS U W

COMO

GENERADOR DE BAWD RATE

Cuando et temparizador uno es usado como generador de baud

ras& de transrnisidn Cbaud rate> en Los modus unu y

tres

por el sobre flujo en et temgorizador unu y el valor de

rate,

la

esdeterminado

SHOD,

guedando

s e la siguiente manera :

MODOS UNO Y

TRES

BAUD RATE = C a s u o ~ / p >* Csobref LUJO

El

Ios

del t imer zuzo)

tempriocrdor uno en si mismo puede ser configurado dentro de

formas

de

operaeicfn.

es

decir,

como

'contador'

'temporieatdor', a d como sus tres posibles modalidades.

o

las

como

En la aplicacibn

Ids tJpica, es configurado como temporizador, en

modo

de autorecarga C e s

I

1

bad

;decir la parte a l t a del nibble TpiOD = ooroB3. En tal caso el

rate

esta d c r d ~por ZQsigzliente relactdn :

MODOS UNO Y TRES

BAUD RAlE = C Z S U O P / ~ >

*

C frecuencia t i e l

luego de una descripciOn de to

facultado

pura

realizar,

se

OSC

el

que

procedera

i ador/Cr& o@-Z'iix>

rn5x

microprocesador

a

la

implementacidn

esta

de

La

'arquitectura, tomando e n cuenta Lo anteriormente descrito.

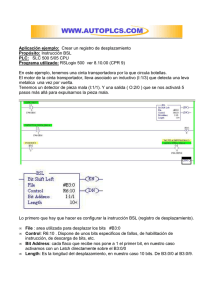

La figura

muestra al microprocesudor &3r,

I,

i h 5 x y que ser¿ utilizudo para ¿a

miembro de la

implementación

de

ta

failia

arquitectura.

Visto de esta manera, el microprocesudor requiere de memoria

externa

y

I

lde

un

latch

externo,

con

objetode

!direccionaniento. La arquitectura

auxiliarlo

definitiva

en

pede

el

de

proceso

observarse

en

la

y

un

I

ijigura 14.

Debe recordarse que para lograx la comunicacidn entre el h 3 x

dispositivo que tenga posibilidades de

comunicacidn

serial,

se

deben

ruidar los estandartes, es decir, Las caractsristicas de los dispositiws

de

comunicaci&.

Las

microcornputadoras

persona¿as

CPC's>,

L ieruen

incluida en su arquitectura,

‘deneminado

m

l

p

,

COYY~~~SXON

RADIO

que

un

estandariecrdo

FRECUPNCY

de

dispositivo

INTERFUEN~

comnicacidn

COYYUNICATIONS

FEDXIAL

en

STAT~YPNT.

serial,

cwnpZe

normas

con

que Le dan caracteristicas peculiares.

Cucndo se habla de Rs-np se esta considerando uno de los estandares

nads untiguos y popuzares. Tipicamente

entre equipes,

como

son

modems,

utiliaado

terminales,

para

la

comunicacich

plot ters.

anal isadores

ldgicos, manejadores de -cintas e impresoras entre otros.

El RS-ep combierte niveles ldgicos mi a niveles

objeto de atcanaar considerables distancias entre los

comunican. Tipicamente la interface

E-2-

que

no lo son, con

sistemas

puede transferir

debajo de

cinco

volts

negativos

hasta

un

a

considera

w’ximo

de

se

informpcih

por c a b l e arriba de cincuenta pies Cr5.24 Efts.> a un maxim0 de

de veinte Kilobits por segundo, para una señal

que

rato

&ia

por

‘u-’

quince

volts

negativos, y a *cero’ como unu seaal de voltaje arriba de cinco volts

y

ion un mhximo de quince volts.

P w a lograr éstos

cambios

de

niveles

de

voltaje

usualmente

requiere del apoyo de dispositivos semiconductores, que se

kstas peculiaridades. Los dispositivos mrfs

I

popularres son el par r4sS

1489, como se muestra en la siguiente figura :

I

encargen

se

de

y

-._

TTL DATA

IN

1/4

14.8

S4’4

+q=,

++= *

TTL DATA

í409

R S 282-C

OUT

+í2v -izv

+8V

...........

+

...........

-

Figura

a.

Circuito

ribdcnejudor

-

y receptor RS-2?p-c

C a b e mencionar que dentro de los estandares que

se

mu~z~jan,estan

sin lvgar u duda los propios niveles licitoc, esto es, tos niveles que se

I

peconoc.rn

dentro . del

marco

establecido,

para

entendar

esta

l=ractsristica, se muestran tos nivetes en la sigvente figvra :

DRXVLR

E f A RS292C/CCXTT

V24-V?0

Signal L A v d o

+f5 Vdc

I

:

Ac ivo/Data

t5 Vdc

+s

=

O

V&

invalid L a v d

@

-5

V&

-5

vdc

xncrttive/mta

I

-55

=

1

Y&

25

c

-

-

L

-..

Es de to anteriormente descrito que se debe consider&

de una interface Rs-acp, para que et microprocesdor

La

construccirfn

ms,

sea capaz

de

'comunicarse con otros dispositivos seriales.

2 . 7 CONSIDERACIOEIES A L SOFTWARE

Lo anterior esta enmcrrcudo e n Lo que

em&argo

pura

que

comvnicucidn

La

a

se

DE SOPORTE

se

Wdwure

efectue

es

'palrticipacidn de et S o f t w e , que avnatgcurrcrdo a su

refiere.

Sin

necesaria!

contraparte

tu

hardware

ipsraitird et estabtecimiento de ta comunicaciljn.

A

continuacidn describire La

de software que permitira que et

-te

imicroprocesadcw 8 o s x , sea capaz de intercambiar

informrrcidn

uti Lizando

tu comunicucidn serial' :

U s o del registro PCON,

este registro contiene destro de

demoninado SHOD, el c u a l afecta

al

baud

rate,

dando

si

mbyor

un

o

precisidn a el c a l c u l o visto anteriormente, se sugiere cargarto

80

H, para tener u n mejor aproximacidn

al

bit

menor

con

un

baud rate deseado.

Uso del registro TCON, este registro se encarga d e definir tos modos

de o p e r e i o n de

kscripcidn

TFr

dos

temporiacldores,

de

acuerdo

a

La

sigvente

:

TRI

TFX

Los

TFo

TRO

I Ex

I Ir

Bandera de s&re f Luj'o de timer I.

por hcrrdware.

IEo

Puesta

y

IT0

Zimpiada

I

TRX

Control de arranque del timffler I. Puesto y limpiado por

soft ware.

~

TFo

I

Bandera de sobre f l u j ' o d e l timer o.

I

Pusta

y

limpiada

por ?ux.rdware.

TRO

ControL de arranque del timer o. Pusto y

por

LiiApiCrdo

rof t - e .

I

IEX

Bandera de deteccidn de interrupcidn externa

f Tr

Control t i e 1 tipo tie interrupcidn I

IEo

Bandera tie deteccidn de interrupcith externa o

IT0

Control d e l t i e de interrupcidn externa o

I

U s o d a 1 registro T m D , este registro se encarga de definir

/¿e opercidn

de ¿os temporizu&res/

Idistributde de l a siguiepte manera

contadores de eventos y se

el

modo

encuentra

:

control d a 1 timar uno bit 5 y 4, control del timar cero bit I y o de

acuerdo a la siguiente tabla

I

I

I

I

MI

Ho

Modo de operacidn

O

O

O

TemporLzador de r 3 bits

O

I

I

Temporizador/Contcldor de r 6 bits

I

O

3

Temporiacrdor&ontador

de 8 bit

con

recarga

U s o del registro S O N , este registro se m a r g a de definir el modo de

5perarción d s t

puerto serial, ver jaugina sz

27

Valor de recarga para el temporiz&r/cont&r

este

uno,

vator

es

'fifudo p r el programador, con objeto de fijar el baud rate que se desea

'para eL enlace seriat.

Uso

deL

registro

interrupciones, es *ir

IP,

a

registro

encargado

de

dar prioridades de acuerdo

dar

valor

lap

a :

bit 5

Define el nivel de prioridad del timer

bit 4

Define el nivel de prioridad del puerto serial

bit 3

Define el nivel de prioridad deL timer

bit

2

Define el niveL de prioridad de la externa

bit

I

Define el nivel de prioridad del timer o

bit

o

Define el nivel de prioridad de

la

a

i

)

I

I

externa o

a . 8 L A IBH PC Y SU COMUNlCACfON ASIEHSRONA

€ 1 objetivo planteado inicialmente, contempla l a utilizuci¿n de unu

microcomputadora personal C P C ) , para establecer

la

comunicacidn, su

'uso

se describira a continwcidn, en las partes que sé involucran, es decir

o1 hcrrdwure ocupcrdo y

2.8.3

La

parte

el software que lo soporta.

ADAPTADOR DE C O M M C A C I O N ASIKRONA DE L A IBH Pt

centrul

del

adaptodor

28

asincrono

es

un

dispositivo

-._

j semiconductor, denominado

interface RS-as,

Lograr

I seriales, dentro.de

LOS

&e,este

es e¡ encargado de, atravds

comunicar

a

cucrLes

se

PC

La

otros

con

encuentran

otras

de

La

dispositivos

microcomputeras

1

personales.

n . 8 . 2 CONSiDERACiONES AL SOFTWARE

DE SOPORTE

1

EZ

I k c p tiene diferentes modos de operacidn que

son

seLeccionabLes

por programu, esto se Logra tornundo de La direccidn 3F8H a 3FFH para

La

parte primaria y aF8H a 2FFH pura La secundaria. Los bits de direcciones

40, AI

y A a seleccionan Los diferentes registros que definen

los

modos

, d e operacion.

Los registros antes mencionados son utilizados

pura!

controlar

las

operaciones de transmisidn y recepcidn de informacidn atraves del a

g

o

.

Los registros utitizados en La comunicaciOn son

:

*iins-ControL, este registro se encarga de co3troLar Los formatos

de

Lectura,

es

decir

transmitir o recibir,

&it

o

9

I

e¡

asi como

Longitud de La palabra

29

núymero

O

U

5 bits

O

z

6 bits

I

o

7 bits

I

I

8 bits

La

de

puridard.

bit

Q

t

-.

bit

P

bit 3

Nrirnero de bit de paro co uno.

I

dos>

HabiLitador de paridad

de k u d &te,

contiene un generador

el

p r o g r d t e de &at&

RATE, que es ccrparz de tomar

una

entrada

de

reloj'

C r . 8 1 ~

Megdiertz3 y dividirlo. La frecuencia de salida del generador de

baud rate es dada por

la siguiente funcidn:

divisor = Cfrecvencia de e n t r W / C b a u d rate

*L

r63

La Localiracidn de este generador es 3F8H y 3F#.

Los Listados c i e comunicacidn empleárdos figuran e n

LOS

anexos.

,

30

I

I

.

...

R E S U L T A D Y COEK=LUSiDE(ES

bntro.de

LOS

problemas que mayor atencidn requirieron se emwentra.

sin lugar a dudas el acoplamiento de los bavd rates, dado que al existir

zuuz diferencia parrticutarrmente pegue%a,

la comunicacich dificitmente

se

jx&r¿ consegir.

Otro problema que

no

por

evidente

es

menos

importante,

es

La

ate el entace fisico atrads de un c d t e conector.

La comunicacith en terminos gsneraLes puede mejorarse para

ZEM

alcansar

mayor flexibilidad. esto visto desde et punto de vista del usuario.

*..

BI BL I OGRAFI A

I ~ E L

ARCHITECTURAL SPECIFICATION

HAMAL

805s

Si NGLE4Hi P NI CRocOHpuTE ARCHITECTURAL SPECI FI CATI ON

AND F U K T i ONAL DESCRI ? T I ON

INTEL CORPORATION rg6o

MANUAL

INTEL

HAROWARE DESCRIPTION

INTEL CORPORATION r

IBM TECHNICAL

e

REFEREKE MANUAL.

INTERNATIONAL BUSINESS MACHINES CORPORATION

INTERFACING TO TH€ I S M PERSONAL COMPUiER

L e w i s C. Eggebrecht

Howard W. saiñ9 & C o . , I n c .

r

e

I

rpsr

-._

286 I/O CARD WITH PRINTEWSERlALfGAME

MATITECH INDUSTRIAL C O P .

HULTITECH POPULAR

1987

USER'S GUIDE

M I T I T E C H INDUSTRIAL COW. rp&5

HOTOROLA LINEAWINT€RFACE

DEVICES

EllOTOROLA fNDUSTRIAL C O P . r

e

US€%

S MANUAL

APENDíCES

-5

-.

-._

;VOCE1 CYCTEHC 8051 CROSS-ASCEHBLER

-

VERSIGW I*

ion

PRGE 1

iOURCE FILE NAHE: E#LACE*PRC

TECLB EOU 20H

i

;

;

PROGRAM PARA CAPTURA EE INFORHACiON ATRRVEC DE EL PUEFTG

SERIRL DEL HICROPROCESACOR 8031

i

QRG OOOOH

LJHP RECIBE

ORG 0013H

AJHP INTE

OR6 0023H

; luego de reset f i s i c o

; Rutina de caotura serial

RET1

OR6 0033

; Cosienzo de prograracion del baud rate

i

:

Tabla de bienvenida

i

T46L8:

29 i i f i l l l l i r

i

DE i ! t l i l l l P

DE 100010018

Codigo r i ~blanco

ÜE llOOOOO0E

DE ílQOOlllE

Iib lOOOl0OOb

DB

DE

DB

DE

$8

IliiilllE

llllflilá

Ifll1111S

l!l~l!l~~

lOOOOO00B

$E I i OOOOQ<l8

ilE lOflIr0002

DE ;::;:301E

0- :::::1::i

LLE A.

f'k :;.,r.Q!i;iE

r.

, / . * . . . . r

i

i

11.

!16&j~j::,E

3s f{t[t6jO005

DL llnOOi1OE

DE lOOOlQ6IE

23 1: i 111118

DE llillillF

DE !!ltllfIB

:

;

1

TI:

Tabla be ecos

D3 lIO00OOOEi

DB lllllOOlB

DB OOlOOlOOE

DB :C11ü000E

03 f00flOOlB

DB 10010010B

DB i000001úB

DE

DE

!O1110008

10OOaoOOE

'

; Codigo de [ 0 1

; Codigo cie [ 1 J

: Codigo de [ 2 I

; Codigo de [ 3 j

i C.odigo dti

; Cadigo

; Codigo

; Cadigo

i Codigo

de

i. d 1

E

5 I

de [ 6 i

ée [ 7 1

de i P 1

-..

3CET SYSTEM 8051 CROCC-ASSEt!üLER

-

VERSION 1*IO!!

PAGE L

URCE FILE NARE: ENLACE*PAC

054 A0

055 88

956 83

057 G6

iCodigo

; Codigo

; Codigo

; Codigo

; Codigo

iCodigo

; Codigo

)sa AI

b59 86

f5A 8E

558 751884

15E 903801

061 7634

163 FO

064 7410

%6 Fú

367 7440

169 F0

b6A 7490

$6 7810

le5 400033

RH :

[ B

[ C

1

I

1D I

[ E 1

[ F I

; Inicializatior del micro 8279

; Prograrrcien de1 reloj

; se envia el preescaler con un 34H

; Prograiacion del teclado y display

; se envia 8 Dis- por der. y Stan codif.

iPrograiacion de ia cola FIFO

i s e envia lectura siautoint- al lugar 000

; Prograiacion para la escritura de la ‘RAH en

; display

; limpia displays

i Primera entrada de l a tabla

i Direction de la tabla

; Actualization de ia entrada a ia tabla

; Copia de la entrada do la tabla

; Dirercion del a i m 8279, para datos

; se envia codigo de 7 segaentos

i Rutina de retardos be tiempo

i Siguiente codigo de bienvenida

i Realiza el ciclo :5 veces

i Programando

i Reprogramation para ia escritura &P la RA!!

: en display

i Iniciaiiza el t G A C H

i Pasi:iona en tah’ii i? inirialiiacion

1 Actuaiiia ti acutiiiador.

c O g i i < J O 6s 5 sEgEe-:Gs iie; 2

A c $

-

CAT :

CATT:

88 ib

J[ G:

i

e n v j a a; 8277 u p da![.

d e 5 S E ~ C L ~ Zd eS tabla

1

sigiente

codig.;

C G C $

3

escribe

i:

0

A

C.

$

5

5fi ?lI3bCIO

:it

CGdigB

91 OE

I 2 B818F3

XI 903801

’18 7406

4A

19 1

1A I

RECIBE:

I6C F0

i6D 311C

b i 7806

171 900033

‘74 E8

175 93

76 903800

b79 FO

.7# lfED

i7c O8

7D B810Fi

i50 903801

83 7690

185 F6

de

de

de

de

de

de

de

iaire

9

FQ

Reprograracian de errritura

pro graaia c i on 1 iqu i erda

se errvia prograaacion a 8279

i Prqrariacion de factnr.

i Timer 1 iodo 2

, Hods f i8 bits UART variablei

iPreset timer f

i Arranque del timer f

1 Iniciaiizacion de 10; con tadores

i para grabar 2k datas en RAH

i Direction de la RRR

1

9B 755786

YE 638928

Ai 759852

k4 438DD2

A7 D28E

r19 787F

AB 79FF

9D 900800

BO 758810

33 3098FD

-

_-

EDATO:

i

Espera la ilegada del dato

, - dI

I

KEET CYSTEIIS 8051 CROSS-BSCEHBLER

- VERSION

-..

i * 10H

: iectura del dato

: Escritura es RA@

: Sigtiierrte Uireccioi,

d

i

IOCET SYSTERC 8051 CROSS-ACCERBLER

WRCi FiiE NAHE: ENLACE.PAS

IOFE O0

)OFF 7EFF

If01 7DFF

)103 DDFE

405 DEFA

ii'??

DFF6

109 12

$04 903800

1OD EO

10E F520

iir, 32

!If 7520FF

114 E520

116 EbFf02

119 80Fs

11B ;2

lit €006

iiE 9 0 W !

!21 7400

123 f0

i24 7808

126 7dFF

128 903800

;2E FO

!2C D8FD

i2i DO90

130 22

-

VERSION 1 10R

I

iOCET CYCTEHC 8051 CROSS-ACCEHBLER

-

,

-..

VERSION 1-1OH

URCE FILE MARE: EWLACE*PBS

i

;

PGGE 5

PROCEDIHIENTO

..

ESCRIBE

A DISPLAYS L A DIi! Y EL BATO COUTEUIDD

i

j t t t t t i i f l t i t i t f C t t t t t t t ~ ~ f f C l i ) ) i t t

131 c000

133 COEO

135 A883

137 AF82

139 903801

13C 7492

13E F0

13F E8

140 54F0

142 C4

143 SOOOQB

146 $3

i47 903806

148 Fi

,JB E8

I4C 540;

.$E 900041

151 93

52 FiO380O

155 FO

.56 EF

i57 5dFU

59 Cd

158 90004k

i

DECPLEGA:

PUSH OW

POSH 224

HOV RO, DPH

HOV R7, DPi

HOY DPTfi,#3801H

ñúV &,#92H

ROVX PDPTR,A

HEW R,RO

AWL i

i

,#l i 1lOO00E

SWAP A

HliV DPIR, 1004Bti

!OK A, EiA+DPTk

nolc DPTR, f380Pn

F&q $OPTE,

y$$ A, Rfj

3:

i

Se

guarda terparaiiente ia inforna,cion

; contenida en R6 y ACC.

: Se alaacena l a iníornacion del DPTR

; para evitar perdida

i Se reprograia l a escritura en displays

: para escribir la inforracion contenida

: en el bloque de RAP! referido

: ircrirura de la iireccion, tomando

; por nibbiei ia inforracios, desi enroaquetando

; Consulta del eco de siete segientos .

; y escritura de e s t e a s : ~respectiva

; pgsicion en el display

i

E;E

2firia 6 $275

: Siguiente n'itiie, tratado de l a wisaá

form, i $ e s , desecpaquetando la

inforeacisn contenida paró si! consulta

P ?I

5D 93

15E 9O38OO

61 FO

162 EF

$3 546'

,$5 900-4:.

it. 9,

YCt38-ó

&

i

i

bC

FO

.6D 8883

tiF 8F82

1

! DOE0

73 EO

74 Fa

75 54FO

77 C4

78 900041

7B 93

7C 903800

7F FO

80 E8

81 540F

DPTR t a f i 2 e l valor quo 1entro? a

!a prnsente rutina

D iro ia inforsacion apentada i n e! DPTS

Ci ! IQanaeras.2i ent consuita a RAN

O t y r S E taia el valor de entrada d e l ACT

se torna por. nibbles iprinero el nitrbie

i a s alto, y cansuitando su eca be

siete segeentas en las tablas

es c rib i endo i o post e r i o mente e ri 5 u

respectiva position dentro dei display

atraves rfei controlador 8273

Procede sigiiiente nibble

r.

ti

I

i

I

090180

!

ICE?

CYSTEHS 8051 CROSS-ASSEHBLER

URCE FILE #At!€:

VERSION 1 lOH

ENLACE.PAC

183 900068

186 i!

187 903800

188 Fit

!8E DO00

18D 22

100

-

PAGE ‘6

MOV

DPTR, 1004EH

H O K 4, IAIDPTR

HOY DPTR, 13800H

ROWl PDPTR, A

PG? 008

E#B

RET

ELD

$123

iSCRIBi ooc9

EíECif!

FI

FINREi

FINi

IE

INTE

0111

6110

QOFD

OliE

0048

0104

IP

bI

LII

1111

LII!

LLAWA

100.

ORW

Q0B8

’

OOi i

O101

O103

0llC

OOFE

0OE6

QOF 6

üTR4

0OC6

RECIBE 0051

RETARDO OOED

0071

O114

0099

RH

RíT

CPVF

SCSN

TABLA

’

0045

O033

TCON

TECLA

TECCRIBE

TH 1

TIEHPO

TW0D

TN

0088

O020

Ofid

008D

OOfi

0089

OQdE

PROMAHA QUE REALIZA LA TRANSHiSION DE DATOS ASiNCRLiIA POR E i PUERTO SERIE

DE UNA 'PC" USANDO LA iNTERFACF 'RS232' ATRAVES D'E LOS REGISTROS DE: 8250 j

DGRRH RECIVE-DATA {INPUT OUTPUT) ;

NST

?-STAT = C3Fi);

ICC

= i12i;

{ DIRECClON DE REGISTRO D i STATUS )

;7

ARCH

: F I i E @F BYTE;

LEEl

: BYTE;

.EE2, RWISO, I , NUH : INTEGER;

VüH-ARCH

: STRING [15];

INICIALIZA E! nTRANS!iICOR!REiEPTOR ASINGRONO UIUIVERSAi 1

+ROCEDURE Iff]-URRT;

:ONST

IN]-SPD = $98;

CPD-i

= 508;

S P D H = $00;

SET-IO = +::;

P-CTiii = $3iB;

,

P-SPDL

= $3F8;

P-SPDH

= $3F9;

t

1

{ PEEXITE i N i C i A L í i F \ F tiEL$IiDkli j

f PARTE BAJA Di iAi.7. D i üii. lodi2

f PaXTi ALTA DE FACT- DE LZL. 10472 )

HABILITA ENTPRDAlSAtID4 !

{ DIRECClON DEL P W T O DE WHTRCil Di:

UART }

{ PARTE EkJP E; -A OiRECCii3W DEL FTL.

DE CTRLS DE VEL- j

{ PARTE ALTA DE LA DIRECClOFi DEL PTrS.

D i CRTi. DE VEL. 1

bIR I -UART ;

BP;',

, U N T E ('NOMIRE DE AkC;HIKi FUENTE '1;

READLM {NOH-ARCH);

kTIL IBRESULT = ü;

SSIGN(ARGH, NOH-ARCH f ;

ECET(ARCH) ;

UH := 2048;

3R I := 1 TO NUii DO

BEGIN

READ { ARCH, LEE 1 1;

PORT [$3F81:= L E E l ;

{ DATO CANAL CERD 1

END;

:OSE(nRCHi ;

I

1