Tema 4 EL PROCESADOR

Anuncio

Tema 4

EL PROCESADOR

4.1.

Introducción

Un computador es un dispositivo electrónico formado por componentes y subsistemas

digitales que permite el procesamiento de datos.

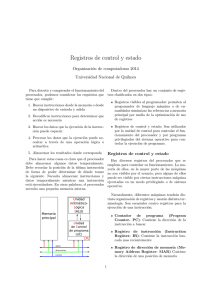

Desde el punto de vista estructural, el computador se considera dividido en varios niveles organizados jerárquicamente. La Figura 4.1 muestra la organización del computador

según estos niveles. Se distinguen 5 niveles básicos:

Nivel Digital: Se corresponde con la máquina fı́sica y engloba todos los circuitos

digitales que constituyen el computador y que han sido estudiados en los capı́tulos

anteriores.

Nivel Instrucciones Máquina: En este nivel se construyen programas en lenguaje

máquina (secuencias de 0’s y 1’s), que es el lenguaje capaz de entender la CPU.

También se incluye en este nivel la programación en ensamblador. El lenguaje ensamblador es la notación simbólica del lenguaje máquina.

Nivel Sistema Operativo: Los sistemas operativos son un conjunto de programas

que ayudan al usuario en la explotación del computador, siendo por tanto, una capa

software con la que se rodea el hardware para facilitar su utilización.

Nivel Lenguajes Alto Nivel: El objetivo de este nivel es facilitar al programador

la utilización del computador. Los programas escritos en un leguaje de alto nivel

deberán pasar por un proceso intermedio de traducción, denominado compilación,

antes de ejecutarse. El objetivo de la compilación es traducir el lenguaje de alto

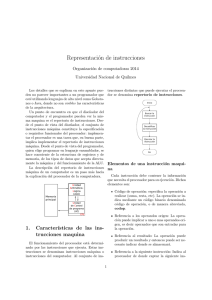

nivel a un lenguaje de bajo nivel que la máquina pueda entender. La figura 4.2

muestra un ejemplo de traducción de un trozo de código codificado en un lenguaje

de alto nivel (lenguaje C) a lenguaje ensamblador para el procesador MIPS y de

lenguaje ensamblador a lenguaje máquina. El programa que traduce el código escrito en lenguaje ensamblador al código equivalente en lenguaje máquina se llama

ensamblador.

1

2

TEMA 4. EL PROCESADOR

Aplicaciones

Lenguajes alto nivel

Sistema operativo

Lenguaje maquina

Logica digital

Figura 4.1: Organización estructural de un computador

Nivel Aplicaciones: Este nivel está formado por paquetes de programas de aplicación

que sirven para resolver problemas en campos especı́ficos de la ciencia o la gestión.

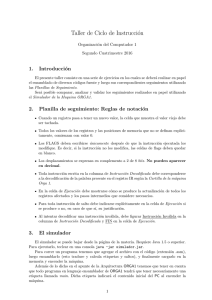

Centrándonos en el nivel digital, los elementos principales de un computador son: la

unidad de procesamiento central (CPU, Central Processing Unit) o procesador, la memoria

principal, el subsistema de entrada/salida y algunos medios de interconexión de todos estos

componentes como se muestra en la figura 4.3.

La unidad central de procesamiento (CPU): Controla el funcionamiento del computador y lleva a cabo sus funciones de procesamiento de datos. Frecuentemente se

llama simplemente procesador. Sus principales componentes estructurales son:

• Unidad de control: Controla el funcionamiento de la CPU y, por tanto, del

computador.

• Unidad aritmético-lógica (ALU, Arithmetic Logic Unit): Lleva a cabo las funciones de procesamiento de datos del computador.

• Registros: Proporcionan almacenamiento interno a la CPU.

• Interconexiones CPU: Proporcionan comunicación entre la unidad de control,

la ALU y los registros.

La memoria principal: Almacena instrucciones y datos.

E/S: Transfiere datos entre el computador y el entorno externo.

Sistema de interconexión: Proporciona la comunicación entre la CPU, la memoria

principal y la E/S.

La tarea de un computador es el procesamiento de datos en base al contenido de las

instrucciones. Ambos elementos (instrucciones y datos) se almacenan en memoria y se

codifican empleando un número especifico de bits. De este modo, la arquitectura de un

computador está diseñada para transferir bloques de información (o múltiplos de bloques) de un determinado tamaño. A cada uno de estos bloques se le denomina palabra y

4.1. INTRODUCCIÓN

High-level

language

program

(in C)

3

swa p ( i n t v [ ] , i n t k )

{ i n t t emp ;

t emp = v [ k ] ;

v [ k ] = v [ k +1 ] ;

v [ k + 1 ] = t emp ;

}

C compiler

Assembly

language

program

(for MIPS)

swa p :

mu l i

a dd

lw

lw

sw

sw

jr

$ 2 , $5 , 4

$ 2 , $4 , $2

$ 1 5 , 0 ( $2 )

$ 1 6 , 4 ( $2 )

$ 1 6 , 0 ( $2 )

$ 1 5 , 4 ( $2 )

$31

Assembler

Binary machine

language

program

(for MIPS)

0 0000 000 10100 00 10000 00 0 00001 10 00

0 0000 000 10001 11 00001 10 0 00010 00 01

1 0001 100 01100 01 00000 00 0 00000 00 00

1 0001 100 11110 01 00000 00 0 00000 01 00

1 0101 100 11110 01 00000 00 0 00000 00 00

1 0101 100 01100 01 00000 00 0 00000 01 00

0 0000 011 11100 00 00000 00 0 00000 10 00

Figura 4.2: Programa C compilado a lenguaje ensamblador y después ensamblado a lenguaje máquina

su tamaño, en número de bits, se denomina ancho de palabra. Todos los elementos del

computador (registros, buses, memorias, periféricos, ALUs) están diseñados para transferir, almacenar o procesar palabras.

El modo de funcionamiento de un computador consiste en la ejecución continua de

instrucciones que operan sobre diferentes datos. El proceso de ejecución de una instrucción

sigue una secuencia de 4 pasos:

1. Lectura o carga de la instrucción: La instrucción se transfiere desde memoria a

uno de los registros internos de la CPU, el denominado registro de instrucción (IR,

Instruction Register).

2. Decodificación de la instrucción: La unidad de control lee el contenido del IR y

4

TEMA 4. EL PROCESADOR

PROCESADOR

PC

IR

ENTRADA

Instrucciones

REGISTROS

UNIDAD DE

MEMORIA

Datos

SALIDA

ALU

UNIDAD DE

CONTROL

Figura 4.3: El computador: unidades funcionales básicas

decodifica la operación a ejecutar.

3. Ejecución de la instrucción: Se activan las señales necesarias para la ejecución de la

operación.

4. Determinación de la siguiente instrucción: Se asume que las instrucciones se ejecutarán de forma ordenada, es decir, después de la ejecución de una instrucción

concreta se carga y se ejecuta la siguiente instrucción contigua en memoria. Sin embargo, en ciertas situaciones se realizan saltos, pasando a ejecutarse otra instrucción

situada en una posición de memoria diferente. La CPU lleva un control de la dirección en memoria de la siguiente instrucción por medio del empleo de un registro de

la CPU especial al que se denomina contador de programa (PC, Program Counter).

Después de traer una instrucción, el contenido del PC se actualiza para apuntar a

la siguiente instrucción de la secuencia.

4.2.

El repertorio de instrucciones

El funcionamiento de la CPU está determinado por las instrucciones máquina que

ejecuta. Al conjunto de instrucciones distintas que puede ejecutar la CPU se le denomina

repertorio de instrucciones de la CPU. El repertorio de instrucciones define las funciones

que puede realizar la CPU y tiene, por tanto, un efecto significativo sobre la implementación de la misma.

Cada instrucción máquina debe contener la información que necesita la CPU para su

ejecución. Los elementos constitutivos de una instrucción máquina son:

4.2. EL REPERTORIO DE INSTRUCCIONES

4 bits

Codop

5

6 bits

6 bits

Ref. a operando

Ref. a operando

16 bits

Figura 4.4: Un formato de instrucciones sencillo

Código de operación: Especifica la operación a realizar (suma, E/S, etc.). La operación se indica mediante un código binario.

Referencia a operandos fuente: La operación puede implicar a uno o más operandos

fuente, es decir, operandos que son entradas para la instrucción.

Referencia al operando resultado: La operación puede producir un resultado.

Referencia a la siguiente instrucción: En la mayorı́a de los casos la siguiente instrucción sigue inmediatamente a la instrucción en ejecución. En tales casos no hay

referencia explı́cita a la siguiente instrucción. Cuando sea necesaria una referencia

explı́cita, debe suministrarse la dirección de memoria.

Los operandos fuente y resultado pueden estar en algunas de las siguientes áreas:

Memoria: Como en las referencias a instrucciones siguientes, debe indicarse la dirección de memoria.

Registro de la CPU: Salvo raras excepciones, una CPU contiene uno o más registros

que pueden ser referenciados por instrucciones máquina. Si existe más de uno, cada

registro tendrá asignado un número único, y la instrucción debe contener el número

del registro deseado.

Dispositivo de E/S: La instrucción debe especificar el módulo y dispositivo de E/S

para la operación. En el caso de E/S asignadas en memoria, se dará otra dirección

de memoria.

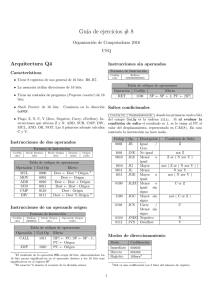

Dentro del computador, cada instrucción se representa por una secuencia de bits. Esta

secuencia se puede interpretar dividida en campos, correspondientes cada uno de ellos a

los elementos constitutivos de la instrucción. La descripción de la instrucción en campos

y bits se denomina formato de instrucción. La figura 4.4 muestra un ejemplo sencillo de

formato de instrucción. En la mayorı́a de los repertorios de instrucciones se emplea más

de un formato. Durante su ejecución, la instrucción se escribe en el registro de instrucción

(IR) de la CPU. La CPU debe ser capaz de extraer los datos de los distintos campos de

la instrucción para realizar la operación requerida.

Los aspectos más importantes a tener en cuenta en el diseño del repertorio de instrucciones son:

6

TEMA 4. EL PROCESADOR

Repertorio de operaciones: Cuántas y qué operaciones considerar, y cuán complejas

deben ser.

Tipos de datos: Los distintos tipos de datos con los que se efectúan operaciones.

Formatos de instrucciones: Longitud de la instrucción (en bits), tamaño de los distintos campos, etc.

Registros: Número de registros de la CPU que pueden ser referenciados por instrucciones, y su uso.

Direccionamiento: El modo o modos de direccionamiento mediante los cuales puede

especificarse la dirección de un operando o instrucción.

4.2.1.

Modelo de ejecución

El modelo de ejecución especifica el dispositivo (memoria, registro, etc.) que almacena

los operandos de las instrucciones. Una arquitectura no está restringida a un único modelo,

sino que suele dar soporte a varios. La elección de un modelo u otro es fuertemente

dependiente de la arquitectura del sistema. Por ejemplo, una unidad aritmético-lógica

que está exclusivamente conectada con registros (tanto para acceder a los operandos de

entrada como para almacenar el resultado) quedará limitada al empleo de un modelo

registro-registro (en el que ambos operandos son registros). Los modelos de ejecución

posibles son:

Modelo de pila: En este modelo los operandos se almacenan en una pila de modo

que se opera con datos de la pila y el resultado es colocado encima de la pila. Se

denota por POP a la instrucción que retira de la pila un dato y lo copia a memoria

o a un registro. Se denomina PUSH a la instrucción que inserta en la pila un valor

de memoria o de un registro.

Modelo de registro-registro (o carga/almacenamiento): En este caso ambos operandos deben residir en un registro. Es el modelo de ejecución más extendido, ya que

las instrucciones que lo emplean se pueden ejecutar de forma rápida (dado que el

acceso a un registro es inmediato). En este modelo es necesario transferir de forma

explı́cita los datos entre la memoria y los registros a través de instrucciones de carga

y de almacenamiento.

Modelo registro-memoria: En este modelo un operando está en un registro y el otro

está en una posición de memoria. El resultado se almacena en un registro.

Modelo memoria-memoria: Ambos operandos residen en memoria principal y el

resultado también se almacena en memoria principal. Mediante este modelo no es

necesario transferir los datos entre la memoria y los registros, sin embargo, tiene el

inconveniente de que la ejecución de las instrucciones requiere un gran número de

ciclos de reloj (necesarios para acceder a los datos en memoria).

4.2. EL REPERTORIO DE INSTRUCCIONES

4.2.2.

7

Direccionamiento

En esta sección analizamos las técnicas de direccionamiento más comunes. Se denominan modos de direccionamiento a aquellos algoritmos empleados por el procesador para

calcular las direcciones de las instrucciones y datos. La dirección real de memoria especificada por el modo de direccionamiento se denomina dirección efectiva.

Direccionamiento inmediato: El operando es una constante cuyo valor se almacena

en el campo operando de la instrucción. La ventaja del direccionamiento inmediato

es que una vez captada la instrucción no se requiere una referencia a memoria para

obtener el operando. La desventaja es que el tamaño del dato está restringido a la

longitud del campo de direcciones.

Direccionamiento directo: El operando se encuentra almacenado en memoria en

la posición indicada por el campo operando. La limitación es que proporciona un

espacio de direcciones reducido.

Direccionamiento indirecto: La instrucción contiene en el campo operando la dirección de una posición de memoria en la que se almacena la dirección del operando

deseado. La desventaja es que la ejecución de la instrucción requiere dos referencias

a memoria para capturar el operando, una para captar su dirección y otra para

obtener su valor.

Direccionamiento de registros: El operando referenciado se encuentra en un registro.

El número de registro se especifica dentro de la instrucción en el campo operando.

Las ventajas son: (1) solo es necesario un campo pequeño de direcciones en la instrucción; (2) el tiempo de acceso a un registro interno es mucho menor que a la

memoria principal. La desventaja es que el espacio de direcciones está muy limitado.

Direccionamiento indirecto con registro: La instrucción contiene en el campo operando el número del registro en el que se almacena la dirección de memoria del

operando deseado. La ventaja es que este direccionamiento emplea una referencia

menos a memoria que el direccionamiento indirecto.

Direccionamiento con desplazamiento: El campo operando contiene una dirección

relativa o desplazamiento (D). La instrucción también especifica, implı́cita o explı́citamente, otras posiciones de memoria de almacenamiento (R), usualmente registros

del procesador, conteniendo información adicional de direccionamiento. La dirección efectiva se calcula a través de una suma (D+R). Los tres usos más comunes

del direccionamiento con desplazamiento son:

• Desplazamiento relativo: El registro referenciado implı́citamente es el contador

de programa (PC). La dirección efectiva es un desplazamiento relativo a la

dirección de la instrucción.

8

TEMA 4. EL PROCESADOR

• Direccionamiento con registro-base: El registro referenciado (implı́cita o explı́citamente) contiene una dirección de memoria, y el campo de dirección contiene

un desplazamiento desde dicha dirección.

• Indexado: El campo de operando referencia una dirección de memoria y el

registro referenciado contiene un desplazamiento positivo desde esa posición.

En la Figura 4.5 se muestra gráficamente un resumen de los modos de direccionamiento

vistos aquı́.

4.2.3.

Operaciones del repertorio de instrucciones

El número de códigos de operación diferentes varı́a ampliamente de una máquina a

otra. Sin embargo, en todas las máquinas podemos encontrar los mismos tipos generales

de operaciones. Una clasificación tı́pica y útil es la siguiente:

Transferencias de datos. Las instrucciones que transfieren datos entre memoria y

registros se denominan instrucciones de transferencia de datos. Para acceder a una

palabra en memoria la instrucción debe proporcionar la dirección de memoria. La

instrucción de transferencia que mueve datos de memoria a algún registro se denomina carga (load ). La instrucción complementaria transfiere datos de un registro a

memoria y se denomina almacenamiento (store).

Aritméticas. La mayorı́a de las máquinas proporcionan las operaciones artiméticas básicas de suma, resta, multiplicación y división. Estas se tienen siempre para

números enteros con signo y, a menudo, para números en coma flotante. Otras operaciones posibles son, por ejemplo, cálculo del valor absoluto, cambiar el signo al

operando o incrementar o decrementar el operando.

Lógicas. La mayorı́a de las máquinas también disponen de diversidad de operaciones para manipular bits individuales dentro de una palabra o de otra unidad

direccionable. Están basadas en operaciones booleanas.

De Entrada/Salida. Son instrucciones de transferencia de datos en las cuales el

origen/destino es un módulo de E/S.

De control de flujo. En todos los tipos de operaciones discutidos hasta aquı́, la

siguiente instrucción a ejecutar es la inmediatamente posterior en memoria a la

instrucción en curso. Sin embargo, una fracción significativa de las instrucciones

de cualquier programa tienen como misión cambiar la secuencia de ejecución de

instrucciones. La operación que realiza la CPU es actualizar el contador de programa

para que contenga la dirección de alguna de las instrucciones que hay en memoria.

Las operaciones de control de flujo que se pueden encontrar en los repertorios de

instrucciones son:

4.2. EL REPERTORIO DE INSTRUCCIONES

9

Figura 4.5: Modos de direccionamiento

• Instrucciones de bifurcación, también llamadas de salto. Tienen como uno de

sus operandos la dirección de la siguiente instrucción a ejecutar.

• Instrucciones de salto condicional. Se efectúa la bifurcación (se actualiza el

10

TEMA 4. EL PROCESADOR

contador de programa con la dirección especificada en el operando) sólo si se

cumple una condición dada, en caso contrario se ejecuta la instrucción siguiente

de la secuencia (se incrementa el contador de programa de la forma habitual).

• Instrucciones de llamada a subrutina. En cualquier punto del programa se

puede invocar o llamar a una subrutina. Se ordena al computador que pase

a ejecutar la subrutina y que retorne después al punto en que tuvo lugar la

llamada. El uso de subrutinas requiere por tanto dos instrucciones básicas: una

instrucción de llamada, que produce una bifurcación desde la posición actual

al comienzo de la subrutina, y una instrucción de retorno de la subrutina al

lugar desde el que se llamó.

De control del sistema. Llamadas al sistema operativo para que realice algún

servicio: E/S, detener la ejecución del programa, ...

4.3.

Repertorio de instrucciones del MIPS

El diseño del juego de instrucciones es un tema complejo y sujeto a un gran número de

compromisos. Existen tantos juegos de instrucciones como arquitecturas, cada uno con sus

ventajas y sus inconvenientes. No obstante, existen básicamente dos filosofı́as de diseño

en las que se pueden agrupar todas las arquitecturas: CISC y RISC. Los diseños CISC

(Complex Intruction Set Computer, computadora de conjunto de instrucciones complejo)

se basan en un juego de instrucciones muy rico con modos de direccionamiento potentes y

complejos. Esto implica que los programas necesitan menos instrucciones, con lo cual son

más fáciles de desarrollar y mantener por los programadores. Además, los programas ocupan menos memoria. La filosofı́a RISC (Reduced Instruction Set Computer, computadores

de conjunto de instrucciones reducido) en contrapartida se basa en un número relativamente pequeño de instrucciones disponibles, por lo regular unas 50, todas ellas muy

sencillas, con pocos modos de direccionamiento, pero que se ejecutan muy eficientemente.

En lo que resta del capı́tulo se estudiará un subconjunto del repertorio de instrucciones

de un computador real. El repertorio de instrucciones escogido proviene del MIPS, usado

por NEC, Nintendo, Silicon Graphics y Sony, entre otros, y es un tı́pico ejemplo de diseño

RISC.

4.3.1.

Arquitectura del MIPS

Las primeras implementaciones de la arquitectura MIPS (familia R20x0 y R30x0)

consistieron en una unidad de proceso de enteros (la CPU) y un conjunto de procesadores

que realizaban tareas auxiliares u operan con otros tipos de datos, como números en coma

flotante. En la figura 4.6 se muestra el esquema del MIPS R2000.

El ancho de palabra de la arquitectura MIPS es de 32 bits. La arquitectura MIPS posee 32 registros genéricos de 32 bits ($0-$31) para utilización de la CPU, siendo el registro

4.3. REPERTORIO DE INSTRUCCIONES DEL MIPS

11

Memory

CPU

Coprocessor 1 (FPU)

Registers

Registers

$0

$0

$ 31

$31

Arithmetic

unit

Multiply

divide

Lo

Arithmetic

unit

Hi

Coprocessor 0 (traps and memory)

Registers

BadVAddr

Cause

Status

EPC

Figura 4.6: Esquema del MIPS R2000

$0 solo de lectura y con valor cero. De los restante registros, solo el $31 es implı́citamente

usado por una instrucción. Concretamente, por la instrucción de invocación de una subrutina (jal) y se utiliza para guardar la dirección de retorno, como veremos más adelante.

Adicionalmente, el MIPS contiene dos registros para poder operar con operandos de 64

bits, como sucede en el caso de la multiplicación y división, llamados hi (high) y lo (low).

En el cuadro 4.1 se puede ver la lista de registros del MIPS y sus usos.

Como se ha comentado antes, estos procesadores MIPS no disponen de unidad de coma

flotante incluida en el microprocesador, implementando estas funciones en coprocesadores

separados. La arquitectura MIPS tiene en cada coprocesador 32 registros de 32 bits para

coma flotante ($f0-$f31), que pueden ser organizados en 16 registros de doble precisión

con 64 bits (las designaciones par de los registros).

En cuanto al direccionamiento de la memoria, éste se realiza por bytes. Esto quiere

decir que las direcciones de memoria de 2 palabras consecutivas estarán separadas en 4

unidades (ya que las palabras son de 4 bytes). Cuando una palabra se carga desde memoria

a un registro o se pasa a memoria desde un registro, la dirección de memoria involucrada

ha de ser múltiplo de 4. Esto es lo que se denomina restricción de alineamiento. Las

direcciones que son múltiples de 4 se llaman direcciones alineadas.

Un aspecto importante en cualquier procesador con un ancho de palabra superior a 1

12

TEMA 4. EL PROCESADOR

Nombre

Número

Uso

$zero

$at

$v0-$v1

0

1

2-3

$a0-$a3

$t0-$t7

$s0-$s7

$t8-$t9

$k0-$k1

$gp

$sp

$fp

$ra

4-7

8-15

16-23

24-25

26-27

28

29

30

31

Valor constante 0

Reservado para el ensamblador

Valores para resultados y evaluación de expresiones

Paso de parámetros

Registros temporales

Registros que deben preservarse

Registros temporales

Reservado para núcleo de SO

Puntero global

Puntero de pila

Puntero de bloque de activación

Dirección de retorno

Preservado

en llamada

n.a.

n.a.

no

sı́

no

sı́

no

n.a.

sı́

sı́

sı́

sı́

n.a.: no aplica

Cuadro 4.1: Registros del MIPS y su uso convencional en llamadas a procedimientos

byte es el ordenamiento de los bytes dentro de una palabra. Dicho ordenamiento puede

tomar dos alternativas: big endian o little endian. En little endian la dirección de un dato

es la dirección del byte menos significativo del dato. En big endian la dirección del dato

es el byte más significativo del mismo:

palabra de 4 bytes

Big Endian

A B C D

Little Endian

Este aspecto ha de tenerse en cuenta cuando se intercambia información entre distintas máquinas. Ejemplos de arquitecturas little endian son los procesadores x86, DEC

ALPHA y VAX. Ejemplos de arquitecturas big endian son IBM POWER, Motorola 6800

y 68k. Algunos procesadores (por ejemplo MIPS, PowerPC, Alpha y SPARC v9) permiten

configurar el comportamiento, estas arquitecturas reciben el nombre de bi-endian.

4.3.2.

Tipos de instrucciones MIPS

Los tipos básicos de instrucciones que soporta el MIPS son los siguientes:

Transferencia de datos

Aritméticas y lógicas

De Control de Flujo

4.3. REPERTORIO DE INSTRUCCIONES DEL MIPS

13

• Salto condicional

• Bifurcación

Las caracterı́sticas más importantes de estas instrucciones en el procesador MIPS son:

La longitud de todas las instrucciones MIPS es de 32 bits.

Los operandos de las operaciones aritméticas son siempre registros. MIPS es, por

tanto, una arquitectura de carga/almacenamiento (registro-registro).

El acceso a memoria se hace a través de las operaciones de carga y almacenamiento

(transferencia de datos).

Para acceder a una palabra en memoria hay que indicar su dirección. MIPS direcciona bytes individuales. No obstante, debe tenerse en cuenta que la mayor parte

de las instrucciones que acceden a memoria lo hacen de forma alineada, por lo que

la dirección a la que se accede debe ser múltiplo de 4.

4.3.3.

Formatos de las instrucciones MIPS

Como comentábamos anteriormente, el número de bits de una instrucción MIPS es

siempre de 32, el mismo tamaño que una palabra. Cada instrucción MIPS se divide en

una serie de campos a los que se les da unos nombres para identificarlos fácilmente:

op: operación básica de la instrucción, tradicionalmente llamada código de operación.

rs: primer registro operando fuente.

rt: segundo registro operando fuente.

rd : registro operando destino, donde se almacena el resultado de la operación.

shamt: tamaño del desplazamiento (shift amount).

funct: función. Este campo selecciona la variante especı́fica de la operación del campo

op, y a veces se le denomina código de función.

El compromiso elegido por los diseñadores del MIPS es guardar todas las instrucciones

con la misma longitud, pero utilizar diferentes clases de formatos de instrucción para

diferentes clases de instrucciones. Los tres tipos de formatos posibles en MIPS son:

Formato tipo R: utilizado por las instrucciones aritméticas y lógicas.

Formato tipo I: utilizado por las instrucciones de transferencia, las de salto condicional y las instrucciones con operandos inmediatos.

14

TEMA 4. EL PROCESADOR

Tipo - R

op

rs

rt

rd

6 bits

5 bits

5 bits

5 bits

shamt

funct

5 bits

6 bits

Tipo - I

op

6 bits

rs

5 bits

rt

direccion

16 bits

5 bits

Tipo - J

op

6 bits

direccion

26 bits

Figura 4.7: Codificación de instrucciones en el MIPS

Formatos tipo J: utilizado por las instrucciones de bifurcación.

En la figura 4.7 se muestran los campos para cada uno de los tres tipos de formato.

Aunque tener múltiples formatos complica la circuiterı́a, se puede reducir la complejidad

guardándolos de forma similar. Por ejemplo, los tres primeros campos de los formatos

tipo-R y tipo-I son del mismo tamaño y tienen los mismos nombres. Los formatos se

distinguen por el valor del primer campo: a cada formato se le asigna un conjunto de

valores distintos en el primer campo y por lo tanto la circuiterı́a sabe si ha de tratar

la última mitad de la instrucción como tres campos (tipo-R) o como un campo simple

(tipo-I), o si la instrucción es tipo-J.

4.3.4.

Instrucciones aritmético-lógicas

El tipo de formato de las instrucciones aritmético-lógicas es tipo-R y el número de

operandos es siempre tres. Estos operandos son siempre registros. El modo de direccionamiento empleado, por tanto, es direccionamiento de registro.

En la figura 4.8 se muestran las codificaciones en el lenguaje máquina MIPS para dos

ejemplos de instrucciones aritméticas, suma y resta. Para cada instrucción se muestra

también la codificación de cada campo en decimal y la representación simbólica de la

instrucción utilizando leguaje ensamblador. La instrucción add $rd,$rs1,$rs2 suma el

contenido de los registros $rs1 y $rs2 y almacena el resultado en $rd.

Muchas veces los programas usan constantes en las operaciones. Para usar una constante utilizando las instrucciones de la figura 4.8 habrı́a que cargarla de memoria al

registro para posteriormente sumarla. Una alternativa que evita los accesos a memoria es

ofrecer versiones de las instrucciones aritméticas en las cuales un operando es constante.

Se usa en este caso el formato de instrucción tipo-I y el modo de direccionamiento es

4.3. REPERTORIO DE INSTRUCCIONES DEL MIPS

15

add $7,$3,$6

0

3

6

7

0

32

000000

00011

00110

00111

00000

100000

31

25

20

15

10

5

0

sub $7,$3,$6

0

3

6

7

0

34

000000

00011

00110

00111

00000

100010

31

25

20

15

10

5

0

Figura 4.8: Estructuras del lenguaje MIPS para suma y resta

direccionamiento inmediato. En la figura 4.9 se muestra la estructura para el ejemplo de

la operación suma inmediata. La instrucción addi $rd,$rs1,inm suma el contenido de

$rs1 y el valor inm y almacena el resultado en $rd.

addi $8,$8,4

8

8

8

4

001000

01000

01000

0000 0000 0000 0100

31

25

20

15

0

Figura 4.9: Estructura del lenguaje MIPS para la suma inmediata

Los operandos constantes aparecen con frecuencia, y situarlos dentro de las instrucciones aritméticas hace que se ejecuten mucho más rápido.

4.3.5.

Instrucciones de transferencia

Las instrucciones de transferencia son instrucciones tipo-I. En la figura 4.10 se muestran las codificaciones en lenguaje MIPS para dos ejemplos de operaciones de transferencia

muy comunes, la carga y el almacenamiento de una palabra (lw y sw respectivamente).

El direccionamiento usado en este tipo de instrucciones es direccionamiento con desplazamiento (registro-base). La instrucción lw $rt,desp($rs) carga la palabra almacenada en

la dirección de memoria $rs+desp en el registro $rt. La instrucción sw $rt,desp($rs)

almacena la palabra contenida en el registro $rt en la dirección de memoria $rs+desp.

16

TEMA 4. EL PROCESADOR

Los 16 bits para especificar el desplazamiento significan que una instrucción de carga

puede cargar cualquier palabra dentro de la región ±215 de la dirección del registro base

$rs.

lw $8,1200($15)

35

15

8

100011

01111

01000

31

25

20

1200

0000 0100 1011 0000

15

0

sw $8,1200($15)

43

15

8

101011

01111

01000

31

25

20

1200

0000 0100 1011 0000

15

0

Figura 4.10: Estructura del lenguaje MIPS para las instrucciones de transferencia

Existe también otra instrucción de transferencia que implementa MIPS, es la llamada

instrucción load upper inmediate (lui) que sirve especı́ficamente para almacenar los 16

bits de la parte alta de una constante en un registro. La instrucción lui $rt,inm almacena

los 16 bits de inm en los 16 bits más significativos del registro $rt poniendo los otros 16

bits a cero ($rt=inm((16). En la figura 4.11 se puede ver la operación lui.

Version en lenguaje maquina:

001111

00000

01000

lui $8,255

0000 0000 1111 1111

Contenido del registro $8

tras la ejecucion:

0000 0000 1111 1111

0000 0000 0000 0000

Figura 4.11: El efecto de la instrucción lui

4.3.6.

Instrucciones de salto condicional

Lo que distingue a un computador de una simple calculadora es la habilidad de tomar

decisiones. Basándose en los datos de entrada y los valores creados durante la computación, el computador ejecuta diferentes instrucciones. La toma de decisiones se representa comúnmente en los lenguajes de programación de alto nivel usando la sentencia if (si

4.3. REPERTORIO DE INSTRUCCIONES DEL MIPS

17

condicional), combinada a veces con sentencias go to (ir a) y etiquetas. El lenguaje máquina del MIPS incluye dos instrucciones de toma de decisiones, similares a una sentencia if

con un go to. Las instrucciones beq (branch if equal ) y bne (branch if not equal ). Estas

dos instrucciones se conocen tradicionalmente como saltos condicionales. Son instrucciones de tipo-I y el modo de direccionamiento empleado por ambas es direccionamiento

con desplazamiento relativo (direccionamiento con desplazamiento relativo al PC donde

el desplazamiento se indica en número de palabras en vez de en número de bytes).

La instrucción beq $rs,$rt,despl significa ir a la instrucción que se encuentra en

la dirección de memoria (PC+4)+4*despl si el valor del registro $rs es igual al valor

del registro $rt. La instrucción bne $rs,$rt,despl significa ir a la instrucción que se

encuentra en la dirección de memoria (PC+4)+4*despl si el valor de $rs no es igual al

valor en $rt. En ensamblador, el uso de etiquetas libera al programador del tedioso cálculo

de las direcciones de salto. Estas instrucciones se muestran en la figura 4.12. En este caso

se utilizan etiquetas. El ensamblador calculará el desplazamiento necesario para saltar a

L1.

beq $19,$20,L1

4

19

20

L1

000100

10011

10100

0001 1000 0011 1101

31

25

20

15

0

bne $19,$20,L1

5

19

20

L1

000101

10011

10100

0001 1000 0011 1101

31

25

20

15

0

Figura 4.12: Estructura en lenguaje MIPS de las instrucciones de salto condicional

La prueba de igualdad y desigualdad es probablemente la más habitual, pero a veces es

útil establecer comparaciones del tipo “menor que”. Para ello se dispone de la instrucción

lógica MIPS slt (set on less than), activar si es menor que. El efecto de la instrucción slt

$rd,$rs,$rt es $rd=($rs<$rt). También existe la versión de esta instrucción utilizando

operandos inmediatos: slti $rd,$rs,inm es $rd=($rs<inm) La estructura de ambas

instrucciones se muestra en la figura 4.13.

18

TEMA 4. EL PROCESADOR

slt $8,$19,$20

0

19

20

18

8

8

0

42

slti $8,$19,10

10

10

Figura 4.13: Estructura de las instrucciones slt y slti en el MIPS

4.3.7.

Instrucciones de bifurcación

Una bifurcación se puede ver como un salto incondicional, es decir, la instrucción

obliga a la máquina a seguir siempre el salto. Para distinguir entre saltos condicionales e

incondicionales, el nombre MIPS para este tipo de instrucción es jump.

j L1

L1

2

jr $8

0

8

0

0

0

8

Figura 4.14: Estructura de las instrucciones jump y jump register en el MIPS

La instrucción de bifurcación jump (j) es de tipo-J y su modo de direccionamiento es

pseudodirecto. El efecto de la instrucción j es saltar a la dirección de salto especificada

por la instrucción. La dirección de salto son los 26 bits de la instrucción desplazados 2

posiciones a la izquierda (es decir, se multiplica por 4) y concatenados con los 4 bits de

mayor peso del contador de programa (P C ← (P C + 4)31−28 IR25−0 00). Al igual que en

las instrucciones de salto condicional, el ensamblador permite el uso de etiquetas.

La instrucción de bifurcación jump register (jr) es de tipo-R y utiliza modo de direccionamiento indirecto con registro. El efecto de la instrucción es saltar a la dirección de

memoria almacenada en el registro.

En la figura 4.14 se muestran estas instrucciones y su formato.

4.3.8.

Modos de direccionamiento del MIPS

Resumimos aquı́ los modos de direccionamiento del MIPS:

Modo de direccionamiento registro, donde el operando es un registro.

4.3. REPERTORIO DE INSTRUCCIONES DEL MIPS

19

Modo de direccionamiento base más desplazamiento, donde el operando está en una

localización de memoria cuya dirección es la suma de un registro y una constante

presente en la propia instrucción.

Modo de direccionamiento inmediato, donde el operando es una constante que aparece en la misma instrucción.

Modo de direccionamiento relativo al PC, donde la dirección es la suma del contador de programa (PC) y la constante de la instrucción multiplicada por 4. Como se

verá más adelante, es conveniente incrementar el PC pronto para apuntar a la siguiente dirección. De aquı́ que la dirección MIPS es realmente relativa a la dirección

de la siguiente instrucción (PC+4) en lugar de a la instrucción actual (PC).

Modo de direccionamiento pseudodirecto, donde la dirección de salto son los 26 bits

de la instrucción desplazados 2 posiciones a la izquierda y concatenados con los 4

bits de mayor peso del contador de programa. Esto limita los saltos a 256MB, si

necesitaramos saltar más allá tendrı́amos que sustituir la instrucción jump por jump

register precedida por otra instrucción para cargar la dirección de 32 bits completa

en el registro.

Una operación simple puede usar más de un modo de direccionamiento. La operación

de sumar, por ejemplo, usa tanto el direccionamiento inmediado (si usamos la instrucción

addi), como el direccionamiento registro (si usamos la instrucción add). La figura 4.15

muestra, para cada modo de direccionamiento, cómo se localiza el operando correspondiente.

4.3.9.

Llamadas a subrutinas

Un procedimiento o subrutina es una herramienta que los programadores usan para

estructurar programas con el fin de hacerlos fácilmente comprensibles y permitir que

el código sea reutilizado. Los parámetros de las subrutinas permiten pasar valores a la

subrutina y que esta retorne resultados.

En la ejecución de una subrutina el programa debe seguir los siguientes pasos:

1. Situar los parámetros en un lugar donde la subrutina pueda acceder a ellos.

2. Transferir el control a la subrutina.

3. Adquirir los recursos de almacenamiento necesarios para el procedimiento.

4. Realizar la tarea deseada.

5. Situar el valor del resultado en un lugar donde el programa que lo ha llamado pueda

acceder a él.

6. Retornar el control al punto de origen.

20

TEMA 4. EL PROCESADOR

x4

x4

4 bits

Figura 4.15: Modos de direccionamiento del MIPS.

4.3. REPERTORIO DE INSTRUCCIONES DEL MIPS

21

En la figura 4.16 se muestra gráficamente la distribución de la memoria para programas

y datos. El espacio de memoria de un programa de usuario se organiza en varios segmentos:

Segmento de texto: Es un segmento de tamaño fijo que contiene las instrucciones

del programa ejecutable.

Segmento de datos: Es un segmento de tamaño variable dividido en varias secciones

para los distintos tipos de datos.

Montı́culo (heap): Contiene los datos reservados dinámicamente y crece de direcciones menores a mayores.

Segmento de pila (stack): Avanza de direcciones mayores a menores. Se utilizará en

las llamadas a procedimientos.

$sp

7 f f f f f f f hex

Stack

Dynamic data

$gp

1000 8000 h e x

Static data

1000 0000 h e x

Text

pc

0040 0000 h e x

Reserved

0

Figura 4.16: Distribución de la memoria para programas y datos en el MIPS

En general, en la mayorı́a de los procesadores la comunicación entre un segmento de

código que llama a una subrutina (invocador) y la subrutina se realiza mediante la pila. El

invocador sitúa los parámetros en la pila. Posteriormente la subrutina coloca también en

la pila la información que debe guardar temporalmente y al finalizar libera dicho espacio

y deja en la pila el resultado de la subrutina. Finalmente el invocador recupera de la pila

el resultado.

La pila es un espacio de memoria con estructura tipo LIFO (Last In First Out), en

la que el último que entra es el primero en salir. Esta estructura necesita un puntero que

apunte a la dirección más recientemente utilizada, para guardar dónde deberı́a de situar el

22

TEMA 4. EL PROCESADOR

siguiente elemento a volcar, o para saber dónde se pueden encontrar los valores guardados.

Por razones históricas, la pila crece de direcciones de memoria superiores a inferiores. Por

tanto, para poner valores en la pila tendremos que restar al puntero de pila y para quitar

valores tendremos que sumar al puntero de pila.

Los programas del MIPS reservan un registro solo para la pila, stack pointer ($sp) o

puntero de pila. Veamos un par de ejemplos de como introducir datos en la pila y como

transferirlos desde ella.

Para realizar la operación de push (guardar) salvando dos registros en la pila:

addi $sp,$sp,-8

sw $v0,0($sp)

sw $v1,4($sp)

# ajusto la pila para a~

nadir dos elementos

# salvo el registro $2

# salvo el registro $3

Para realizar la operación de pop (recuperar) transfiriendo los datos de la pila a dos

registros:

lw $v0,0($sp)

lw $v1,4($sp)

addi $sp,$sp,8

#

#

#

#

restaura el registro $2

restaura el registro $3

ajusta el puntero de la pila para eliminar

dos elementos

Sin embargo, es más rápido acceder a registros que a memoria, de aquı́ que el convenio

de llamadas MIPS se apoya en el banco de registros para evitar accesos a pila y acelerar

ası́ la ejecución de los programas. Los programas MIPS asignan por convenio los siguientes

registros de los 32 disponibles en cada llamada de procedimiento:

$a0-$a3: cuatro registros de argumentos en los cuales se pasan parámetros. Si se

necesitan más parámetros se pasan a través de la pila.

$v0-$v1: dos registros de valores en los cuales se retornan valores.

$ra: un registro de retorno de dirección para volver al punto de origen.

Además de esta asignación de registros, el lenguaje ensamblador del MIPS incluye

una instrucción solo para procedimientos (jal): salta a una dirección y simultáneamente

salva la dirección de retorno (dirección de la siguiente instrucción) en el registro $ra. La

instrucción jal (jump-and-link ) se muestra en la figura 4.17. Utiliza direccionamiento

pseudodirecto al igual que jump para el cálculo de la dirección de salto. El ensamblador

permite el uso de etiquetas para especificar la dirección de salto.

La dirección de retorno es necesaria porque el mismo procedimiento se puede llamar

desde diferentes puntos del programa. La instrucción jal guarda P C + 4 en el registro

$ra para encadenar la siguiente instrucción con el retorno del procedimiento.

4.3. REPERTORIO DE INSTRUCCIONES DEL MIPS

23

jal direccion_subrutina

3

direccion_subrutina

Figura 4.17: Estructura de la instrucción jump-and-link en MIPS.

Para realizar el salto de retorno disponemos de la instrucción jump register comentada anteriormente: jr $ra salta a la dirección almacenada en el registro $ra, que es

justamente lo que se requiere.

Resumiendo, el programa que llama al procedimiento (invocador) pone los valores

de los parámetros en $a0-$a3 y usa la instrucción jal para saltar al procedimiento. El

procedimiento (también conocido por invocado) realiza los cálculos, pone los resultados

en $v0-$v1 y devuelve el control al invocador usando jr $ra.

Salvaguarda de registros

Si un procedimiento modifica los registros utilizados por la rutina invocadora los valores de los registros deben ser guardados y restaurados utilizando para ello la pila. Los

dos convenios estándares para guardar y restaurar registros son:

Guardar invocador (caller save): el procedimiento invocador es el responsable de

guardar y restaurar los registros que necesite conservar.

Guardar invocado (callee save): el invocado es el responsable de guardar y restaurar

cualquier registro que vaya a utilizar.

Para evitar salvar y restaurar un registro cuyo valor nunca se usa, los programas MIPS

ofrecen dos clases de registros (ver cuadro 4.1):

Registros temporales ($t0-$t9): Se utilizan para guardar datos temporales que no

necesitan ser preservados entre llamadas. No son preservados por el invocado (procedimiento llamado) en una llamada de procedimiento. Estos registros deben ser

guardados por el invocador en caso de que necesite conservar sus valores.

Registros salvados ($s0-$s7): Se utilizan para almacenar valores de vida más larga

que se deben preservar durante las llamadas. Si el invocado los usa salva previamente

su valor.

Esta simple convención reduce el volcado de registros.

24

TEMA 4. EL PROCESADOR

4.4.

Diseño de la Unidad Central de Proceso

La unidad central de proceso es la encargada de la ejecución de las instrucciones

especificadas por el programa. Este módulo esta formado por dos bloques, el Camino de

Datos y la Unidad de Control.

Camino de Datos: se encarga de realizar todas las operaciones requeridas por las

instrucciones del nivel de lenguaje máquina. Contiene los siguientes elementos (ver

Figura 4.18):

• Unidad Aritmético-Lógica (ALU): está formada por los circuitos digitales necesarios para realizar las operaciones aritméticas y lógicas requeridas por las

instrucciones.

• Banco de Registros: contiene los registros que almacenan temporalmente los

datos y resultados con los que opera la ALU.

• Registros Especiales: contienen información necesaria para la correcta ejecución

de las instrucciones y del programa. Por ejemplo, la instrucción en ejecución

(registro de instrucciones, IR), la dirección de la siguiente instrucción a ejecutar

(contador de programa, PC), etc.

• Buses internos: son los caminos de conexión entre los distintos elementos que

forman la Unidad de Proceso.

Figura 4.18: Estructura del Camino de Datos

4.5. CONSTRUCCIÓN DEL CAMINO DE DATOS

25

Unidad de Control: se encarga de gestionar el secuenciamiento de las operaciones

que se realizan en el Camino de Datos para que las instrucciones se ejecuten adecuadamente. Este secuenciamiento se realiza generando en el orden correcto las señales

de control necesarias para coordinar el funcionamiento del resto de unidades del

computador. La unidad de control es un sistema secuencial y su complejidad depende básicamente de la complejidad del Camino de Datos y del número y tipo de

instrucciones a ejecutar.

En general, la ejecución de una instrucción se puede entender como un proceso dividido

en 5 pasos:

Captar la instrucción: El procesador debe leer la instrucción de la memoria.

Interpretar las instrucción: La instrucción debe decodificarse para determinar qué acción es necesaria.

Captar datos: La ejecución puede exigir leer datos de la memoria o de un módulo

de E/S.

Procesar datos: La ejecución de una instrucción puede exigir llevar a cabo alguna

operación aritmética o lógica.

Escribir datos: Los resultados de una ejecución pueden tener que ser escritos en la

memoria o en un módulo de E/S.

En las siguientes secciones estudiaremos como llevar a cabo el diseño de una Unidad

Central de Proceso (Camino de Datos y Unidad de Control). Para ello tomaremos como

ejemplo el procesador MIPS. En concreto, diseñaremos una Unidad Central de Proceso

para ejecutar el siguiente subconjunto del repertorio de instrucciones del MIPS:

Las instrucciones de acceso a memoria lw y sw

Las instrucciones aritmético-lógicas add, sub, and, or y slt

La instrucción de salto condicional beq

La instrucción de salto incondicional j

4.5.

Construcción del Camino de Datos

Una forma razonable de empezar el diseño de una Unidad Central de Proceso es la

construcción del Camino de Datos. Examinaremos para ello los componentes que serán

necesarios para la ejecución de cada una de las instrucciones. Utilizaremos tanto sistemas

combinacionales como secuenciales. Para los sistemas secuenciales asumiremos sincronización por flancos.

26

4.5.1.

TEMA 4. EL PROCESADOR

Carga de la instrucción

Para ejecutar cualquier instrucción se debe empezar por cargar la instrucción desde

memoria. La dirección de memoria nos la indica el registro de 32 bits contador de programa

(PC). Para ejecutar la siguiente instrucción el contador de programa ha de incrementarse

para que apunte 4 bytes más adelante. El Camino de Datos para este paso se muestra en

la figura 4.19.

Sumador

4

PC

Dirección

Instrucción

Memoria de

instrucciones

Figura 4.19: Parte del Camino de Datos correspondiente a la búsqueda de la instrucción

e incremento del contador de programa

4.5.2.

Instrucciones aritmético-lógicas

Las instrucciones aritmético-lógicas son instrucciones tipo R que leen dos registros,

operan con la ALU los contenidos de estos registros y escriben el resultado. El ejemplo

tı́pico de este tipo de instrucciones es add $t1, $t2, $t3, que suma los contenidos de

$t2 y $t3 y escribe el resultado en $t1. En la figura 4.20 se muestra el Camino de Datos

para estas instrucciones suponiendo que ya se ha obtenido la instrucción. Los registros

de 32 bits del procesador se agrupan en un banco de registros. Se puede acceder a cada

uno de los registros especificando su número. El banco de registros tiene dos puertos de

lectura y uno de escritura. Para escribir hay que activar explı́citamente la señal de control

de escritura. Las entradas que indican el número de registro a leer o escribir son todas de

5 bits, mientras que las salidas (lı́neas de datos) son de 32 bits.

Necesitaremos una ALU que pueda realizar las operaciones sumar, restar, AND, OR

y realizar la comparación set on less than (slt). El cuadro 4.2 muestra las lı́neas de

control de la ALU con las correspondientes operaciones. La ALU admitirá como entrada

dos operandos de 32 bits (a y b) y una lı́nea de control de tres bits para seleccionar la

operación a realizar. Ofrecerá como salida el resultado de la operación, también de 32 bits,

un bit de acarreo, una salida de detección de desbordamiento y una salida de detección de

cero como se ilustra en la figura 4.21. La salida Cero de la ALU se utilizará en la realización

de los saltos condicionales como veremos más adelante. La salida de Desbordamiento se

usará para la detección de excepciones.

4.5. CONSTRUCCIÓN DEL CAMINO DE DATOS

Reg. de

lectura 2

Reg. de

escritura

Dato a

escribir

3

REGISTROS

Instrucción

Reg. de

lectura 1

27

Dato

leído 1

Dato

leído 2

Operación de la ALU

ALU

Cero

Resultado

de la ALU

EscribirReg

Figura 4.20: Parte del Camino de Datos correspondiente a las instrucciones aritméticológicas (tipo R)

lı́neas de control de la ALU

000

001

010

110

111

función

and

or

suma

resta

slt

Cuadro 4.2: Valores de las tres lı́neas de control de la ALU y las operaciones correspondientes.

4.5.3.

Instrucciones de transferencia de datos

Las instrucciones de carga y almacenamiento son instrucciones tipo I con el siguiente

formato: lw $t1, desp1($t2) o sw $t1, desp1($t2). Estas instrucciones leen o escriben un dato en memoria. La dirección de memoria se calcula añadiendo al registro base

($t2) el campo de desplazamiento (positivo o negativo) de 16 bits contenido en la instrucción. El desplazamiento se extiende a 32 bits antes de realizar la suma en la ALU.

Si la instrucción es la sw, el dato a almacenar ha de leerse del registro $t1 del banco de

registros. En caso de lw, el valor leı́do de memoria debe escribirse en el registro $t1. La

figura 4.22 muestra el Camino de Datos para este tipo de instrucciones. Los identificadores de registros para el banco están en los campos de la instrucción, ası́ como el valor del

desplazamiento, el cual tras extender el signo se convierte en el segundo operando de la

ALU. La memoria de datos tiene señales de control de lectura y escritura, una entrada de

dirección, una entrada de datos para la escritura y una salida de datos para la lectura. La

señal de control de lectura de la memoria es necesaria para evitar el acceso a posiciones

no válidas.

28

TEMA 4. EL PROCESADOR

Figura 4.21: Sı́mbolo de la ALU

Reg. de

lectura 2

Reg. de

escritura

Dato a

escribir

3

REGISTROS

Instrucción

Reg. de

lectura 1

Dato

leído 1

Operación de la ALU

EscribirMem

ALU

Cero

Resultado

de la ALU

Dato

leído 2

Dato

leído

Memoria

de Datos

Dato a

escribir

EscribirReg

16

Dirección

Extensión

de signo

32

LeerMem

Figura 4.22: Parte del Camino de Datos correspondiente a las instrucciones de acceso a

memoria

4.5.4.

Instrucción de salto condicional

La instrucción beq es una instrucción tipo I con 3 operandos, dos registros y un

desplazamiento de 16 bits utilizado para calcular la dirección destino del salto. Su formato

es beq $t1, $t2, despl. Evalúa si el contenido de los registros $t1 y $t2 son iguales,

si la condición se cumple aplica un salto relativo a la dirección de la instrucción con

signo. Es la dirección PC+4 la que se utilizará como base para el cálculo de la dirección

destino. Para realizar esta instrucción se ha de calcular la dirección destino del salto:

(PC+4)+4*despl. Los 16 bits del campo desplazamiento se extienden a 32 y se desplazan

a la izquierda 2 posiciones para multiplicar por 4. Además de calcular la dirección de

salto, se tiene que determinar si se realiza el salto o no. Si la condición se cumple, es

decir, los dos operandos son iguales, la dirección de salto calculada pasa a ser el nuevo

PC. Si los operandos son diferentes, el PC+4 deberı́a reemplazar al actual. La figura 4.23

muestra el Camino de Datos para esta instrucción. Para calcular la dirección de salto se

4.5. CONSTRUCCIÓN DEL CAMINO DE DATOS

29

incluye una unidad de extensión de signo y un sumador. Para la comparación se necesita

utilizar el banco de registros y la ALU. A la ALU entran los dos datos a comparar, la

señal de control de la ALU se configura para hacer una resta, de esta forma si son iguales

se activará la salida Cero de la ALU.

PC +4 del camino de datos de instrucciones

Resultado

Desp.

2 bits a

la izq.

Reg. de

lectura 2

Reg. de

escritura

Dato a

escribir

Sumador

3

REGISTROS

Instrucción

Reg. de

lectura 1

Destino salto

Operación de la ALU

Dato

leído 1

Cero

Dato

leído 2

Decidir si se

hace el salto

ALU

EscribirReg

16

Extensión

de signo

32

Figura 4.23: Parte del Camino de Datos correspondiente a la instrucción de salto condicional (beq)

4.5.5.

Instrucción de salto incondicional

La instrucción de salto incondicional (j) es una instrucción tipo J con un modo de

direccionamiento pseudodirecto. Esta instrucción reemplaza los 28 bits de menor peso del

PC con los 26 bits de menor peso de la instrucción desplazados 2 bits hacia la izquierda.

No se necesita hardware adicional para llevar a cabo esta instrucción.

4.5.6.

Camino de Datos completo

El Camino de Datos necesario para la ejecución del subconjunto de instrucciones elegido estará formado por la combinación de los elementos explicados en las subsecciones

anteriores. Como hemos visto en la sección 4.4, la ejecución de una instrucción la podemos dividir en 5 pasos, correspondiendo cada uno de ellos a diferentes operaciones de

las unidades funcionales requeridas. Cada paso lo vamos a ejecutar en un ciclo de reloj

diferente, de esta forma podremos utilizar una determinada unidad funcional más de una

vez en una instrucción siempre y cuando se haga en ciclos diferentes, reduciendo ası́ la

30

TEMA 4. EL PROCESADOR

cantidad de hardware empleado. Ası́ por ejemplo, las sumas realizadas para calcular la

siguiente instrucción a ejecutar (ver figuras 4.19 y 4.23) se pueden realizar con la ALU

y no se necesitan sumadores independientes para esa operación. La ALU llevará a cabo

diferentes operaciones dependiendo de la instrucción que se ejecute y del ciclo de ejecución

en el que nos encontremos:

Cuando se realice la carga de la instrucción, sumará el PC+4 para incrementar el

contador del programa y que este apunte a la siguiente instrucción a ejecutar.

En el caso de instrucción de carga/almacenamiento, calculará la dirección de memoria sobre la que leer o escribir sumando a un operando almacenado en registro el

campo desplazamiento con el signo extendido.

En el caso de instrucción tipo R, realizará una operación aritmética o lógica (and,

or, add, sub y slt) con 2 operandos almacenados en los registros.

En el caso de salto condicional, evaluará la condición de salto restando 2 operandos

almacenados en los registros. También calculará la dirección de salto sumando al PC

incrementado los 16 bits menos significativos de la instrucción con el signo extendido

y desplazados dos bits a la izquierda.

Del mismo modo, no se necesita una memoria para instrucciones y otra para datos, ya

que el acceso a la memoria de instrucciones y a la de datos se realiza en ciclos diferentes

de la ejecución.

P

C

Memoria

Registro de

instrucciones

Reg. de

lectura 2

Dirección

Instrucciones

o datos

Dato

Reg. de

lectura 1

Reg. de

escritura

Registro de

datos de

memoria

Dato a

escribir

REGISTROS

Al finalizar cada ciclo todos los datos que vayan a utilizarse en el siguiente ciclo se

deben almacenar en un elemento de almacenamiento (memoria o registro). Los datos a

utilizar por las siguientes instrucciones en ciclos posteriores se almacenarán en elementos

de almacenamiento visibles al programador (el banco de registros, el PC o la memoria).

En cambio, los datos que va utilizar la misma instrucción en ciclos posteriores deben

guardarse en registros temporales.

Dato

leído 1

A

ALU

Dato

leído 2

Salida

ALU

B

Figura 4.24: Visión de alto nivel del Camino de Datos del MIPS

La figura 4.24 muestra una visión de alto nivel del Camino de Datos completo. En

este diseño se utiliza una única ALU en vez de una ALU y dos sumadores, una memoria

4.5. CONSTRUCCIÓN DEL CAMINO DE DATOS

31

única para instrucciones y datos, y se han añadido registros temporales tras cada unidad

funcional para almacenar la salida de dicha unidad hasta que este valor vaya a utilizarse

en el siguiente ciclo. En concreto, se han añadido los siguientes registros temporales:

El registro de instrucción (IR) y el registro de datos de memoria (MDR) se añaden

para almacenar la salida de la memoria tras la lectura de una instrucción o un dato,

respectivamente. Se utilizan dos registros separados, ya que, como se verá más tarde,

ambos valores se necesitarán en un mismo ciclo.

Los registros A y B se utilizan para guardar los valores de los registros operandos

leı́dos del banco de registros.

El registro SalidaALU almacena la salida de la ALU.

Todos los registros, excepto el IR, guardan datos entre dos ciclos de reloj consecutivos

y por tanto no necesitarán señal de escritura. El IR sı́ necesita conservar la instrucción

hasta el final de su ejecución y por lo tanto sı́ requiere de esa señal de control.

Debido a que se utilizarán varias unidades funcionales para diferentes propósitos,

será necesario introducir multiplexores para poder escoger entre diferentes entradas. Se

necesita un MUX para seleccionar:

el origen de la dirección de acceso a memoria (el PC para acceder a instrucciones,

el registro SalidaALU para acceder a datos).

el registro de destino, que estará indicado por los bits 16-20 (rt) en los casos de instrucciones de carga y por los bits 11-15 (rd) en los casos de instrucciones aritméticológicas.

el dato a escribir, que será un dato de la memoria en el caso de instrucciones de

carga y la salida de la ALU en el caso de instrucciones aritmético-lógicas.

la primera entrada de la ALU, que podrá ser el registro A o el PC.

la segunda entrada de la ALU, que podrá ser el registro B (en el caso de instrucción

aritmética lógica o instrucción de salto condicional), el número 4 (utilizado para

incrementar el PC), el campo desplazamiento con el signo extendido (en el caso

de instrucciones de transferencia de datos) o el campo desplazamiento con el signo

extendido y desplazado 2 bits a la izquierda (para el cálculo de la dirección destino

en los saltos condicionales).

la dirección de la siguiente instrucción a ejecutar, que se almacenará en PC y que

podrá ser PC+4, la dirección de salto calculada por la ALU en caso de salto condicional o la dirección de salto indicada en la propia instrucción en caso de salto

incondicional. En este último caso, la dirección destino se obtiene mediante el desplazamiento de los 26 bits de menor peso de la instrucción 2 bits a la izquierda

(añadiendo 00 como bits de menor peso) y concatenando los 4 bits de mayor peso

de PC+4 como bits de mayor peso.

32

TEMA 4. EL PROCESADOR

La figura 4.25 muestra el Camino de Datos completo para ejecutar las instrucciones

básicas del MIPS.

0

1

Desp. 28

2 bits a

la izq.

26

Instrucción [25-0]

Salto

incond. [31-0]

M

u

x

2

PC [31-28]

0

M

u

1x

Memoria

Dirección

Instrucciones

o datos

Datos

Reg. de

lectura 1

Instrucción

[20-16]

Reg. de

lectura 2

Instrucción

[15-0]

Registro de

instrucción

Instr.

[15-0]

Registro

de datos de

memoria

0

M

Instr.

u

[15-11]

1x

REGISTROS

P

C

Instrucción

[25-21]

Reg. de

escritura

Dato a

escribir

0

Dato

leído 1

Dato

leído 2

B

0

4

0

M

u

1x

16

M

u

1x

A

M

1

u

2

x

ALU

Cero

Resultado

ALU

Salida

ALU

3

Exten.

signo 32

Desp.

2 bits a

la izq.

Figura 4.25: Camino de Datos para ejecutar las instrucciones básicas del MIPS

El primer paso en la ejecución de una instrucción es común a todas las instrucciones y

consiste en el almacenamiento de la instrucción a ejecutar en el registro de instrucción. Se

envı́a el PC a memoria como dirección, se efectúa la lectura de la instrucción y se escribe

en el registro de instrucciones (IR).También se incrementa el PC en cuatro para apuntar

a la siguiente instrucción a ejecutar. La figura 4.26 muestra la parte del Camino de Datos

que se utiliza. Debido a que nuestro diseño utiliza sincronización por flanco, se puede leer

el contenido de un registro que se vaya a escribir ya que el nuevo valor no será accesible

hasta el siguiente ciclo de reloj. En este caso, el incremento del PC y la búsqueda de la

instrucción puede realizarse en paralelo ya que el nuevo valor del PC no será visible hasta

el siguiente ciclo.

A continuación describiremos como se utiliza este Camino de Datos para cada una de

las instrucciones consideradas.

Instrucciones aritmético-lógicas

Si la instrucción a ejecutar es una instrucción aritmético lógica, el siguiente paso será la

búsqueda de los registros con los operandos, la ejecución de la operación aritmético-lógica

sobre los operandos y la escritura del resultado en el registro destino.

La figura 4.27 muestra la parte del Camino de Datos que se utiliza para la búsqueda de

los registros. En esta etapa se leen los dos registros indicados por rs y rt y se almacenan

en los registros temporales A y B.

4.5. CONSTRUCCIÓN DEL CAMINO DE DATOS

33

0

1

Desp. 28

2 bits a

la izq.

26

Instrucción [25-0]

Salto

incond. [31-0]

M

u

x

2

PC [31-28]

0

M

u

1x

Memoria

Dirección

Instrucciones

o datos

Datos

Reg. de

lectura 1

Instrucción

[20-16]

Reg. de

lectura 2

Instrucción

[15-0]

Registro de

instrucción

Instr.

[15-0]

Registro

de datos de

memoria

0

M

Instr.

u

[15-11]

1x

REGISTROS

P

C

Instrucción

[25-21]

Reg. de

escritura

Dato a

escribir

0

Dato

leído 1

M

u

1x

A

Dato

leído 2

B

Cero

Resultado

ALU

0

4

0

M

u

1x

16

ALU

M

1

u

2

x

Salida

ALU

3

Exten.

signo 32

Desp.

2 bits a

la izq.

Figura 4.26: Camino de Datos: etapa de carga de la instrucción

0

1

Desp. 28

2 bits a

la izq.

26

Instrucción [25-0]

Salto

incond. [31-0]

M

u

x

2

PC [31-28]

0

M

u

1x

Memoria

Dirección

Instrucciones

o datos

Datos

Reg. de

lectura 1

Instrucción

[20-16]

Reg. de

lectura 2

Instrucción

[15-0]

Registro de

instrucción

Instr.

[15-0]

Registro

de datos de

memoria

0

Instr.

[15-11]

M

u

1x

REGISTROS

P

C

Instrucción

[25-21]

Reg. de

escritura

Dato a

escribir

0

Dato

leído 1

Dato

leído 2

B

0

4

0

M

u

1x

16

M

u

1x

A

M

1

u

2

x

ALU

Cero

Resultado

ALU

Salida

ALU

3

Exten.

signo 32

Desp.

2 bits a

la izq.

Figura 4.27: Camino de Datos: búsqueda de registros (instrucción tipo R e instrucción

sw)

34

TEMA 4. EL PROCESADOR

La figura 4.28 muestra en rojo la parte del Camino de Datos que se utiliza para la

ejecución de la operación y en rosa lo que se utiliza de ciclos anteriores. En esta etapa

la ALU lleva a cabo la operación especificada en el código de función sobre los datos

almacenados en A y B en el ciclo anterior y almacena el resultado en el registro SalidaALU.

0

1

Desp. 28

2 bits a

la izq.

26

Instrucción [25-0]

Salto

incond. [31-0]

M

u

x

2

PC [31-28]

0

M

u

1x

Memoria

Dirección

Instrucciones

o datos

Datos

Reg. de

lectura 1

Instrucción

[20-16]

Reg. de

lectura 2

Instrucción

[15-0]

Registro de

instrucción

Instr.

[15-0]

Registro

de datos de

memoria

0

M

Instr.

u

[15-11]

1x

REGISTROS

P

C

Instrucción

[25-21]

Reg. de

escritura

Dato a

escribir

0

Dato

leído 1

M

u

1x

A

Dato

leído 2

B

Cero

Resultado

ALU

0

4

0

M

u

1x

16

ALU

M

1

u

2

x

Salida

ALU

3

Exten.

signo 32

Desp.

2 bits a

la izq.

Figura 4.28: Camino de Datos: instrucción tipo R, ejecución

La figura 4.29 muestra en rojo la parte del Camino de Datos que se utiliza para escribir

el resultado (almacenado en el ciclo anterior en el registro SalidaALU) en el registro destino

especificado por el campo rd de la instrucción (bits 15-11).

0

1

Desp. 28

2 bits a

la izq.

26

Instrucción [25-0]

Salto

incond. [31-0]

M

u

x

2

PC [31-28]

0

M

u

1x

Memoria

Dirección

Instrucciones

o datos

Datos

Reg. de

lectura 1

Instrucción

[20-16]

Reg. de

lectura 2

Instrucción

[15-0]

Registro de

instrucción

Instr.

[15-0]

Registro

de datos de

memoria

0

M

Instr.

u

[15-11]

1x

REGISTROS

P

C

Instrucción

[25-21]

Reg. de

escritura

Dato a

escribir

0

Dato

leído 1

Dato

leído 2

B

0

4

0

M

u

1x

16

M

u

1x

A

M

1

u

2

x

ALU

Cero

Resultado

ALU

3

Exten.

signo 32

Desp.

2 bits a

la izq.

Figura 4.29: Camino de Datos: instrucción tipo R, escritura de resultado

En total, este tipo de instrucciones necesitarán 4 ciclos de reloj para ejecutarse.

Salida

ALU

4.5. CONSTRUCCIÓN DEL CAMINO DE DATOS

35

Instrucción lw

Si la instrucción a ejecutar es un load (lw $t1, desp1($t2)) el siguiente paso a la

carga de la instrucción será el cálculo de la dirección de memoria a leer, la lectura del

dato y el almacenamiento del mismo en el registro destino.

La dirección de memoria se calcula sumando al registro base ($t2) el campo desplazamiento. Por tanto, antes de calcular la dirección de memoria tendremos que leer

el registro base y almacenarlo en el registro temporal A para poder operar con él. La

figura 4.30 muestra el Camino de Datos utilizado para esta operación.

0

1

Desp. 28

2 bits a

la izq.

26

Instrucción [25-0]

Salto

incond. [31-0]

M

u

x

2

PC [31-28]

0

M

u

1x

Memoria

Dirección

Instrucciones

o datos

Datos

Instrucción

[25-21]

Reg. de

lectura 1

Instrucción

[20-16]

Instrucción

[15-0]

Registro de

instrucción

Instr.

[15-0]

Registro

de datos de

memoria

REGISTROS

P

C

Reg. de

lectura 2

0

Instr.

[15-11]

M

u

1x

Reg. de

escritura

Dato a

escribir

0

Dato

leído 1

Dato

leído 2

B

0

4

0

M

u

1x

16

M

u

1x

A

M

1

u

2

x

ALU

Cero

Resultado

ALU

Salida

ALU

3

Exten.

signo 32

Desp.

2 bits a

la izq.

Figura 4.30: Camino de Datos: instrucción lw, búsqueda de registro

La figura 4.31 muestra la parte del Camino de Datos que se utiliza para calcular la

dirección de memoria utilizando el dato almacenado en el registro A en el ciclo anterior.

A continuación se accede a memoria y se carga una palabra en el registro MDR. La

dirección de memoria que se utiliza se ha calculado en el ciclo anterior y se encuentra

almacenada en SalidaALU. La figura 4.32 muestra en rojo la parte del Camino de Datos

que se utiliza y en rosa lo que se utiliza de ciclos anteriores.

Las instrucción se completa escribiendo el valor leı́do de memoria, almacenado en el

ciclo anterior en el registro MDR, en el banco de registros. La figura 4.33 muestra en rojo

la parte del Camino de Datos que se utiliza en esta etapa y en rosa lo que se utiliza de

ciclos anteriores.

Esta instrucción necesita un total de 5 ciclos de reloj para completarse.

36

TEMA 4. EL PROCESADOR

0

1

Desp. 28

2 bits a

la izq.

26

Instrucción [25-0]

Salto

incond. [31-0]

M

u

x

2

PC [31-28]

0

M

u

1x

Memoria

Dirección

Instrucciones

o datos

Datos

Reg. de

lectura 1

Instrucción

[20-16]

Reg. de

lectura 2

Instrucción

[15-0]

Registro de

instrucción

Instr.

[15-0]

Registro

de datos de

memoria

0

M

Instr.

u

[15-11]

1x

REGISTROS

P

C

Instrucción

[25-21]

Reg. de

escritura

Dato a

escribir

0

Dato

leído 1

M

u

1x

A

Dato

leído 2

B

Cero

Resultado

ALU

0

4

0

M

u

1x

16

ALU

M

1

u

2

x

Salida

ALU

3

Exten.

signo 32

Desp.

2 bits a

la izq.

Figura 4.31: Camino de Datos: instrucción lw, cálculo de la dirección de memoria

0

1

Desp. 28

2 bits a

la izq.

26

Instrucción [25-0]

Salto

incond. [31-0]

M

u

x

2

PC [31-28]

0

M

u

1x

Memoria

Dirección

Instrucciones

o datos

Datos

Instrucción

[25-21]

Reg. de

lectura 1

Instrucción

[20-16]

Instrucción

[15-0]

Registro de

instrucción

Instr.

[15-0]

Registro

de datos de

memoria

REGISTROS

P

C

Reg. de

lectura 2

0

Instr.

[15-11]

M

u

1x

Reg. de

escritura

Dato a

escribir

0

Dato

leído 1

Dato

leído 2

A

B

0

4

0

M

u

1x

16

M

u

1x

M

1

u

2

x

ALU

Cero

Resultado

ALU

3

Exten.

signo 32

Desp.

2 bits a

la izq.

Figura 4.32: Camino de Datos: instrucción lw, lectura de memoria

Salida

ALU

4.5. CONSTRUCCIÓN DEL CAMINO DE DATOS

37

0

1

Desp. 28

2 bits a

la izq.

26

Instrucción [25-0]

Salto

incond. [31-0]

M

u

x

2

PC [31-28]

0

M

u

1x

Memoria

Dirección

Instrucciones

o datos

Datos

Reg. de

lectura 1

Instrucción

[20-16]

Reg. de

lectura 2

Instrucción

[15-0]

Registro de

instrucción

Instr.

[15-0]

Registro

de datos de

memoria

0

M

Instr.

u

[15-11]

1x

REGISTROS

P

C

Instrucción

[25-21]

Reg. de

escritura

Dato a

escribir

0

Dato

leído 1

Dato

leído 2

M

u

1x

A

B

0

4

0

M

u

1x

16

M

1

u

2

x

ALU

Cero

Resultado

ALU

Salida

ALU

3

Exten.

signo 32

Desp.

2 bits a

la izq.