Microarquitectura del CPU

Anuncio

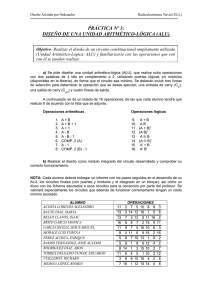

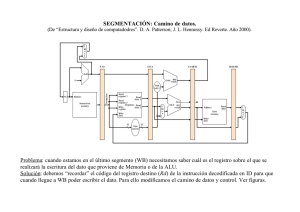

Organización del Computador I Microarquitectura del CPU Matı́as Introducción A1 B1 ADD R1, R0 ¿−→? Σ SS Ae A2 A3 Σ S Ae A3 B3 Ae A4 B4 C3 As Σ S C2 As Σ S C1 As As C4 C5 El lenguaje NEG_on NEG_off NEG I Podemos activar señales NEG on : niega los bits de la entrada y los pone a la salida NEG off : pasa los bits sin modificarlos El lenguaje HAB. D SET s3 Q Q CLR HAB. D I Podemos ver alguna parte especı́fica de un registro y usarla para algo... SET s2 Q Q CLR HAB. D SET s1 Q Q CLR HAB. D WriteEnable Q CLR Reset Vale R0[3] SET Q Enable out s0 El lenguaje I Existen caminos (lı́neas) por donde van los datos. I Podemos mover un dato de un registro a otro si hay un camino directo entre ellos I Podemos asignar un valor constante (almacenada) a un registro. R0 R_OUT R1 0xF0CA Vale R1:= R0 R OUT:=R0 . . . No vale R0:=R OUT R1:=R OUT R0:=0xF0CA R1:=x Componentes 0xF0CA 0x0000 CMP_f0ca CMP_0000 I Podemos hacer un comparador CMP_1 CMP 1 := R3 CMP 0000 CMP_2 COMP EQ_cmp El lenguaje I Podemos analizar un bit y actuar en consecuencia if EQ cmp=0 R OUT:=R3 else R OUT:=R2 endif Ejercicio 1 Se cuentan con los siguientes circuitos: I Una ALU con 2 registros de 16 bits (ALU IN1 y ALU IN2) que usa de entradas y 5 registros que usa de salida: ALU OUT de 16 bits y (ALU Z, ALU N, ALU C y ALU V) de 1 bit. Sus señales de control son: Señal ALUadd ALUsub ALUneg ALUand ALUnot Efecto ALU OUT ALU OUT ALU OUT ALU OUT ALU OUT := := := := := ALU IN1 + ALU IN2 ALU IN1 - ALU IN2 - ALU IN1 ALU IN1 AND ALU IN2 NOT ALU IN1 I Un extensor de signo complemento a 2 (SIGN EXT) con un registro de entrada de 16 bits (EXT IN) y un registro de salida de 16 bits (EXT OUT). Sus señales de control son: Señal Efecto SIGN EXTon activa la operación de extensión de signo de 8 bits a 16 bits SIGN EXToff copia el contenido de EXT IN en EXT OUT 1) Suponiendo que se encuentra resuelta la decodificación y el acceso a memoria de la máquina, diseñar el camino de datos de la arquitectura de la máquina ORGA1. No dibujar la unidad de control para simplificar el diagrama. Ejercicio 1 Se cuentan con los siguientes circuitos: I Una ALU con 2 registros de 16 bits (ALU IN1 y ALU IN2) que usa de entradas y 5 registros que usa de salida: ALU OUT de 16 bits y (ALU Z, ALU N, ALU C y ALU V) de 1 bit. Sus señales de control son: Señal ALUadd ALUsub ALUneg ALUand ALUnot Efecto ALU OUT ALU OUT ALU OUT ALU OUT ALU OUT := := := := := ALU IN1 + ALU IN2 ALU IN1 - ALU IN2 - ALU IN1 ALU IN1 AND ALU IN2 NOT ALU IN1 I Un extensor de signo complemento a 2 (SIGN EXT) con un registro de entrada de 16 bits (EXT IN) y un registro de salida de 16 bits (EXT OUT). Sus señales de control son: Señal Efecto SIGN EXTon activa la operación de extensión de signo de 8 bits a 16 bits SIGN EXToff copia el contenido de EXT IN en EXT OUT 2) Indicar cuál es la secuencia de señales (o microoperaciones) que debe realizar la unidad de control para ejecutar las siguientes instrucciones: I I I MOV R5, R1 AND R7, R1 NEG R4 Ejercicio 1 - Solución SIGN_EXT_on SIGN_EXT_off EXT_IN R0 ... R7 SIGN_EXT EXT_OUT SP PC ALU_IN2 ALU_IN1 ALU_Z Z N V ALU ALU_add ALU_sub ALU_neg ALU_and ALU_not ALU_N ALU_V ALU_C C ALU_OUT CPU Orga1 Ejercicio 1 - Solución I 16 bits: R0, .., R7, SP, PC, EXT IN, EXT OUT, ALU IN1, ALU IN2, ALU OUT I 1 bit: Z, N, V, C, ALU Z, ALU N, ALU V, ALU C I Bus interno: 16 lı́neas. I Los flags están conectados a las 4 lı́neas menos significativas del bus. Ejercicio 1 - Solución: Secuencias de microoperaciones I MOV R5,R1 1. R5 := R1 I AND R7, R1 1. 2. 3. 4. 5. 6. 7. 8. ALU IN1 := R7 ALU IN2 := R1 ALUand R7 := ALU OUT Z := ALU Z N := ALU N C := ALU C V := ALU V I NEG R4 1. 2. 3. 4. 5. 6. 7. ALU IN1 := R4 ALUneg R4 := ALU OUT Z := ALU Z N := ALU N C := ALU C V := ALU V Ejercicio 2 Se cuenta con una memoria con palabra y direccionamiento de 16 bits. La misma está conectada por medio de un bus a la CPU. En la CPU se agrega un controlador de bus que cuenta con 2 registros de entrada de 16 bits (ADDR, WRT DATA) y 1 de salida de 16 bits (RD DATA). Sus señales de control son: I MEM WRITE: Lanza el protocolo de escritura del contenido del registro WRT DATA en la dirección de memoria indicada por el ADDR I MEM READ: Lanza el protocolo de lectura del contenido de la dirección de memoria indicada por el ADDR, colocando el valor en el registro RD DATA. 1. Extender el camino de datos de la arquitectura de la máquina ORGA1 para poder utilizar la memoria. No dibujar la unidad de control para simplificar el diagrama. 2. Indicar cuál es la secuencia de señales (o microoperaciones) que debe realizar la unidad de control para ejecutar las siguientes instrucciones: I I I I I MOV R2, R5 MOV R2, [R5] MOV R2, [0xFF00] MOV [0xFF00], [0xFF01] JE 0xFF Ejercicio 2: Solución 0x0001 .... .... ADDR IR0 WRT_DATA IR1 RD_DATA IR2 CPU Orga1 MEM_READ MEM_WRITE Controlador del Bus bus externo Memoria Ejercicio 2 - Solución: secuencias de microoperaciones I I MOV R2, R5 1. 2. 3. 4. 5. 1. R2 := R5 I MOV R2, [R5] 1. ADDR := R5 2. MEM READ 3. R2 := RD DATA I MOV R2, [0xFF00] 1. ADDR := IR1 2. MEM READ 3. R2 := RD DATA MOV [0xFF00], [0xFF01] I ADDR := IR2 MEM READ WRT DATA := RD DATA ADDR := IR1 MEM WRITE JE 0xFF 1. IF Z = 0 2. EXT IN := IR0 3. SIGN EXT on 4. ALU IN 1 := PC 5. ALU IN 2 := EXT OUT 6. ALU add 7. PC := ALU OUT Ejercicio 3 La computadora STACK1 es una máquina de pila con direccionamiento a byte, tamaño de palabra de 16 bits y direcciones de memoria de 12 bits. Trabaja con aritmética complemento a 2 de 16 bits. Posee el siguiente set de instrucciones: Instrucción PUSH [M] POP [M] ADD SUB JUMP SKIP N SKIP Z SKIP GE CodOp 0000 0001 0010 0011 0100 0101 0110 0111 Significado push [X] [X] := pop push(pop+pop) push(pop-pop) PC := pop (sólo los 12 bits menos significativos) ignora la próxima instrucción si top es < 0 ignora la próxima instrucción si top es 0 ignora la próxima instrucción si top es >= 0 El formato de instrucción de STACK1 es el que sigue: CodOp 4 bits Dirección 12 bits 1) Definir el camino de datos y la organización del CPU de STACK1 para soportar la implementación de, al menos, estas instrucciones. 2) Describa la secuencia de microoperaciones que realiza la unidad de control para realizar un fetch de una instrucción. 3) Implementar las siguientes instrucciones: i) JUMP ii) SKIP Z iii) PUSH [X] iv) ADD Ejercicio 3: Solución Se utiliza un circuito incrementador con 2 señales: INC +2 que suma 2 a la entrada, y INC −2 que resta 2 a la entrada. I 12 bits: SP, PC, INC IN, INC OUT, ADDR. I 16 bits: WRT DATA, RD DATA, IR, ALU IN1, ALU IN2, ALU OUT, CMP 1. I 1 bit: EQ cmp ALU_IN2 SP PC ALU_IN1 IR MEM_READ MEM_WRITE ALU ADDR Memoria bus externo WRT_DATA ALU_add ALU_sub RD_DATA Controlador del Bus CMP_1 ALU_OUT 0x0000 INC_IN INC COMP INC_OUT CMP_0000 EQ_cmp INC_+2 INC_­2 CPU STACK1 Ejercicio 3 - Solución: fetch 1. ADDR := PC 2. MEM READ 3. IR := RD DATA // cargo el IR 4. INC IN := PC 5. INC +2 6. PC := INC OUT // incremento PC Ejercicio 3 - Solución: secuencia de microoperaciones I SKIP Z I JUMP 1. 2. 3. 4. 5. 6. INC IN := SP INC +2 SP := INC OUT ADDR := SP MEM READ PC := RD DATA[11:0] 1. 2. 3. 4. 5. 6. 7. 8. 9. 10. 11. INC IN := SP INC +2 ADDR := INC OUT MEM READ CMP 1 := RD DATA CMP 0000 if EQ cmp = 1 INC IN := PC INC +2 PC := INC OUT endif Ejercicio 3 - Solución: secuencia de microoperaciones I PUSH [X] 1. ADDR := IR[11:0] 2. MEM READ 3. WRT DATA := RD DATA 4. ADDR := SP 5. MEM WRITE 6. INC IN := SP 7. INC −2 8. SP := INC OUT I ADD 1. 2. 3. 4. 5. 6. 7. 8. 9. 10. 11. 12. 13. 14. 15. 16. 17. 18. 19. INC IN := SP INC +2 SP := INC OUT ADDR := SP MEM READ ALU IN1 := RD DATA // primer operando INC IN := SP INC +2 SP := INC OUT ADDR := SP MEM READ ALU IN2 := RD DATA // segundo operando ALU add WRT DATA := ALU OUT ADDR := SP MEM WRITE // push resultado INC IN := SP INC −2 SP := INC OUT Cómo sigue Orga1... Con lo visto hoy pueden hacer toda la práctica 7. I Jueves: taller de Microprogramación