PUERTO SERIAL

Anuncio

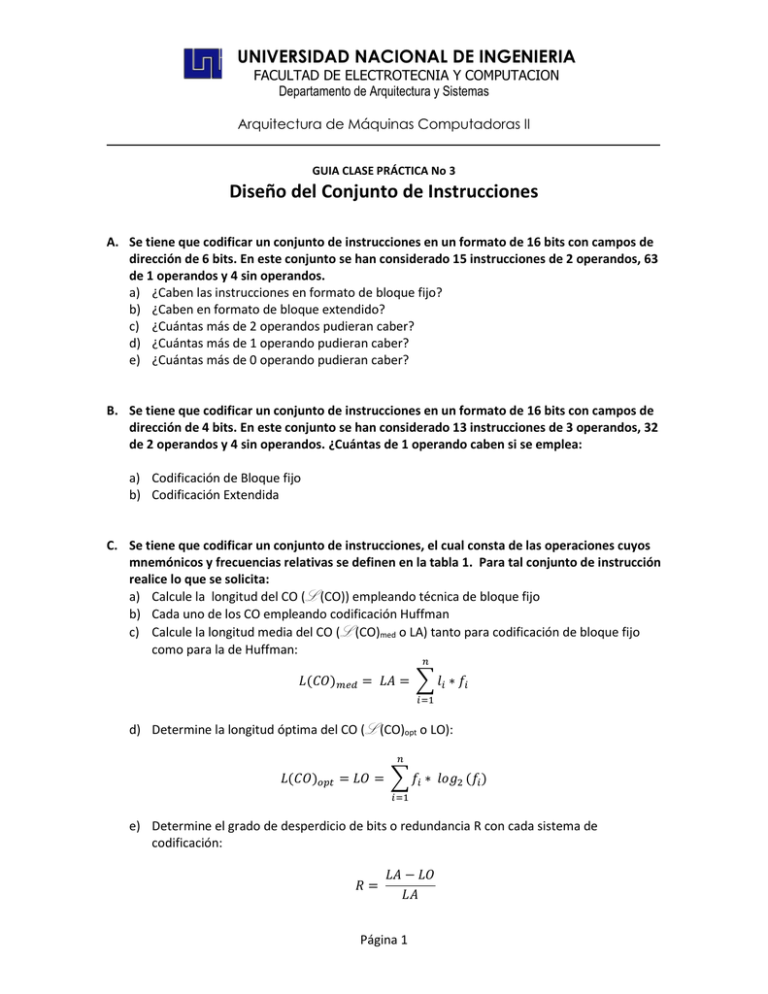

UNIVERSIDAD NACIONAL DE INGENIERIA FACULTAD DE ELECTROTECNIA Y COMPUTACION Departamento de Arquitectura y Sistemas Arquitectura de Máquinas Computadoras II GUIA CLASE PRÁCTICA No 3 Diseño del Conjunto de Instrucciones A. Se tiene que codificar un conjunto de instrucciones en un formato de 16 bits con campos de dirección de 6 bits. En este conjunto se han considerado 15 instrucciones de 2 operandos, 63 de 1 operandos y 4 sin operandos. a) ¿Caben las instrucciones en formato de bloque fijo? b) ¿Caben en formato de bloque extendido? c) ¿Cuántas más de 2 operandos pudieran caber? d) ¿Cuántas más de 1 operando pudieran caber? e) ¿Cuántas más de 0 operando pudieran caber? B. Se tiene que codificar un conjunto de instrucciones en un formato de 16 bits con campos de dirección de 4 bits. En este conjunto se han considerado 13 instrucciones de 3 operandos, 32 de 2 operandos y 4 sin operandos. ¿Cuántas de 1 operando caben si se emplea: a) Codificación de Bloque fijo b) Codificación Extendida C. Se tiene que codificar un conjunto de instrucciones, el cual consta de las operaciones cuyos mnemónicos y frecuencias relativas se definen en la tabla 1. Para tal conjunto de instrucción realice lo que se solicita: a) Calcule la longitud del CO (L (CO)) empleando técnica de bloque fijo b) Cada uno de los CO empleando codificación Huffman c) Calcule la longitud media del CO (L (CO)med o LA) tanto para codificación de bloque fijo como para la de Huffman: 𝑛 𝐿(𝐶𝑂)𝑚𝑒𝑑 = 𝐿𝐴 = ∑ 𝑙𝑖 ∗ 𝑓𝑖 𝑖=1 d) Determine la longitud óptima del CO (L (CO)opt o LO): 𝑛 𝐿(𝐶𝑂)𝑜𝑝𝑡 = 𝐿𝑂 = ∑ 𝑓𝑖 ∗ 𝑙𝑜𝑔2 (𝑓𝑖 ) 𝑖=1 e) Determine el grado de desperdicio de bits o redundancia R con cada sistema de codificación: 𝑅= 𝐿𝐴 − 𝐿𝑂 𝐿𝐴 Página 1 UNIVERSIDAD NACIONAL DE INGENIERIA FACULTAD DE ELECTROTECNIA Y COMPUTACION Departamento de Arquitectura y Sistemas Arquitectura de Máquinas Computadoras II Tabla 1. Conjunto de instrucciones con su frecuencia relativa mnemónicos MOV ADD SUB AND JMP INT CALL NOT CO f 0.25 0.25 0.125 0.125 0.0625 0.0625 0.0625 0.0625 D. Suponga que tiene una máquina con un formato de 2 direcciones de 6 bits cada uno y el CO está en bloque fijo de 4 bits. Su conjunto de instrucciones tiene 14 instrucciones y los modos se codifican según la tabla 1. La máquina tiene 8 registros enumerados de R0 a R7. a) Asigne código a las operaciones siguientes: ADD, SUB, JNZ y MOV b) Codifique en binario las instrucciones siguientes: ADD (R4)+, 1000H(R6) SUB (R3), (-(R7)) JNZ R5 MOV (R4)+, (1000H(R6)) Tabla 1.: Modos de Direccionamiento Modo Registro Directo Indirecto Autoincremento Directo Indirecto Autodecremento Directo Indirecto Indice Directo Indirecto Operando Fuente Código de operación (CO) 15 14 13 Código 000 001 010 011 100 101 110 111 Mf 12 11 10 Operando Destino Rf 9 8 7 Md 6 Formato de la Instrucción Página 2 5 4 Rd 3 2 1 0 UNIVERSIDAD NACIONAL DE INGENIERIA FACULTAD DE ELECTROTECNIA Y COMPUTACION Departamento de Arquitectura y Sistemas Arquitectura de Máquinas Computadoras II E. Llene la matriz de comparación de los modos de direccionamiento y arquitecturas poniendo palomilla () o tacha () en dependencia si el modo aplica o no para esa arquitectura. Posteriormente, analice cuál arquitectura soporta más modos y cuál menos. Con base en los conocimientos adquiridos en clase, justifique el porqué de sus hallazgos. Acumulador Pila Registros 2 dir. Registros 3 dir. Inmediato Registro Absoluto Indirecto de Registro Autoincremento Autodecremento Indice Relativo al PC F. Escriba una rutina en código en ensamblador de 2 direcciones de la arquitectura estudiada en clase, para cada una de las tareas descritas en la lista a continuación, tratando de aplicar lo más posible los modos de direccionamiento estudiados: 1. Multiplicación de dos enteros por sumas sucesivas. Considere que los factores deben estar en los registros R1 y R2 y el resultado debe quedar en R3. 2. División de dos enteros por restas sucesivas. Considere que el dividendo debe estar en el registro R1 y el divisor en R2. El cociente debe quedar en R3 y el residuo en R1. 3. Determinar si un arreglo de caracteres es palíndromo. Considere que el arreglo de caracteres se almacena en una variable de memoria con nombre “cadena”. El resultado debe quedar en R1: 1 si es palíndromo y 0 si no lo es. 4. Invertir una cadena. Considere que la cadena reside en un arreglo de caracteres en una variable de memoria con nombre “cadena”. 5. Dados dos arreglos A y B, los sume y guarde el resultado en uno de ellos. 6. Genere los primeros “n” valores de la serie Fibonacci en un arreglo de enteros almacenado en la variable de memoria “Fibonacci”. Considere que el valor de n está almacenado en R1. Página 3 UNIVERSIDAD NACIONAL DE INGENIERIA FACULTAD DE ELECTROTECNIA Y COMPUTACION Departamento de Arquitectura y Sistemas Arquitectura de Máquinas Computadoras II G. La serie de instrucciones descritas abajo, corresponden a una rutina. Esta rutina accede a variables de memoria cuya dirección se muestran en la tabla de símbolos. Al momento de su llamado, la memoria y los registros tenían el estado mostrado. Ejecute la rutina a mano y muestre en cada paso los cambios de los valores en memoria y los registros. Explique qué hace la rutina. Notas: 1) 2) 3) 4) LEA R3, A carga la dirección de la variable A en el registro R3. INC R2 incrementa en 1 el contenido del registro R2 DEC R1 decrementa en 1 el contenido del registro R1 JNZ LOOP modifica el PC para que apunte a la dirección 100FH o :LOOP si el resultado de la operación anterior no fue 0. Tabla de Símbolos :RUTINA R3, R4, R1, R2, A B D 0 A 2010H B 2020H C 2030H D 2040H R5 (R3)+ (R4)+ R5 2030H(R2), R5 R2 R1 LOOP Memoria ... 100FH 1011H 1015H 1017H 1019H 101BH 101DH LEA LEA MOV MOV :LOOP MOV ADD MOV INC DEC JNZ RETURN 0 1 2 2010 1 2 3 2020 10 20 30 2030 2040 3 2050 ... 1000H 1004H 1008H 100CH Página 4 3 4 5 ... F UNIVERSIDAD NACIONAL DE INGENIERIA FACULTAD DE ELECTROTECNIA Y COMPUTACION Departamento de Arquitectura y Sistemas Arquitectura de Máquinas Computadoras II Registros 1 R0 R1 R2 R3 R4 2 3 4 5 6 7 2010H 2020H Página 5 8 9 10 11 12