ELO311 Estructuras de Computadores Digitales Memoria

Anuncio

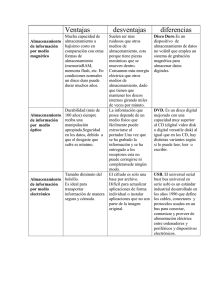

ELO311 Estructuras de Computadores Digitales Memoria Tomás Arredondo Vidal Este material está basado en: material de apoyo del texto de David Patterson, John Hennessy, "Computer Organization & Design", (segunda y tercera edición), Morgan Kaufmann, CA. 2005 materia del curso de Mary Jane Irwin en PSU, EEUU material del curso anterior ELO311 del Prof. Leopoldo Silva www.wikipedia.org Interconexión del sistema bus Processor Main Memory Receiver Keyboard La computadora usa un bus como enlace de comunicación para conectar múltiples subsistemas Cosas de interés son Performance Expandabilidad Resistencia en caso de falla (fault tolerance) Interconexión del sistema (cont) Generalmente se tiene mas de un aparato de input/output (I/O) en el sistema Cada aparato tiene un controlador de I/O interrupt signals Processor Cache Memory Memory - I/O Bus Main Memory I/O Controller Disk Disk I/O Controller Terminal I/O Controller Network Características del Bus Control Lines Data Lines Líneas de Control Señales de control y acks Indican el tipo de información en las líneas de datos Líneas de Datos Datos, instrucciones complejas y direcciones Transacción en el bus consiste de Enviar la dirección Recibir o enviar los datos Transacción de Output (Read) en el BUS Definido por lo que le hacen a la memoria read = output: transfiere datos desde memoria (read) a aparato de I/O (write) Step 1: Processor sends read request and read address to memory Control Main Memory Processor Data Step 2: Memory accesses data Control Main Memory Processor Data Step 3: Memory transfers data to disk Control Main Memory Processor Data Transacción de Input (Write) en el BUS Definido por lo que le hacen a la memoria write = input: transfiere datos desde el aparato de I/O (read) a memory (write) Step 1: Processor sends write request and write address to memory Control Main Memory Processor Data Step 2: Disk transfers data to memory Control Main Memory Processor Data Ventajas y Desventajas de BUSES Ventajas Versatilidad Nuevos aparatos (devices) se pueden agregar fácilmente Periféricos se pueden intercambiar entre sistemas computacionales con el mis standard de bus Bajo Costo: Un set de cables se comparte en múltiples maneras Desventajas Crea un cuello de botella de comunicaciones El bandwidth limita el máximo flujo (throughput) La velocidad del bus se limita principalmente por El largo del bus El numero de aparatos conectados al bus Tiene que soportar un rango de aparatos con tasas de transferencia y latencias que varían Tipos de Buses Bus Procesador-Memoria (propietario) Corto y de alta velocidad Diseñado para que el sistema de memora maximiza el ancho de banda de memoria-procesador Optimizado para transferencias de bloques de cache Bus I/O (estándar industrial, e.g., SCSI, USB, ISA, IDE) Mas largo y mas lento Debe acomodar una multitud de aparatos de I/O Conecta al bus procesador-memora o al bus principal de la maquina (backplane bus) Bus Backplane (estándar industrial, e.g., PCI) El bus de backplane es la estructura de interconexión en el chasis Se usa como un bus intermediario conectando los buses de I/O con el bus de procesador-memoria Sistema con Dos Buses Processor-Memory Bus Processor Memory Bus Adaptor I/O Bus Bus Adaptor Bus Adaptor I/O Bus I/O Bus I/O buses I/O se conectan al bus processor-memory usando Adaptadores de Bus (que hacen el interfaz para equiparar las diferentes velocidades de los buses) Bus processor-memory: principalmente para trafico processormemory Bus I/O: proveen slots de expansión para aparatos de I/O devices Sistema con Tres Buses Processor-Memory Bus Processor Memory Bus Adaptor Bus Adaptor Backplane Bus Bus Adaptor I/O Bus I/O Bus Se agrega un pequeño numero de buses de Backplane Buses conectado al bus de Processor-Memory Ventaja: carga en el bus Processor-Memory es reducido Ejemplo: Sistema I/O (Apple Mac 7200) Típico de sistemas medianos al fines de los 90 Processor Cache Memory Main Memory PCI Interface/ Memory Controller Processor-Memory Bus Audio I/O Serial ports I/O Controller I/O Controller CDRom Disk Tape SCSI bus PCI I/O Controller Graphic Terminal I/O Controller Network Ejemplo: Sistema Pentium Processor-Memory Bus Memory controller (“Northbridge”) PCI Bus I/O Buses http://developer.intel.com/design/chipsets/850/animate.htm?iid=PCG+devside& Repaso: Componentes de una Computadora Processor Control Datapath Devices Memory Input Output Principio de Localidad Los programas acceden a una parte relativamente pequeña de su espacio de direcciones durante un espacio corto de tiempo Localidad Temporal Si un elemento es referenciado, volverá a ser referenciado pronto (e.g. bucles o loops) Localidad Espacial Si un elemento es referenciado, los elementos cuyas direcciones están próximas tenderán a ser referenciados pronto (e.g. elementos en un arreglo, instrucciones que se acceden en forma secuencial) Jerarquía y Memoria Cache Dado el principio de localidad y que hay diferencias de costo y tiempo de acceso, es ventajoso construir la memoria como jerarquía de niveles. El cache es una memoria rápida en acceso a sus componentes, relativamente pequeña en su número de componentes, y por el momento costosa en dinero que interactúa directamente con el procesador. Suele ser memoria estática SRAM (por static random access memory, memoria estática de acceso aleatorio) y recientemente SSRAM (memoria estática sincrónica de acceso aleatorio). Costos y Velocidades Típicas de la Memoria Usando el principio de localidad: Presentar al usuario con la mayor memoria disponible en la tecnología mas barata. Dar acceso en la velocidad ofrecida por la tecnología mas rápida. L1 cache L2 cache On-Chip Components Control .1’s Size (bytes): 100’s Cost: Instr Data Cache Cache Speed (ns): ITLB DTLB RegFile Datapath eDRAM Second Level Cache (SRAM) Main Memory (DRAM) 1’s 10’s 100’s 1,000’s 100K’s M’s-G’s T’s 10K’s highest Secondary Memory (Disk) lowest Características de la Jerarquía de Memoria Processor Distancia del procesador en tiempo de acceso L1 L2 Main Memory Secondary Memory Tamaño relativo de la memoria en cada nivel Inclusive– lo que esta en L1 es un subconjunto de lo que esta en L2 que es un subconjunto de MM que es un subconjunto de SM Jerarquía y Memoria Cache (cont) La memoria cache es accedida directamente por el procesador y ésta puede acceder al siguiente elemento de la jerarquía que es la memoria denominada principal. En la jerarquía se copian datos solamente entre niveles adyacentes de memoria La unidad de información se denomina bloque, se transfiere un bloque completo cuando se copia entre niveles Jerarquía de Memoria: Tecnologías Acceso Aleatorio (Random Access) “Aleatorio” es bueno: tiempo de acceso es el mismo para todas las ubicaciones DRAM: Dynamic Random Access Memory Alta densidad (celdas de 1 transistor), bajo poder, baratas, lentas Dynamic: tienen que ser refrescadas regularmente (~ cada 8 ms) SRAM: Static Random Access Memory Baja densidad (celdas de 6 transistores), alto consumo, caras, rápidas Estática: contenidos duran para siempre (hasta que se apague la energía) Tamaño: DRAM vs SRAM - 1 a 4 Costo: SRAM vs DRAM - 1 a 8 Tecnologías no aleatorias Tiempos de acceso varían de ubicación a ubicación y en el tiempo (e.g., Disco, CDROM) Ciclo de Lectura Típico de RAM Para leer se coloca la dirección en el bus, luego se activa el Chip Enable y el Output Enable (con WE’ alto y CE’ y OE’ bajas), después del tiempo de acceso (en el orden de varios ns) se tienen datos válidos en el bus Dout. Otra Version: http://www.eventhelix.com/realtimemantra/faulthandling/bus_cycles.htm Ciclo de Escritura Típico de RAM Se colocan los datos en Din, y la dirección en el bus; luego se activan Chip Enable(CE’ baja) y Write Enable. Los datos son escritos en el canto de subida de WE’. La señal Write Enable es un pulso con requerimientos de ancho mínimo, más que un reloj. Adicionalmente deben cumplirse tiempos de set-up y hold. El dispositivo externo debe colocar datos en el bus bidireccional. Otra Version: Ejemplo: SRAM de 4x2 (un decodificador) Organizacion de SRAM (dos decodificadores) bit (data) lines r o w d e c o d e r dirección de fila Cada intersección representa una celda de 6Transistores RAM Cell Array seleccionador de palabra Column Selector & I/O Circuits 4 palabra de datos dirección de columna Una fila tiene un bloque de datos, y la dirección de la columna selecciona la palabra (word) de ese bloque Ejemplo: SRAM de 32Kx4 (dos decodificadores) 1 1 1 1 Organizacion DRAM (usando planos) .. . bit (data) lines r o w d e c o d e r Cada intersección es una celda DRAM de 1 transistor RAM Cell Array word (row) select column address row address Column Selector & I/O Circuits data bit data bit . . . data bit ord w data La dirección de la columna selecciona el bit de cada fila en el plano Ejemplo: DRAM de 1Mx1 (1 plano) 1024 1 Definiciones de Memoria RAM Cache usa SRAM para velocidad Memoria Principal usa DRAM por su mayor densidad Dirección (addresses) se divide en 2 partes (row and column) RAS or Row Access Strobe activa decodificador de fila CAS or Column Access Strobe activa decodificador de columna Performance de DRAMs Latencia: Tiempo para leer una palabra Tiempo de acceso: tiempo entre petición y cuando llegan palabras Tiempo de ciclo: tiempo entre peticiones Usualmente tiempo de ciclo > tiempo de acceso Bandwidth: Cuantos datos se pueden leer por unidad de tiempo ancho del canal de datos * la tasa en que se puede usar Operación de DRAM Clásica Column Address N rows x N column x M-bit Leer o Escribir M-bits a la vez Cada acceso de M-bits requiere un ciclo RAS / CAS N cols DRAM N rows Organización de DRAM: Row Address M bits M-bit Output Cycle Time 1st M-bit Access 2nd M-bit Access RAS CAS Row Address Col Address Row Address Col Address Maneras de Mejorar la Performance de DRAM Memory interleaving Fast Page Mode DRAMs – FPM DRAMs www.usa.samsungsemi.com/products/newsummary/asyncdram/K4F661612D.htm Extended Data Out DRAMs – EDO DRAMs www.chips.ibm.com/products/memory/88H2011/88H2011.pdf Synchronous DRAMS – SDRAMS www.usa.samsungsemi.com/products/newsummary/sdramcomp/K4S641632D.htm Rambus DRAMS www.rambus.com/developer/quickfind_documents.html www.usa.samsungsemi.com/products/newsummary/rambuscomp/K4R271669B.htm Double Data Rate DRAMs – DDR DRAMS www.usa.samsungsemi.com/products/newsummary/ddrsyncdram/K4D62323HA.htm Incrementar el Bandwidth - Interleaving Patron de acceso sin interleaving: Cycle Time CPU Memory Access Time D1 available Start Access for D1 Start Access for D2 D2 available Memory Bank 0 Con interleaving de 4 vias: CPU Memory Bank 1 Access Bank 0 Memory Bank 2 Memory Bank 3 Access Bank 1 Access Bank 2 Access Bank 3 We can Access Bank 0 again Problemas con Interleaving Cuantos bancos de memoria? Idealmente, el numero de bancos ≥ numbero relojes que tenemos que esperar para acceder a la proxima palabra en el banco Solo funciona para accesos secuénciales (i.e., primera palabra pedida en el primer banco, segunda en el segundo, etc) Típicamente se usa sola para sistemas de memoria muy grandes (e.g. supercomputadoras) Operación de DRAM : Modo Fast Page Column Address Fast Page Mode DRAM N cols N x M “SRAM” para ahorrar fila N rows Después que una fila se lee al DRAM “registro” SRAM Solo CAS se necesita para acceder a otros bloques de Mbits en esa fila N x M “SRAM” RAS se mantiene mientras se cambia CAS M-bit Output 1st M-bit Access 2nd M-bit 3rd M-bit Row Address M bits 4th M-bit RAS CAS Row Address Col Address Col Address Col Address Col Address Porque nos importa la jerarquía de Memoria? Distancia Procesador-Memoria DRAM CPU “Moore’s Law” Processor-Memory Performance Gap: (grows 50% / year) 100 10 DRAM 1 1980 1981 1982 1983 1984 1985 1986 1987 1988 1989 1990 1991 1992 1993 1994 1995 1996 1997 1998 1999 2000 Performance 1000 µProc 60%/year (2X/1.5yr) Time DRAM 9%/year (2X/10yrs) Jerarquia de Memoria: Objetivos Hecho: Memorias grandes son lentas, memorias rápidas son pequeñas Como creamos una memoria que da la ilusión de ser grande, barata y rápida (la mayoría del tiempo)? ….tomando ventaja de El principio de la Localidad: Programas acceden a una porción relativamente pequeña del espacio de memoria en un instante de tiempo. Probability of reference 0 Address Space 2n - 1 Jerarquía de Memoria: Como funciona? Localidad Temporal: Mantener los datos mas recientemente accedidos mas cercanos al procesador Localidad Espacial: Mover los bloques de palabras contiguas a los recientemente accedidos a niveles mas cercanos al procesador To Processor Upper Level Memory Lower Level Memory Blk X From Processor Blk Y Jerarquía de Memoria: Terminología Hit (éxito): datos están en un bloque en nivel alto (Block X) Tasa de éxito (Hit Rate): la fracción de acceso de memoria que se resuelven en el nivel alto Tiempo de éxito (Hit Time): Tiempo para acceder al nivel alto que consiste de: tiempo acceso a RAM + tiempo para determinar hit/miss To Processor Upper Level Memory Lower Level Memory Blk X From Processor Blk Y Miss (falla): datos tienen que ser sacados de un bloque en nivel bajo (Block Y) Tasa de Falla (Miss Rate) = 1 - (Hit Rate) Penalidad de Falla (Miss Penalty): Tiempo para reemplazar un bloque en el nivel mas alto + Tiempo para enviar bloque al procesador Hit Time << Miss Penalty Jerarquía de Memoria: Cálculos Ciclos de detención en memoria de instrucciones = Instrucciones * Tasa de fallos * Penalización por fallos Ciclos de detención en memoria de datos = Instrucciones que accesan memoria * Tasa de fallos * Penalización por fallos Penalización total = Ciclos de detención-memoriainstrucciones + Ciclos de detención-memoria -datos Quien Maneja las Jerarquías? registros <-> memoria por compilador y programador cache <-> memoria principal por el hardware (HW) memoria principal <-> discos por el HW y el sistema operativo por el programador (archivos) Cache de Mapeo Directo Cada localización de memoria se mapea en una localización en la cache. Índice establece el número de direcciones de la cache ( 2i celdas). Cache de Mapeo Directo (cont) Existen muchas direcciones que tienen igual campo índice y se almacenarán en la misma dirección de la cache, esto implementa el mecanismo de acceso denominado directo. Al inicio se marcan todas las celdas de la cache como invalidas (campo V igual a cero). Al intentar leer una dirección se producirá un fallo, entonces se leerá desde la memoria principal y se traerá el contenido al campo dato de la cache; y se escribe el campo marca con los m bits más significativos de la dirección en la celda índice de la caché y se marca como válida (V = 1). Si más adelante se desea leer una dirección que tenga el mismo índice pero con diferente marca se producirá un fallo. Y se reescribe la marca (desde el bus de dirección) y el nuevo dato que se trae desde la memoria principal. Cache de Mapeo Directo con Bloques Para aprovechar la localidad espacial el bloque de la cache contiene varias palabras adyacentes (una potencia de dos). Los bits dedicados a la administración de la cache (válido, marca) disminuyen al aumentar el tamaño del bloque. Cache de Mapeo Directo con Bloques (cont) Si se produce un fallo (de lectura), deben ahora traerse desde la memoria principal 2Offset Bloques palabras adyacentes. Al aumentar el tamaño del bloque disminuye la tasa de fallos, este efecto es más notable en la cache de instrucciones debido a la mejor localidad espacial. Cache Asociativo Para flexibilizar la colocación de los bloques la cache asociativa de n vías, permite colocar un bloque en n posiciones. Cache Asociativo (cont) El diagrama anterior ilustra una cache asociativa por conjuntos de dos vías y muestra la comparación necesaria, realizada en paralelo, para ubicar a un bloque que puede estar en dos posiciones (en la primera o segunda vía). En el ejemplo sólo pueden estar en la cache dos bloques que tengan igual índice; en caso de requerir colocar un tercero, con igual índice, debe aplicarse alguna política de reemplazo (e.g. aleatorio, menos usada) Tabla de Páginas Para tener completa asociatividad se emplea una Tabla de Páginas residente en memoria, que tiene como índice el número de página virtual y como contenido el número de página física, además de un bit para indicar si la página está o no presente en lamemoria. Cada programa tiene su propia tabla de páginas, y se dispone un registro en el procesador para apuntar a la tabla de página activa. Resumen DRAM es lento pero denso y de bajo costo Bueno para un sistema de memoria GRANDE SRAM es rápido pero caro y no muy denso Tiempos de acceso RAPIDOS Dos tipos de localidad Temporal Espacial Usando el principio de localidad: Presentar al usuario con la mayor memoria posible en la tecnología mas barata Provee acceso a la tecnología ofrecida por la tecnología mas rápida