Ejercicios Resueltos TEL-201 UTFSM © REINALDO VALLEJOS, 2010

Anuncio

©

R

Ejercicios Resueltos

10

N TE

AL LD 20

O 1

VA UT

LL FS

EJ M

O

S,

20

EI

Apéndice A

178

Capı́tulo 1

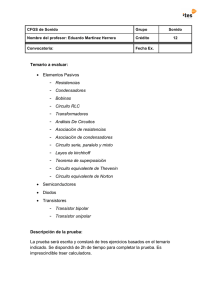

EJERCICIO 1.1 Analizar el circuito de la Figura A.1, para los valores de excitación que aparecen en la Tabla A.1 y determinar cada una

de las entradas que están en blanco en dicha Tabla.

'

,

9

9 '

'

10

,

9

N TE

AL LD 20

O 1

VA UT

LL FS

EJ M

O

S,

20

9

9' 5 >N@

,5

Figura A.1: Circuito Máx-Off de dos entradas

Caso

1

2

3

V1

[V]

3

-3

2

V2

[V]

3

-2

5

Estado

D1 D2

V0

[V]

IR

[mA]

EI

Tabla A.1: Análisis del circuito de la Figura A.1

R

RESPUESTA.

©

Caso 1. De acuerdo a la ecuación 1.4 y lo que establece en el punto

iii), ambos diodos quedan directos. En consecuencia: V0 =2,25[V].

Luego IR , está dado por:

IR =

(V2 − VD2 )[V]

= 1, 125[mA]

2[KΩ]

Caso 2. La ecuación 1.4 y el punto i), establece que ambos diodos

quedan abiertos. En consecuencia: V0 =0[V].

Luego IR , está dado por:

A. Ejercicios Resueltos

IR =

179

V0 [V]

= 0[mA]

2[KΩ]

Caso 3. La ecuación 1.4 y el punto ii), determinan que D2 está directo

y D1 queda abierto. En consecuencia: V0 =4,25[V]. Luego IR , está dado

por:

(V2 − VD2 )[V]

= 2, 125[mA]

2[KΩ]

10

IR =

N TE

AL LD 20

O 1

VA UT

LL FS

EJ M

O

S,

20

Los resultados obtenidos en los tres casos anteriores se resumen en la

Tabla A.2.

Caso

1

2

3

V1

[V]

3

-3

2

V2

[V]

3

-2

5

Estado

D1

D2

Directo Directo

Abierto Abierto

Abierto Directo

V0

[V]

2,25

0

4,25

IR

[mA]

1,125

0

2,125

Tabla A.2: Análisis del circuito de la Figura A.1

EI

EJERCICIO 1.2 Analizar el circuito de la Figura A.2 para los valores

de excitación que aparecen en la Tabla A.3. Determinar cada una de las

entradas de la Tabla A.3:

R

>9@

©

,5

5 >N@

'

9

9 '

9

,

9

'

9' ,

Figura A.2: Circuito Mı́n-Off de dos entradas.

180

Caso

1

2

3

V1

[V]

3

-3

2

V2

[V]

3

-2

5

Estado

D1 D2

V0

[V]

IR

[mA]

Tabla A.3: Análisis del circuito de la Figura A.2

RESPUESTA.

N TE

AL LD 20

O 1

VA UT

LL FS

EJ M

O

S,

20

10

Caso 1. De acuerdo a la ecuación 1.5, ambos diodos quedan directos,

En consecuencia:

V0 = 3, 75[V]

Luego, IR :

IR =

(5 − V0 )[V]

= 0, 625[mA]

2[KΩ]

Caso 2. La ecuación 1.5, establece que D1 se encuentra directo y D2

abierto. En consecuencia:

EI

V0 = −2, 25[V]

R

Luego IR , está dado por:

(5 − V0 )[V]

= 3, 625[mA]

2[KΩ]

©

IR =

Caso 3. La ecuación 1.5, determina que D1 se encuentra directo y D2

abierto. En consecuencia:

V0 = 2, 75[V]

Luego IR , está dado por:

IR =

(5 − V0 )[V]

= 1, 125[mA]

2[KΩ]

181

A. Ejercicios Resueltos

En resumen, en cada uno de los casos anteriores el estado del circuito

Mı́n-Off es el siguiente:

Caso

V1

[V]

3

-3

2

1

2

3

V2

[V]

3

-2

5

Estado

D1

D2

Directo Directo

Directo Abierto

Directo Abierto

V0

[V]

3,75

-2,25

2,75

IR

[mA]

0,625

3,625

1,125

N TE

AL LD 20

O 1

VA UT

LL FS

EJ M

O

S,

20

10

EJERCICIO 1.3 Considerando que cualquier voltaje entre 0[V] y

0,2[V] es considerado un 0 lógico y que los voltajes entre 2,4[V] y 5[V]

son considerados 1 lógico; para el circuito de la Figura A.3, determine

los estados de los diodos D1 , D2 y D3 , para los casos enunciados en

la siguiente tabla. Además, determine I[mA], Vx [V] y V0 [V] para cada

caso.

R1

R2

[V]

[KΩ]

[KΩ]

1

5

4

1

2

5

4

0

3

5

4

1

4

0

4

1

5

0

4

0

6

0

Caso

V1

Estado

Estado

Estado

D1

D2

D3

I

Vx

V0

[mA]

[V]

[V]

ON

ON

1

4

R

EI

Tabla A.4: Tabla de resultados

>9@

©

,

5 >N@

9

'

'

'

9N

9

5 >N@

Figura A.3

182

RESPUESTA. Antes de resolver el circuito, es conveniente redibujarlo

de la siguiente forma:

>9@

,

5 >N@

'

9

'

9

N TE

AL LD 20

O 1

VA UT

LL FS

EJ M

O

S,

20

5 >N@

10

'

9[

Figura A.4: Circuito de la Figura A.3 reorganizado.

Tal como se ilustra en la Figura A.4, el circuito corresponde a una variante de circuito Mı́n-Off, lo cual facilita su análisis.

Caso 1. De acuerdo a la ecuación 1.5, D1 queda cortado, mientras que

D2 queda directo. En consecuencia:

R

Vx

EI

(5 − VD2 )[V]

= 0, 85[mA]

5[KΩ]

= 5[V] − (4[KΩ] ⋅ 0, 85[mA]) = 1, 6[V]

I =

©

V0 = Vx − VD2 [V] = 1, 6 − 0, 75 = 0, 85[V]

Caso 2. En este caso D1 queda inverso, mientras D2 y D3 quedan

directos. Por lo tanto:

(5 − VD2 − VD3 )[V]

= 0, 875[mA]

4[KΩ]

= 5[V] − (4[KΩ] ⋅ 0, 875[mA]) = 1, 5[V]

I =

Vx

V0 = Vx − VD2 − VD3 = 0[V]

A. Ejercicios Resueltos

183

Caso 3. En este caso D1 queda inverso, mientras que D2 y D3 quedan

directos. En consecuencia:

(5 − VD2 − VD3 )[V]

= 0, 7[mA]

5[KΩ]

= 5[V] − (4[KΩ] ⋅ 0, 7[mA]) = 2, 2[V]

I =

Vx

V0 = (Vx − VD2 − VD3 )[V] = 0, 7[V]

N TE

AL LD 20

O 1

VA UT

LL FS

EJ M

O

S,

20

10

Caso 4. D1 se encuentra directo y Vx es suficiente para polarizar

directo a D2 . Observación: En general, el análisis de la proporción de

corriente que circula por cada diodo no es relevante en el tipo de análisis

de circuitos integrados que se hace en este texto.

Vx = VD1 + V1 = 0, 75 + 0 = 0, 75[V]

V0 = (Vx − VD2 )[V] = 0, 75 − 0, 75 = 0[V]

(5 − Vx )[V]

= 1, 0625[mA]

I =

4[KΩ]

EI

Caso 5. En este caso D1 queda directo. Nuevamente Vx no es suficiente

para polarizar los demás diodos, los cuales quedan abiertos.

©

R

Observación: V0 queda indefinido, ya que no está conectado eléctricamente a ningún circuito. En consecuencia:

(5 − Vx )[V]

= 1, 0625[mA]

4[KΩ]

= VD1 + V1 = 0, 75 + 0 = 0, 75[V]

I =

Vx

Caso 6. En este caso D1 queda directo; sin embargo Vx no es suficiente

para polarizar D2 y D3 , en consecuencia éstos quedan abiertos. Luego,

se obtiene:

184

(5 − VD1 )[V]

= 1, 0625[mA]

4[KΩ]

= VD1 + V1 = 0, 75 + 0 = 0, 75[V]

I =

Vx

V0 = 0[V]

La Tabla A.5 resume los análisis realizados arriba.

I

Vx

V0

[mA]

[V]

[V]

ON

0,85

1,6

0,85

Directo

0,875

1,5

0

0,7

2,2

0,7

1,0625

0,75

0

R1

R2

Estado

Estado

Estado

[KΩ]

[KΩ]

D1

D2

D3

1

5

4

1

Abierto

Directo

2

5

4

0

Abierto

Directo

3

5

4

1

Abierto

Directo

Directo

4

0

4

1

Directo

Directo

ON

5

0

4

0

Directo

Abierto

Abierto

1,0625

0,75

-

6

0

4

1

Directo

Abierto

Abierto

1,0625

0,75

0

10

V1

[V]

N TE

AL LD 20

O 1

VA UT

LL FS

EJ M

O

S,

20

Caso

Tabla A.5: Tabla de resultados

EJERCICIO 1.4 Considere el circuito de la Figura A.5a y la entrada

en función del tiempo que se muestra en el gráfico de la Figura A.5b:

EI

▪ Determinar el estado de los diodos D1, D2, D3, D4 en los instantes τ1 ,

τ2 , τ3 , τ4 .

©

R

▪ Graficar V0 (t).

>9@

5 >.@

'

'

'

9

9

'

5 >.@

Figura A.5

A. Ejercicios Resueltos

185

9LW>9@

N TE

AL LD 20

O 1

VA UT

LL FS

EJ M

O

S,

20

WVHJ

10

Figura A.6: Gráfico de V1 (t)

RESPUESTA. En la Figura A.7, el circuito está redibujado para dejar

en evidencia que se trata de una variante de un circuito Min-Off.

>9@

>N@

9

9[

9

'

'

>N@

R

EI

'

'

©

Figura A.7: Circuito de la Figura A.5 redibujado

Instante τ1 . De acuerdo a la ecuación 1.5 y lo que se establece inmediatamente después de esta, los diodos D1 y D2 están abiertos, mientras

que D3 y D4 están directos. En consecuencia:

5 − VD3 − VD4

= 0, 7[V]

(R1 + R2 )

= (5 − R1 IR1 ) = 2, 2[V]

IR1 = IR2 =

Vx

V0 (τ1 ) = (Vx − VD3 − VD4 ) = 0, 7[V]

186

Instante τ2 . En este caso los diodos D1 y D2 están directos. Además,

como Vx es menor que 0[V], D3 y D4 quedan abiertos. Por lo tanto:

IR2 = 0[V]

V0 (τ2 ) = 0[V]

(5 − VD3 − VD4 )

= 0, 7[mA]

(R1 + R2 )

= (5 − R1 IR1 ) = 2, 2[V]

N TE

AL LD 20

O 1

VA UT

LL FS

EJ M

O

S,

20

IR1 = IR2 =

10

Instante τ3 . En este caso, los diodos D1 y D2 quedan abiertos, mientras

que D3 y D4 están directos. En consecuencia:

Vx

V0 (τ3 ) = (Vx − VD3 − VD4 ) = 0, 7[V]

Instante τ4 . Debido a que V1 tiene el mismo voltaje de la tierra, D1 no

se polariza, en cambio D2 sı́ lo hace. Esto causa que D3 y D4 queden

en zona de corte. En consecuencia:

IR2 = 0[V]

V0 (τ2 ) = 0[V]

R

EI

En resumen:

Instante

©

τ1

τ2

τ3

τ4

V1 (t)

[V]

7

-2

5

0

D1

OFF

ON

OFF

OFF

Estado

D2

D3

OFF ON

ON OFF

OFF ON

ON OFF

D4

ON

OFF

ON

OFF

V0 (t)

[V]

0,7

0

0,7

0

Tabla A.6: Resumen de resultados del ejercicio 1.4

Considerando el hecho de que en el circuito Min-Off de la Figura A.7,

V0 (t) depende directamente de v1 (t) y usando los datos obtenidos en los

cálculos anteriores y la tabla A.6, se puede concluir que: si V1 (t) ≥ 5[V],

entonces V0 (t) = 0, 7[V]. Por otro lado, si V1 (t) < 5[V], entonces V0 (t) =

0[V]. Estos antecedentes permiten obtener el siguiente gráfico de V0 (t)

en función de V1 (t).

A. Ejercicios Resueltos

187

9LW>9@

WVHJ

WVHJ

N TE

AL LD 20

O 1

VA UT

LL FS

EJ M

O

S,

20

10

9LW>9@

Figura A.8: Gráfico de V0 (t)

EJERCICIO 1.5 Dado el circuito de la Figura A.9:

'

,'

,5

,'

9'

'

9

9'

9

5

>N@

Figura A.9

R

EI

9

©

Para los valores de las fuentes V1 y V2 especificados en la Tabla A.7,

determine los valores que están en blanco en dicha Tabla.

V1

[V]

10

−5

V2

[V]

5

−10

Estado

D1

Estado

D2

VD1

[V]

ID1

[mA]

VD2

[V]

ID2

[mA]

V0

[V]

Tabla A.7: Análisis de la Figura A.9

RESPUESTA. Al analizar el circuito, se observa que existe un circuito

del tipo Max-off, lo cual queda en evidencia al redibujarlo en la siguiente

forma:

188

10

Figura A.10: Circuito de la Figura A.9 redibujado

N TE

AL LD 20

O 1

VA UT

LL FS

EJ M

O

S,

20

Caso 1. V1 = 10[V], V2 = 5[V]. De acuerdo a la ecuación 1.4 y lo que

se establece inmediatamente después de esta, el diodo D1 queda directo,

mientras que D2 queda abierto. En consecuencia:

VD1 = 0, 75[V]

ID2 = 0[mA]

V0 = (V1 − VD1 )[V] = 9, 25[V]

VD2 = (V2 − V0 )[V] = −4, 25[V]

V0 [V]

= 9,25[mA]

ID1 =

R[KΩ]

©

R

EI

Caso 2. V1 = −5[V], V2 = −10[V]. Debido a que ambos voltajes son

menores al voltaje de la tierra 0[V], D1 y D2 quedan abiertos. En consecuencia:

ID1 = ID2 = 0[mA]

V0 = 0[V]

VD1 = (V1 − V0 ) = −5[V]

VD2 = (V2 − V0 ) = −10[V]

EnVresumen:

V2

Estado

1

[V] [V]

D1

10

5

ON

−5 −10

OFF

Estado

D2

OFF

OFF

VD1

[V]

0,7

−5

ID1

[mA]

9,25

0

VD2

[V]

−4, 25

−10

Tabla A.8: Resultados del ejercicio 1.5

ID2

[mA]

0

0

V0

[V]

9,25

0

A. Ejercicios Resueltos

189

EJERCICIO 1.6 Para el circuito de la Figura A.11, determine el valor

de las corrientes y voltajes en cada diodo, además del voltaje de la salida.

9 >9@

5

9 >9@ '

,'

>N@

,5

9

9'

10

9'

,'

'

N TE

AL LD 20

O 1

VA UT

LL FS

EJ M

O

S,

20

9 >9@

Figura A.11

RESPUESTA. El circuito de la Figura A.11 es un Min-Off, por lo

tanto, de la ecuación 1.5 y su análisis, implican que, D2 queda directo

y D1 queda abierto. En consecuencia:

VD2 = 0, 75[V]

V0 = (VD2 + V3 ) = 5, 75[V]

VD1 = (V0 − V2 ) = −4, 25[V]

©

R

EI

ID1 = 0[mA]

(V1 − V0 )

= 9,25[mA]

ID2 =

R

EJERCICIO 1.7 Para el circuito de la Figura A.12:

a) Calcule los estados de los siguientes diodos y voltajes.

1

2

3

4

Diodo

5 6 7

8

9

10

V1

b) Calcule las corrientes en cada Resistencia.

V2

Voltaje

V3 V4

V0

190

>9@

5 >.@

'

>9@

'

9

9

'

>9@

'

,5

5 .

,5

'

9

N TE

AL LD 20

O 1

VA UT

LL FS

EJ M

O

S,

20

10

>9@

'

>9@

>9@

'

'

9

'

9

,5

'

5 >.@

5 >.@

,5

5 .

,5

>9@

Figura A.12

D2

OFF

V1

[V]

5,25

D3

D4

D5

D6

D7

D8

D9

D10

ON

ON

OFF

ON

ON

OFF

ON

ON

OFF

V2

[V]

3,25

V3

[V]

4,75

V4

[V]

4

V0

[V]

4

ID1

[mA]

5,25

ID3

[mA]

3,25

ID6

[mA]

0,25

ID7

[mA]

-1

ID9

[mA]

4

©

R

D1

EI

RESPUESTA.

Tabla A.9

EJERCICIO 1.8 El circuito de la Figura A.13a), es conocido como

rectificador de media onda. Determine (grafique) V0 (t) para el caso en

A. Ejercicios Resueltos

191

que Vi (t) es una señal senoidal de 220[V] RMS, tal como aparece en

Figura A.13b.

,5

5

9W

9LW

N TE

AL LD 20

O 1

VA UT

LL FS

EJ M

O

S,

20

10

a) Circuito

9LW>9@

>9@

10

20

30

40

50

60

70

W>PV@

b) Gráfico Vi (t)

Figura A.13

©

R

EI

RESPUESTA. Dado que se tiene una señal de excitación alterna de

220[V] RMS, se deben analizar dos tipos de casos: cuando Vi (t) toma

un valor positivo y cuando toma un valor negativo.

Cuando Vi (t) toma un valor positivo (> 0, 75[V]), este voltaje logra

polarizar directamente el diodo, obteniendo V0 (t) = Vi (t) − 0, 75[V]. Sin

embargo, debido a que la caı́da de voltaje en el diodo es mucho menor

al voltaje de entrada, para simplificar el análisis se puede suponer que

el diodo es ideal. En consecuencia: si V0 (t) ≥ 0, entonces Vi (t) ≈ V0 (t).

Para el segundo caso, cuando Vi (t) toma un valor negativo, el diodo se

polariza de forma inversa, sin permitir el paso de la corriente (circuito

abierto), por lo cual V0 (t) = 0[V]. Los antecedentes previos permiten

obtener el gráfico de la Figura A.14.

192

9 L W > 9 @

>9 @

W>PV@

9 W >9 @

>9 @

N TE

AL LD 20

O 1

VA UT

LL FS

EJ M

O

S,

20

10

W>PV@

Figura A.14: V0 (t) en función de Vi (t) para el circuito de la Figura A.13

EJERCICIO 1.9 Considere el circuito de la Figura A.15 para las siguientes señales de excitación: v1 (t) = sen(wt), v2 (t) = sen(wt+2π/3) y

v3 (t) = sen(wt + 4π/3). Considere que las tres señales de entrada tienen

la misma frecuencia f = 50[Hz] y VRMS = 220[V]. Grafique la salida V0

en función del tiempo y determine cuál es la función que implementa el

circuito.

D1

VD1

R

EI

D2

v0 (t)

©

VD2

D3

VD3

v1(t)

IR

v2 (t)

v3 (t)

5

>N

Figura A.15

RESPUESTA. Para una señal sinusoidal de la forma A sen(Wt), se

A. Ejercicios Resueltos

193

A

cumple que: VRMS = √ . En este caso VRMS = 220[V], por lo tanto la

2

amplitud de la señal de salida es 310[V]. Esta es la misma amplitud que

tienen las tres entradas del circuito. Los antecedentes previos implican

que V0 (t) está dado por:

YL W >9 @

Y W >9 @

N TE

AL LD 20

O 1

VA UT

LL FS

EJ M

O

S,

20

Y W

Y W

10

Y W π

π

π

π

ϑ > UDG @

W>PV @

W>PV @

©

R

EI

Figura A.16: Señales de excitación y salida del circuito de la Figura A.15

De acuerdo a la Figura y su configuración, se puede ver que este circuito

es un Max-Off, por lo que la salida toma el valor de la mayor señal.

EJERCICIO 1.10 Considere el circuito de la Figura A.17 para los

siguientes valores de entrada: v1 (t) = sen(wt), v2 (t) = sen(wt + 2π/3)

y v3 (t) = sen(wt + 4π/3). Las tres señales de entrada tienen la misma

frecuencia f = 50[Hz] y VRMS = 220[V]. Grafique la salida V0 en función

del tiempo.

194

'

9'

'

Y W

9'

'

9'

YW

Y W

5

,5

Y W

>N

N TE

AL LD 20

O 1

VA UT

LL FS

EJ M

O

S,

20

10

Figura A.17

RESPUESTA. Nuevamente, las entradas de los diodos son señales

sinusoidales de igual amplitud y frecuencia pero de diferente fase. De

acuerdo a la Figura, se puede ver que este circuito es un rectificador

Mı́n-Off, por lo que la salida toma el valor de la menor señal. Esto se

puede comprobar con los siguientes gráficos donde se muestra la relación

entre la entrada y la salida del circuito.

YL W >9 @

Y W Y W

R

EI

π

π

π

π

ϑ>UDG @

W>PV @

W>PV @

©

Y W

Y W >9 @

− Figura A.18

A. Ejercicios Resueltos

195

EJERCICIO 1.11 Considere el circuito de la Figura A.19 para los

siguientes valores de excitación: v1 (t) = sen(wt), v2 (t) = sen(wt + 2π/3)

y v3 (t) = sin(wt + 4π/3). Las tres señales de entrada tienen la misma

frecuencia f = 50[Hz] y VRMS = 220[V]. Obtenga el gráfico de la salida

V0 en función del tiempo.

9' '

'

9' '

9'

,5

YW

Y W

Y W

5

>N

Y W

N TE

AL LD 20

O 1

VA UT

LL FS

EJ M

O

S,

20

10

9' '

'

9' '

9 '

Figura A.19

RESPUESTA. Las entradas de los diodos son señales sinusoidales de

igual amplitud y frecuencia pero de distinta fase. Nótese que este circuito está formado como la unión de los circuitos de los dos ejercicios

anteriores. Especı́ficamente, los diodos D1 , D2 y D3 forman un circuito

Max-Off, mientras que D4 , D5 y D6 forman un circuito Min-Off. Esto

permite obtener el siguiente gráfico para V0 (t).

YL W >9 @

Y W Y W

Y W

R

EI

π

π

π

π

ϑ>UDG @

W>PV @

W>PV @

©

Y W >9 @

Figura A.20

196

EJERCICIO 1.12 Para el circuito de la Figura A.21, grafique la

corriente IR en función de (wt), dado Vi (t) = V sen(wt).

9LW

9

'

9LW

,5

'

5

,I

ʌ

10

'

'

ZW

ʌ

N TE

AL LD 20

O 1

VA UT

LL FS

EJ M

O

S,

20

9

Figura A.21: Puente rectificador

RESPUESTA. Para efectos de análisis, el circuito de la Figura A.21

se redibuja de la siguiente forma:

'

9LW

'

'

,5

5

©

R

EI

,I '

Figura A.22: Circuito redibujado

Según esta configuración se puede reconocer que los diodos D1 , D2 y la

resistencia forman un circuito Max-Off. Análogamente, la resistencia y

los diodos D3 y D4 forman un circuito Min-Off.

Se supondrá |V| ≥ 1, 5[V], ya que se necesita polarizar dos diodos para

A. Ejercicios Resueltos

197

que la corriente circule por el circuito. En la siguiente tabla, se analiza el

estado de cada diodo para cada perı́odo de tiempo ilustrado en el gráfico

anterior.

Tiempo

t

0−π

π − 2π

D1

Directo

Abierto

Estado

D2

D3

Abierto Abierto

Directo Directo

D4

Directo

Abierto

IR

[mA](máx)

(V − 1, 5)/R

(V − 1, 5)/R

10

Tabla A.10

N TE

AL LD 20

O 1

VA UT

LL FS

EJ M

O

S,

20

De acuerdo al comportamiento de Vi y de la corriente If , el comportamiento de IR en función de (wt) es el siguiente:

,5

9

5

,','

ʌ

ʌ

ʌ

ʌ

ʌ

ʌ

ZW

ZW

©

R

EI

,','

ZW

Figura A.23

En la figura se puede ver que durante el semiciclo positivo de Vi conducen

los diodos D1 y D4 , los cuales determinan la corriente IR en ese semiperı́odo. Para el semiciclo negativo, la misma función la cumplen los

diodos D2 y D3 .

198

Capı́tulo 2

EJERCICIO 2.1 Considere el circuito de la Figura A.24. Determine

la zona en que se encuentra el transistor y también sus respectivas corrientes.

,&

N TE

AL LD 20

O 1

VA UT

LL FS

EJ M

O

S,

20

5% >. @

10

>9@

,%

K)( ,(

Figura A.24: Circuito 1

RESPUESTA. En este transistor debido a la fuente de 10[V] en la

base, la juntura base-emisor está directa. En consecuencia:

R

EI

VB = 0, 75[V]

(10 − VB )

= 9, 25[mA]

IB =

RB

©

Suponiendo que el transistor está en ZAD:

IC = hFE ⋅ IB = 462, 5[mA]

VC = 10[V]

Esto implica que VBC < 0. Por lo tanto la hipótesis de que el transistor

está en ZAD es correcta. Por último:

IE = IB + IC = 471, 75[mA]

A. Ejercicios Resueltos

199

En Resumen:

Vin

[V]

10

Zona

transistor

ZAD

VB

[V]

0,75

IB

[mA]

9,25

IE

[mA]

471,75

IC

[mA]

462,5

Tabla A.11: Resumen de resultados ejercicio 2.1

N TE

AL LD 20

O 1

VA UT

LL FS

EJ M

O

S,

20

>9@

10

EJERCICIO 2.2 Determine la zona de operación del transistor de la

Figura A.25, ası́ como sus voltajes y corrientes respectivas.

5& >. @

,5

,&

,%

K)( ,(

Figura A.25: Ejercicio 1

©

R

EI

RESPUESTA. En este caso la juntura base-emisor está ON. Para el

análisis, comenzamos evaluando IR . De lo anterior:

VB = 0, 75[V]

(10 − VB )[V]

= 9, 25[mA]

IR =

RC [kΩ]

Por ley de Kirschoff: IE = IR . Suponiendo ZAD:

IC = hFE ⋅ IB

IE = IB + IC = (hFE + 1)IB

200

De esto:

IB = 0, 092[mA]

IC = 9, 16[mA]

IE = 9, 25[mA]

A su vez, viendo el circuito se puede notar que:

10

VB = VC = 0, 75[V]

Zona

ZAD

N TE

AL LD 20

O 1

VA UT

LL FS

EJ M

O

S,

20

Esto implica que VBC = 0[V]. Por lo tanto la hipótesis de que el transistor

está en ZAD es correcta. En resumen:

VB

[V]

0,75

VE

[V]

0

VC

[V]

0,75

IB

[mA]

0,092

IE

[mA]

9,25

IC

[mA]

9,16

EJERCICIO 2.3 Calcule las corrientes en cada uno de los transistores

T1 y T2 del circuito de la Figura A.26 y también los voltajes VC1 y VC2

>9@

K)( K)( ,&

5 >. @

5 >. @

©

R

EI

5 >. @

>9@

,%

,&

,%

9&

9&

7

5 >. @

,(

Figura A.26: Circuito 3

7

,(

A. Ejercicios Resueltos

201

RESPUESTA. En el primer transistor, se cumple que la juntura baseemisor está ON. En consecuencia:

VB = 0, 75[V]

(10 − VB )[V]

= 9, 25[mA]

IR =

R1 [kΩ]

N TE

AL LD 20

O 1

VA UT

LL FS

EJ M

O

S,

20

10

En el peor caso, toda la corriente circula por el colector de T1 , mientras

la base de T2 queda sin corriente. Suponiendo además T1 en ZAD, se

obtendrı́a:

IC1 = hFE1 ⋅ IB1 = 462, 5[mA]

VC1 = (10 − R2 IC1 ) = −452, 5[V]

Esto implica que VBC1 > 0[V]. Por lo tanto, la hipótesis de que el transistor T1 está en ZAD es incorrecta, ya que la juntura base colector de

T1 estarı́a ON. Por lo tanto, T1 está en ZS y no en ZAD. Por lo tanto:

VC1 = 0, 2[V]

©

R

EI

Como VC1 es la entrada a T2 , éste no alcanza a polarizar su juntura BE

de T2 , en consecuencia T2 está en ZC y sus corrientes y voltajes son:

IB2 = IE2 = IC2 = 0[mA]

VC2 = 0[V]

Debido a que T1 está en ZS y que T2 está en ZC:

(10 − VC1 )

= 9, 8[mA]

R2 [KΩ]

= IB1 + IC1 = 19, 05[mA]

IC =

IE1

202

Transistor

Zona

T1

T2

ZS

ZC

En Resumen:

VC

[V]

0,2

0

IB

[mA]

9,25

0

IE

[mA]

19,05

0

IC

[mA]

9,8

0

EJERCICIO 2.4 Determine la zona en la que se encuentra el transistor

de la Figura A.27 y también sus respectivas corrientes y voltajes.

>9@

K)( N TE

AL LD 20

O 1

VA UT

LL FS

EJ M

O

S,

20

10

5 >. @

,&

5 >. @

>9@

,5

,5

5 >. @

,(

Figura A.27: Circuito 3

R

EI

9&

,%

©

RESPUESTA. Debido a la fuente de 10 V en el transistor se cumple

que la juntura base emisor está ON. En consecuencia:

VB = 0, 75[V]

(10 − VB )[V]

= 9, 25[mA]

IR1 =

R1 [kΩ]

En la misma rama de colector, calculamos IB e IR2 :

(10 − IR1 R1 )[V]

= 0, 75[mA]

R2 [KΩ]

= IR1 + IR2 = 8, 5[mA]

IR2 =

IB

A. Ejercicios Resueltos

203

Suponiendo que el transistor se encuentra en ZAD:

IC = hFE IB = 425[mA]

VC = 5 − IC R3 = −420[V]

10

Esto implica que VBC > 0[V]. Por lo tanto la hipótesis de que el transistor

está en ZAD es incorrecta, ya que la juntura base colector estarı́a ON.

Por lo tanto, el transistor está en ZS. Por lo tanto:

N TE

AL LD 20

O 1

VA UT

LL FS

EJ M

O

S,

20

VC = 0, 2[V]

Consecuentemente:

IR2 =

(5 − 0, 2)[V]

= 4, 8[mA]

R3 [KΩ]

En resumen:

Zona

VB

[V]

0,75

IB

[mA]

8,5

IE

[mA]

13,3

IC

[mA]

4,8

©

R

EI

ZS

VC

[V]

0,2

EJERCICIO 2.5 Considere el circuito de la Figura A.28. Para el valor

de la fuente V1 especificado en la Tabla 2.2, determine cada una de las

entradas en blanco de dicha tabla.

V1

[V]

0

5

Zona

VB

[V]

IB

[mA]

IE

[mA]

IC

[mA]

Tabla A.12: Análisis Figura A.28

204

>9@

KIH ,&

5 >. @

9&

9

5 >. @

,%

N TE

AL LD 20

O 1

VA UT

LL FS

EJ M

O

S,

20

10

,(

Figura A.28: Circuito

RESPUESTA.

Caso 1. V1 = 0[V]. En este caso, la juntura base-emisor está cortada, lo

mismo ocurre en la juntura base-colector. En consecuencia el transistor

está en zona de corte. Por lo tanto:

IB = IC = IB = 0[mA]

EI

VB = V1 − R1 IB = 0[V]

©

R

Caso 2. V1 = 5[V]. En este caso la juntura base-emisor está ON. En

consecuencia:

VB = 0, 75[V]

(V1 − VB )[V]

= 0, 085[mA]

IB =

R1 [KΩ]

Suponiendo que el transistor está en ZAD:

IC = hFE IB = 4, 25[mA]

VC = 5 − R2 IC = 0, 75[V]

A. Ejercicios Resueltos

205

Esto implica que VBC = 0[V]. Por lo tanto la hipótesis de que el transistor

está en ZAD es correcta. Por último:

IE = IB + IC = 4, 335[mA]

En resumen:

ZC

ZAD

VB

[V]

0

0,75

IB

[mA]

0

0,085

IE

[mA]

0

4,335

IC

[mA]

0

4,25

10

Zona

N TE

AL LD 20

O 1

VA UT

LL FS

EJ M

O

S,

20

V1

[V]

0

5

Tabla A.13: Análisis Figura A.28

EJERCICIO 2.6 Determine la zona en la que se encuentra el transistor

de la Figura A.29 y también sus respectivas corrientes.

>9@

,5

5 >. @

5 >. @

,&

,5

,%

©

R

EI

5 >. @

K)( ,(

Figura A.29

RESPUESTA. Debido a que la fuente en la base es la misma que en

colector, se supondrá que el transistor está en ZS. De esto obtenemos

206

que:

VC = 0, 2[V]

Las resistencias R1 y R2 , están en paralelo, lo que implica que la resistencia equivalente en colector y la corriente en el colector son:

=

N TE

AL LD 20

O 1

VA UT

LL FS

EJ M

O

S,

20

IC =

1

1

+

=⇒ RC = 0, 5[KΩ]

R1 [KΩ] R2 [KΩ]

(10 − VC )[V]

= 19, 6[mA]

RC [KΩ]

10

1

RC [KΩ]

Considere ahora la rama base emisor. Suponiendo que los transistores

están en ZS, se cumplirı́a que:

VB = 0, 75[V]

(10 − VB )[V]

= 9, 25[mA]

IB =

R1 [KΩ]

©

R

EI

Por lo tanto y para que se cumpla la suposición de que el transistor

está en ZS:

IC < hFE IB

19, 6 < 9, 25 ⋅ 50

Como la desigualdad se cumple, entonces la suposición fue correcta. En

resumen:

Zona

ZS

VC

[V]

0,2

IB

[mA]

9,25

IE

[mA]

28,85

IC

[mA]

19,6

A. Ejercicios Resueltos

207

EJERCICIO 2.7 Para el circuito de la Figura A.30, complete los

valores de la Tabla. Suponga hFE = 100.

5[V ]

RC = 1[kΩ]

I RC

9

V0

T1

T2

IE

9

RB 2 = 10[kΩ]

N TE

AL LD 20

O 1

VA UT

LL FS

EJ M

O

S,

20

RB1 = 10[kΩ]

,&7

10

,&7

Figura A.30: Circuito

V2

[V]

0

0

5

5

0

A.I

Z.O.

T1

Z.O.

T2

ICT1

[mA]

ICT2

[mA]

IRC

[mA]

V0

[V]

R

1

2

3

4

5

6

V1

[V]

0

5

5

A.I

A.I

A.I

EI

Caso

©

RESPUESTA.

Caso 1: Dado que V1 = V2 = 0[V] ambos transistores se encuentras

en zona de corte, por lo que la corriente de los colectores de ambos

transistores es 0[mA]. Esto implica que:

IRC = ICT1 + ICT2 = 0[mA]

V0 = 5 − VRC = 5[V]

Caso 2: En este caso T2 está en zona de corte al igual que en el caso

208

anterior. Sin embargo T1 se encuentra en zona de saturación. Por lo

tanto:

ICT2 = 0[mA]

(5 − VCE1 )[V]

= 4, 8[mA]

1[KΩ]

= 5 − VRC = 5 − 4, 8 = 0, 2[V]

ICT1 = IRC =

V0

N TE

AL LD 20

O 1

VA UT

LL FS

EJ M

O

S,

20

10

Caso 3: Ahora ambos transistores se encuentran en zona de saturación.

Para simplificar el análisis se supone que la corriente IRC se distribuye

en igual proporción en ambos transistores (el valor exacto depende de

los parámetros de cada transistor). Luego:

(5 − VCE1 )[V]

= 4, 8[mA]

1[KΩ]

= ICT2 = 2, 4[mA]

IRC =

ICT1

V0 = 5 − VRC = 5 − 4, 8 = 0, 2[V]

R

EI

Caso 4: Para T1 se tiene alta impedancia por lo que éste se encuentra

en zona de corte, mientras T2 se encuentra en zona de saturación. En

consecuencia, toda la corriente que pasa por RC circula por el colector

de T2 . Luego:

©

ICT1 = 0[mA]

(5 − VCE1 )[V]

= 4, 8[mA]

1[KΩ]

= 5 − VRC = 5 − 4, 8 = 0, 2[V]

ICT2 = IRC =

V0

Caso 5: T1 se comporta de igual modo que en el caso anterior. Por otro

lado, debido a V2 , T2 se encuentra en zona de corte. Por lo tanto:

IRC = ICT1 + ICT2 = 0[mA]

V0 = 5 − VRC = 5[V]

A. Ejercicios Resueltos

209

Caso 6: En este caso ambos transistores se encuentran en zona de

corte, por lo que la corriente en los colectores es nula, mientras la salida

está dada por:

V0 = 5 − VRC = 5[V]

Con lo cual se completa la tabla con sus respectivos valores:

V1

[V]

0

5

5

A.I

A.I

A.I

Z.O.

T1

Z.C

Z.S

Z.S

Z.C

Z.C

Z.C

Z.O.

T2

Z.C

Z.C

Z.S

Z.S

Z.C

Z.C

ICT1

[mA]

0

4,8

2,4

0

0

0

ICT2

[mA]

0

0

2,4

4,8

0

0

IRC

[mA]

0

4,8

4,8

4,8

0

0

N TE

AL LD 20

O 1

VA UT

LL FS

EJ M

O

S,

20

1

2

3

4

5

6

V2

[V]

0

0

5

5

0

A.I

V0

[V]

5

0,2

0,2

0,2

5

5

10

Caso

>9 @

©

R

EI

EJERCICIO 2.8 Si en el punto I del circuito de la Figura A.31 se

aplican 0,2[V], determine la zona de operación de los transistores T1 y

T2 . Justifique su respuesta.

5 = >NΩ@

,5

9

7

,

7

Figura A.31: Circuito

210

RESPUESTA.

1. T1 : Es un transistor PNP. En este caso, la juntura C-B T1 está inversa. Además la juntura B-E de T1 siempre se encuentra directa.

Esto implica que T1 está en zona activa directa.

2. T2 : Dado I = 0, 2[V], se puede ver claramente que la juntura B-E

de T2 no alcanza a quedar directa. Además B-C de T2 también se

encuentra en corte. Esto implica que T2 está en zona de corte.

N TE

AL LD 20

O 1

VA UT

LL FS

EJ M

O

S,

20

10

EJERCICIO 2.9 Para el siguiente circuito, determine la zona de operación del transistor, las corrientes y el voltaje V0 .

>9 @

5& = >Ω@

5 = >Ω@

,

9;

,

,&

,%

9

7

,(

5 = >Ω@

©

R

EI

5( = >Ω@

Figura A.32

RESPUESTA. Para efectuar el análisis de una manera más sencilla,

se evaluará el voltaje y resistencia Thevenin de la entrada:

RTH =

VTH =

R1 ⋅ R2

R1 + R2

R2

⋅5

R1 + R2

211

A. Ejercicios Resueltos

>9 @

>9 @

5&

5&

,&

,%

5

97+

5 7+

,%

,(

,

,(

5(

5

5(

>9 @

N TE

AL LD 20

O 1

VA UT

LL FS

EJ M

O

S,

20

Figura A.33

10

,

,&

Ahora se supone que el transistor está en ZAD, en cuyo caso:

VTH − IB RTH − IE RE − 0, 75[V] = 0 [V]

Despejamos IB :

VTH − IE RE − 0, 75[V]

RTH

= hFE IB

IB =

IC

EI

IE = IB + IC = IB (1 + hFE )

©

R

Luego,

(

IB

1 + hFE

1+

RTH

)

=

IB =

VTH − 0, 75[V]

RTH

VTH − 0, 75[V]

RTH + 1 + hFE

Como HFE ≫ 1: IC ≈ IE .

Observación. El tipo de configuración del circuito de la Figura A.32, es

llamada polarización por división de tensión, cuyo propósito es facili-

212

tar la polarización necesaria para que la juntura base-emisor quede en

Z.A.D. Reemplazando los valores:

R1 = R2 = 400[Ω]

hFE = 100

RC = RE = 500[Ω]

RTH = 0, 2[KΩ]

10

VTH = 2, 5[V]

2, 5 − 0, 75

= 0, 0175[mA]

IB =

0, 2 + 1 + 100

IC = 1, 72[mA]

N TE

AL LD 20

O 1

VA UT

LL FS

EJ M

O

S,

20

IE = 1, 74[mA]

V0 = 5 − 1, 72 ⋅ 1, 5 = 4, 14[V]

EJERCICIO 2.10 Encontrar zona de operación de los transistores T1

y T2 , junto con sus respectivos voltajes, corrientes y V0 para los valores

de entrada tabulados. Determinar la función lógica implementada.

0

0

0

5

5

0

5

5

>9 @

R

EI

A

B

©

>NΩ@

9$

9

> N Ω @

7

9%

Figura A.34

> N Ω @

7

A. Ejercicios Resueltos

213

RESPUESTA. Dado que ambos transistores son simétricos, se

analizará el siguiente circuito:

>9 @

> NΩ@

,%

7

N TE

AL LD 20

O 1

VA UT

LL FS

EJ M

O

S,

20

9$

9

10

,&

> N Ω @

,(

Figura A.35

EI

Caso 1: Para A = 0[V] , la juntura JB−E de T1 está cortada, al igual que

la juntura JB−C , por lo tanto, el transistor se encuentra en Z.C., lo que

implica que: IB = IC = IE = 0[mA]. Por tanto V0 = 5[V], además de que

T1 se comporta como un circuito abierto.

©

R

Para A = 5[V], la juntura JB−E de T1 está directa, por lo que VBE =

0, 75[V]. Por lo tanto:

(5 − 0, 75)[V]

= 0, 425[mA]

10[KΩ]

(5 − VC )[V]

=

4, 7[KΩ]

= IC + IB

IB =

IC

IE

Suponiendo ZAD, se cumple que:

IC = hFE IB = 50 ⋅ 0, 425[mA] = 21, 25[mA]

214

Finalmente:

VC = 5[V] − 4, 7[KΩ] ⋅ 21, 25[mA] = −94, 875[V]

Lo que implica que T1 está en ZS, por lo cual:

VC = 0, 2[V]

N TE

AL LD 20

O 1

VA UT

LL FS

EJ M

O

S,

20

(5 − 0, 2)[V]

= 1, 021[mA]

4, 7[KΩ]

= 1, 446[mA]

IC =

IE

10

Y se cumple que:

V0 = 0, 2[V]

Caso 2: El análisis precedente permite concluir que mientras alguna de

las dos entradas esté en 5[V], la salida será V0 = 0, 2[V]. Por otro lado,

si ambas son 0[V], la salida queda en V0 = 5[V].

©

R

EI

A

0

0

5

5

B

0

5

0

5

S

5

0

0

0

Lo que corresponde a la función lógica NOR.

EJERCICIO 2.11 En el circuito de la Figura A.36, determinar el

estado de los diodos D1 , D2 , D3 , D4 y D5 ; la zona de operación de T1 ;

y V0 para:

A

B

0

0

0

5

5

0

5

5

A. Ejercicios Resueltos

215

9 FF

> N Ω @

'

> NΩ@

9

'

'

$1'

%

'

9

,%

,&

7

,(

> NΩ@

N TE

AL LD 20

O 1

VA UT

LL FS

EJ M

O

S,

20

'

9

25

10

$

Figura A.36: Circuito

RESPUESTA. En primer lugar, se observa que las entradas A y B

determinan V1 y V2 . Para determinar estos voltajes se utiliza el hecho

que D1 y D4 forman un Mı́n-Off y D2 y D3 un Max-Off, por lo tanto:

A

0

0

5

5

B

0

5

0

5

V1

0

4,25

4,25

4,25

V2

0,75

0,75

0,75

5

EI

Este análisis permite simplificar el circuito de la Figura A.36, de la siguiente forma:

©

R

9

> NΩ @

9

,%

,&

7

,(

Figura A.37: Circuito

9

216

Caso 1: Para que JB−E quede polarizada, V1 debe ser mayor que 1,5[V].

Cumpliéndose sólo cuando V2 = 5[V]. Suponiendo ZAD:

5 [V] − 1, 5[V]

= 0, 7[mA]

5[kΩ]

= hFE ⋅ IB = 70[mA]

IB =

IC

V0 = 4, 25 [V] − 70 [mA] ⋅ 4, 5 [kΩ] = −275[V]

N TE

AL LD 20

O 1

VA UT

LL FS

EJ M

O

S,

20

10

Lo cual es absurdo. Por lo tanto, el transistor se encuentra saturado

determinando que: V0 = 0, 2[V].

Caso 2: Para el caso en que V2 < 1, 5[V], JB−C queda OFF, por lo que

el transistor está cortado, lo cual implica que:

V0 = V1 = 4, 25[V]

{

Nótese que éste es el valor de V0 para los casos:

A = 5 [V] y B = 0[V]

A = 0 [V] y B = 5[V]

R

EI

Caso 3: Con V1 = 0[V] y V2 = 0, 75[V], el transistor está cortado,

dejando:

V0 = V1 = 0[V]

©

Entonces V0 está determinado según la siguiente tabla:

A

0

0

5

5

B

0

5

0

5

V0

5

4,25

4,25

0,2

Nótese que el circuito de la Figura A.36 implementa la función lógica

XOR (OR exclusivo).

A. Ejercicios Resueltos

217

EJERCICIO 2.12 Para el circuito de la Figura A.38, determinar

la zona de operación de T1 y T2 , junto con sus corrientes y voltajes

respectivos para A = 5[V] y A = 0[V].

>9 @

9;

$

7

9

,&

N TE

AL LD 20

O 1

VA UT

LL FS

EJ M

O

S,

20

> N Ω @

'

10

> N Ω @

9<

7

>Ω @

,5

Figura A.38: Circuito

R

EI

RESPUESTA.

©

Caso 1: Para A = 5[V]: se logra polarizar IB−E de T1 , y JB−E de T2 .

Suponiendo que T1 esta en ZS:

IC1

IB 1

IE1

5[V] − 0, 2[V]

= 2, 4[mA]

2[KΩ]

5[V] − 0, 75[V] − 0, 75[V]

= 0, 875[mA]

=

4[KΩ]

= IB1 + IC1 = 0, 875[mA] + 2, 4[mA] = 3, 275[mA]

=

Luego, dado Vx = 0, 2[V], D1 queda OFF, por lo que no circula corriente

218

por él, dejando IC2 = 0[mA]. Esto implica que T2 está en ZS, lo que a

su vez significa que: V0 = 0, 2[V].

VY

IR

IB2

= 0, 75[V]

VY

= 0, 93[mA]

=

0, 8[KΩ]

= IE1 − IR = 2, 345[mA]

N TE

AL LD 20

O 1

VA UT

LL FS

EJ M

O

S,

20

IE2 = IC2 + IB2 = 2, 345[mA]

10

IC2 = 0[mA]

©

R

EI

Caso 2: Para A = 0[V]: T1 y T2 están en Z.C., mientras que D1 está directo. Bajo esta condición, se cumple que: V0 = 0[V], Vx = 0, 75[V],

IC2 = 2, 125[mA].

A. Ejercicios Resueltos

219

Capı́tulo 3

EJERCICIO 3.1 Obtenga la función de transferencia del circuito de

la Figura A.39.

9&& >9@

5

5&

9%(

9L

N TE

AL LD 20

O 1

VA UT

LL FS

EJ M

O

S,

20

9

10

9

,'

9

Figura A.39: Circuito NAND

RESPUESTA. De acuerdo el método de análisis visto en el capı́tulo 1

y 2, para el circuito se puede establecer que:

R

EI

i) Si es que algunas de las entradas V1 , V2 o ambas, tienen un voltaje

menor o igual a 1,3[V], el transistor queda en ZC, en cuyo caso se

cumple que:

(A.1)

©

V0 = VCC = 5[V]

ii) Luego, si la menor de las entradas, o ambas, aumenta hasta que

Vi asuma un valor para dejar ON la juntura B-E, el transistor se

encuentra en ZAD., por lo que:

Vi ZC−ZAD = 2, 2[V]

(A.2)

Si se encuentra en ZAD, las ecuaciones que rigen el comportamiento circuital son las siguientes:

220

IB = ID

IC = hFE IB

V0 = VCC − IC RC

Lo que permite concluir que:

(A.3)

N TE

AL LD 20

O 1

VA UT

LL FS

EJ M

O

S,

20

10

V0 = VCC − hFE IDiodo RC

De acuerdo a la ecuación A.3, cuando el transistor se encuentra en

ZAD, la variación de V0 no depende directamente de Vi , sino de

ID , y éste se ve afectado por el valor que asuma Vi , por lo que en

el gráfico la pendiente en la ZAD es −(hFE RC /RB ).

iii) Si la menor de las entradas, o ambas, siguen aumentando, se llega

al punto donde el transistor se satura; es decir: V0 ≈ 0, 2[V], por

lo tanto: si Vi > Vi ZAD−ZS , entonces V0 = 0, 2[V].

Con esto, se obtiene la función de transferencia del circuito A.39.

(FXDFLyQ

©

R

VCC

EI

V0 (t )

(FXDFLyQ

(FXDFLyQ

0 ,2

ZAD

ZC

Vi−Z.C.−Z.A.D

(FXDFLyQ

Vi−Z.A.D−Z.S.

(FXDFLyQ

ZS

Vi (t )

Figura A.40: Gráfico función de transferencia del circuito de la Figura A.39

A. Ejercicios Resueltos

221

EJERCICIO 3.2 Obtenga la función de transferencia del circuito de

la Figura A.41, para lo cual cortocircuite ambas entradas y varı́e la señal

de excitación entre 0[V] y 5[V].

VCC = 5[V ]

RC

R1

10

N TE

AL LD 20

O 1

VA UT

LL FS

EJ M

O

S,

20

V1

V0

IC

RB I B

V2

Figura A.41: Circuito NAND

RESPUESTA. Al cortocircuitar las entradas, el circuito quedarı́a de

la siguiente forma:

VCC = 5[V ]

RC

Vi

RB I B

IC

V0

©

V

R

EI

R1

Figura A.42: Circuito NAND con entradas cortocircuitadaa

Siguiendo el mismo método de análisis que en el ejercicio anterior, se

puede establecer que:

i) Si V es un valor muy pequeño, Vi también lo será, por lo que la

juntura B-E estará en estado OFF, en consecuencia el transistor

222

se encuentra en ZC, se cumple que:

V0 = VCC = 5[V]

(A.4)

10

ii) Luego si V aumenta lo suficiente, para que Vi asuma un valor para

poder dejar ON la juntura B-E del transistor, el transistor entra

en ZAD. El umbral entre ZC y ZAD debido a los tres diodos en

serie es:

N TE

AL LD 20

O 1

VA UT

LL FS

EJ M

O

S,

20

Vi ZC−ZAD = 2, 95[V]

(A.5)

En ZAD las ecuaciones que rigen son las siguientes:

(Vi − 2, 25)

RB

= hFE IB

IB =

IC

V0 = VCC − IC RC

Con lo que se puede concluir:

(

)

(A.6)

R

EI

V0 = VCC − (Vi − 2, 25)

hFE RC

RB

©

Por lo que la pendiente que posee el gráfico cuando al transistor

se encuentra en ZAD es igual a −hFE RC /RB .

iii) Si V continua aumentando, llega a un punto en que el transistor

entra en ZS. El lı́mite entre ZAD y ZS ocurre cuando Vi asume un

valor tal que V0 sea aproximadamente 0,2[V]. Es decir:

0, 2 = VCC − (Vi ZAD−ZS − 2, 25)

Vi ZAD−ZS = (VCC − 0, 2)

hFE RC

RB

hFE RC

+ 2, 25[V]

RB

(A.7)

A. Ejercicios Resueltos

223

Si Vi > Vi ZAD−ZS , el transistor se encuentra saturado, en cuyo caso se

puede suponer V0 ≈ 0, 2[V]. Con esto se obtiene la siguiente función de

transferencia:

V0 (t )

(FXDFLyQ

VCC

(FXDFLyQ

RC

RB

N TE

AL LD 20

O 1

VA UT

LL FS

EJ M

O

S,

20

10

pendiente = − h FE

(FXDFLyQ

0 ,2

Z .S .

Z . A.D.

Z.C.

Vi−Z.C.−Z.A.D Vi−Z. A.D−Z.S.

(FXDFLyQ

(FXDFLyQ

Vi (t )

Figura A.43: Función de transferencia Ejercicio 3.2

EJERCICIO 3.3 Demuestre que el operador NOR es un operador

completo.

6 Ɩ

$

6 Ɩ

$

6 $Â%

©

$

R

EI

RESPUESTA. Se sabe que un operador completo debe poder sintetizar las tres operaciones lógicas del algebra de Boole. Por lo tanto:

&

$

6 $Â%

%

$

%

'

&

6 $%

%

Figura A.44

$

%

6 $%

224

Dadas las implementaciones anteriores basadas sólo el compuertas NOR

queda demostrado que dicha compuerta es un operador completo. Se

adjuntan las tablas de verdad para mayor entendimiento.

Inversor:

A

0

1

S=A NOR A

1

0

NOT A

1

0

A

B

0

0

1

1

0

1

0

1

N TE

AL LD 20

O 1

VA UT

LL FS

EJ M

O

S,

20

10

And:

C=

A NOR A

1

1

0

0

B

0

1

0

1

C=A NOR B

1

0

0

0

S=

C NOR D

0

0

0

1

S=C NOR C

0

1

1

1

A AND B

0

0

0

1

A OR B

0

1

1

1

©

R

A

0

0

1

1

EI

Or:

D=

B NOR B

1

0

1

0

EJERCICIO 3.4 Deduzca un método para implementar cualquier función lógica utilizando solamente compuertas NOR. Ayuda: proceda en

forma análoga a la forma en que se usa solamente NAND’s para implementar cualquier función lógica. En este caso se debe intercambiar el rol

de los operadores AND y OR y también se debe intercambiar el rol de

los valores 0 y 1.

RESPUESTA. Al igual que para la implementación con NAND’s se

sintetiza cada operador lógico por medio de la compuerta(en este caso

NOR). Este método es igual de ineficiente que el descrito en el capı́tulo

A. Ejercicios Resueltos

225

para las compuertas NAND ya que también requiere muchas compuertas

para implementar la función lógica.

En este caso un método más eficaz consiste en escribir la función lógica

como un producto de sumas.

Los pasos a seguir son los siguientes(considerando que la función

está minimizada):

N TE

AL LD 20

O 1

VA UT

LL FS

EJ M

O

S,

20

10

1. La función debe estar minimizada y escrita como producto de

sumas.

2. Para cada variable de entrada generar su complemento (al igual

que en el método en base a compuertas NAND, es conveniente

hacerlo en base a NOT’s).

3. Existen dos niveles de compuertas NOR.

4. Por cada término de la función se asigna un NOR en el nivel 1.

5. Para cada variable que forma parte de un término se conecta la

señal al NOR correspondiente(o su complemento).

R

EI

6. La salida de cada uno de los NOR’s del nivel 1 se conecta a una

de las entradas del NOR del nivel 2.

©

7. La salida del NOR del nivel 2 entrega la función lógica que se desea

implementar.

A modo de ejemplo para aplicar el método se tiene la siguiente función:

f(A, B, C, D) = (A + B) ⋅ (B + C)

El diagrama en base a compuertas NOR de acuerdo al método es el

siguiente:

226

$

$

%

%

&

&

6

10

Figura A.45

N TE

AL LD 20

O 1

VA UT

LL FS

EJ M

O

S,

20

Para comprobar que el método es correcto se muestran las tablas de

verdad de la función implementada con los operadores Booleanos y luego

en base a compuertas NOR:

B

0

0

1

1

0

0

1

1

C

0

1

0

1

0

1

0

1

(A + B)

1

1

0

0

1

1

1

1

(B + C)

1

0

1

1

1

0

1

1

S = (A + B)(B + C)

1

0

0

0

1

0

1

1

A

B

C

A NOR B

B NOR C

0

0

0

0

1

1

1

1

0

0

1

1

0

0

1

1

0

1

0

1

0

1

0

1

0

0

1

1

0

0

0

0

0

1

0

0

0

1

0

0

©

R

EI

A

0

0

0

0

1

1

1

1

S=

(A NOR B) NOR (B NOR C)

1

0

0

0

1

0

1

1

Las salidas son las mismas, por lo tanto el método es correcto.

A. Ejercicios Resueltos

227

EJERCICIO 3.5 Diseñe un circuito AND.

RESPUESTA. De antemano tenemos los circuitos de las compuertas

NAND, NOR y NOT. Del trabajo con lógica se obtiene lo siguiente:

AND = NOT (NAND)

N TE

AL LD 20

O 1

VA UT

LL FS

EJ M

O

S,

20

10

Por lo tanto simplemente basta con agregar un negador a la salida de

un NAND, el circuito queda como sigue:

9&& >9@

5&

5

,

$

,%

9;

9

5&

9

6

5%

5%

,%

9

%

R

EI

Figura A.46: Circuito que implementa la función lógica AND

©

EJERCICIO 3.6 Diseñe un circuito OR.

RESPUESTA. Considerando que ya se dispone de los circuitos que implementan las funciones NAND, NOR y NOT, un OR se puede obtener

mediante la siguiente función:

OR = NOT (NOR)

Por lo tanto simplemente basta con agregar un negador a la salida de

un NOR, con lo cual el circuito queda como sigue:

228

9&& >9@

5&

5&

9

,%

$

5%

9;

9

6

5%

9

N TE

AL LD 20

O 1

VA UT

LL FS

EJ M

O

S,

20

5

10

%

Figura A.47: Circuito que implementa un OR

EJERCICIO 3.7 Determinar el valor de la salida cuando se realiza

un Wired-AND entre las salidas de n compuertas NOT.

RESPUESTA. El circuito para este ejercicio es el mismo que el que se

vio en el Capı́tulo 3 para un Wired-AND, con la única diferencia que se

enfrenta a una salida con n entradas en vez de dos.

©

R

EI

Caso 1. Todas las entradas en 0[V]. Para este caso, todos los

transistores quedan en ZC. Bajo esta condición todas las corrientes

de colector serán 0[mA], originando una salida S = 5[V].

Caso 2. Todas las entradas en 5[V].

Para este caso, todos los transistores estarán en ZS, esto implica

que la salida será 0,2[V].

Caso 3. X entradas en 5[V] y (n − X) entradas en 0[V], con 1 ≤

X ≤ n.

La cantidad de entradas no variará el resultado, solo producirá variaciones en las corrientes en los colectores de los diferentes transistores. Bajo estas condiciones, la salida S será de 0,2[V],

la cual está determinada por los transistores en ZS. El resto de

A. Ejercicios Resueltos

229

los transistores se encuentran en ZC, por lo cual no influyen en el

valor de V0 .

Los análisis de los resultados previos se resumen en la siguiente función:

S=

n

∏

Ai

©

R

EI

N TE

AL LD 20

O 1

VA UT

LL FS

EJ M

O

S,

20

10

i=1