SISTEMAS DIGITALES Tema 7: Latches, Flip-Flops y

Anuncio

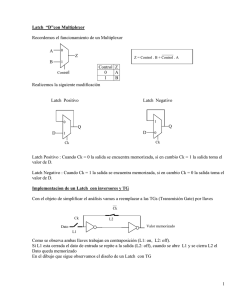

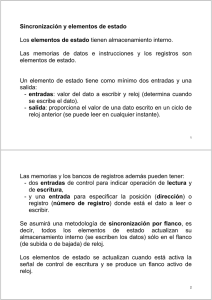

EIE 446 - SISTEMAS DIGITALES Tema 7: Latches, Flip-Flops y Temporizadores Nombre del curso: “Sistemas Digitales” Nombre del docente: Héctor Vargas OBJETIVOS DE LA UNIDAD ● Utilizar puertas lógicas para construir latches básicos. ● Estudiar la diferencia entre un latch S-R y un latch D. ● Conocer la diferencia entre un latch y un flip-flop. ● Explicar en que se diferencian los flip-flops S-R, D y J-K. ● Estudiar: Retardo de propagación, tiempo de establecimiento (setup time), tiempo de mantenimiento (hold time), frecuencia máxima de funcionamiento, ancho mínimo del impulso de reloj, disipación de potencia. ● Emplear flip-flops en aplicaciones sencillas. ● Estudiar los circuitos monoestables. ● Estudiar el temporizador 555 cuando se conecta para operar como multivibrador a-estable o como monoestable. LATCHES ● Un latch es un dispositivo de almacenamiento temporal que tiene dos estados estables SET y RESET (también llamados biestables). Es una forma básica de memoria. ● El latch S-R (Set-Reset) es el tipo más básico. Puede ser construido mediante puertas NOR o NAND. Con puertas NOR el latch responde a entradas activas en ALTA. Con puertas NAND responde a entradas activas en BAJA. R S Q Q NOR Active-HIGH Latch S R Q Q NAND Active-LOW Latch LATCHES El latch S-R activo a nivel ALTO está en una condición de estado estable (latched = enganchado) cuando ambas entradas están a nivel BAJO. Asumamos que latch está inicialmente en estado RESET (Q = 0) y que las entradas están en sus niveles inactivos (0). Para pasar el latch a estado SET (Q = 1), una señal momentánea a nivel ALTO se aplica a la entrada S mientras la entrada R permanece a nivel BAJO. 0 R Para poner el latch en estado RESET (Q = 0), una señal en estado ALTO se aplica momentáneamente a la entrada R mientras la entrada S permanece en estado BAJO. 0 R 1 0 10 0 S 1 0 1 0 0 S Q Latch inicialmente RESET Q Q Latch initially SET Q LATCHES El latch S-R activo a nivel BAJO está en una condición de estado estable (latched = enganchado) cuando ambas entradas están a nivel ALTO. Asumamos que el latch está inicialmente en estado RESET (Q = 0) y que las entradas están en su nivel inactivo (1). Para pasar el latch a estado SET (Q = 1), una señal momentánea a nivel BAJO se aplica a la entrada S mientras la entrada R permanece a nivel ALTO. 1 S 01 1 R 1 S Para poner el latch en estado RESET una señal momentánea a nivel BAJO se aplica a la entrada R mientras S es ALTO. No aplicar nunca un nivel activo a la entrada SET y RESET al mismo tiempo (estado inválido). 1 0 1 0 Q Latch inicialmente RESET Q Q Latch initially 1 SET 0 1R Q LATCHES La tabla de verdad de un latch S-R con entrada activa a nivel BAJO se muestra a continuación. Entradas Salidas S R Q Q 1 0 1 0 1 1 0 0 NC 1 0 1 NC 0 1 1 Comentarios No cambio SET RESET No valido LATCHES El latch S-R activo a nivel BAJO está disponible como C.I. 74LS279A. Cuenta con cuatro latches internos con dos que tienen entradas S. Para poner en estado SET cualquiera de los latches, la línea S debe ser puesta en bajo. (2) (3) (1) (6) S-R latches se usan frecuentemente para circuitos que eliminan el rebote de conmutación: (5) (11) (12) (10) VCC (15) 2 1 Q S S R R (14) Posición 1a2 Posición 2a1 1S1 1S2 1R 2S (4) 1Q (7) 2Q (9) 3Q (13) 4Q 2R 3S1 3S2 3R 4S 4R 74LS279A LATCHES Un latch con entrada de habilitación es una variación del latch básico. Este latch tiene una entrada adicional, llamada de habilitación o enable (EN) que debe estar en ALTO a fin de que el latch responda a las entradas S y R. Mostrar la salida Q en relación a las señales de entrada. Asuma que Q comienza en BAJO. S Q EN Q R Recordar que S y R están solamente activas cuando EN es ALTO. S R EN Q LATCHES El latch D con entrada de habilitación es una variación del latch S-R ya que combina las entradas S y R en una única entrada D como se muestra a continuación: D Q EN D Q EN Q Q Una regla de funcionamiento simple para el latch D es: Q sigue a D cuando la entrada Enable está activa. LATCHES La tabla de verdad de un latch D resume su modo de operación. Si EN está en un nivel BAJO, entonces no hay cambio en la salida y está enganchado. Entradas Salidas D EN Q Q Comentarios 0 1 X 1 1 0 0 1 Q0 1 0 Q0 RESET SET No cambio LATCHES D Determinar la salida Q para el latch D, de acuerdo a las entradas dadas. Q EN Q D EN Q Observe que la entrada Enable (EN) no está activo durante estos tiempos, de modo que la salida está enganchada. FLIP-FLOPS Un flip-flop difiere de un latch en la manera en que cambia de estados. Un flipflop es un dispositivo disparado por una señal de reloj, en el cual solamente un flanco del pulso de reloj determina cuando se ingresa un nuevo bit. El flanco activo puede ser positivo o negativo. D Q C Indicador de entrada dinámico D Q C Q (a) Positive edge-triggered Q (b) Negative edge-triggered FLIP-FLOPS La tabla de verdad para un flip-flop tipo D disparado por flanco positivo muestra una flecha hacia arriba para recordar que es sensible a su entrada D solamente en el flanco de subida de la señal de reloj; En cualquier otro caso, está enganchado. La tabla de verdad para un flip-flop tipo D disparado por flanco negativo es idéntica excepto por la dirección de la flecha. Entradas D 1 0 CLK Salidas Entradas Q Q Comentarios D 1 0 0 1 SET RESET 1 0 (a) Disparado por flanco positivo CLK Salidas Q Q Comentarios 1 0 0 1 SET RESET (b) Disparado por flanco negativo FLIP-FLOPS El flip-flop tipo J-K es más versátil que el flip-flop tipo D. Además de la entrada de reloj, tiene dos entradas, etiquetadas como J y K. Cuando ambas entradas J y K = 1, la salida cambia de estado (bascula) en el flanco de reloj activo (en este caso, el flanco de subida). Entradas Salidas J K Q Q Comentarios 0 0 1 0 1 0 Q0 0 1 Q0 1 0 1 1 Q0 Q0 No cambio RESET SET Basculación CLK FLIP-FLOPS Q J CLK Determinar la salida Q para el flip-flop J-K, dadas las entradas que se muestran. K Q Observe que la salida cambia en el flanco de subida de la señal de reloj. Set CLK J K Q Basculación Set Latch FLIP-FLOPS Un flip-flop tipo D no tiene un modo de basculación como el flip-flop J-K, pero se puede bascular su modo de conmutación al conectar Q hacia atrás a la entrada D como se muestra en la figura de abajo. Esto es útil en algunos contadores que se verán en el Capítulo 8. Por ejemplo, si Q es BAJO, Q es ALTO y el flip-flop cambiará en el próximo flanco de reloj. Dado que el flip-flop sólo cambia durante su flanco activo, la salida solamente cambiará una vez por cada pulso de reloj. D CLK Q CLK Q Flip-flop D conectado para conmutar de forma alterna FLIP-FLOPS Otro tipo de flip-flop que conviene mencionar es el flip-flop tipo T. al igual que el flip-flop tipo D tiene sólo una entrada de excitación. Sin embargo, difiere del anterior en su comportamiento de transición. T Q C Indicador de entrada dinámico T Q C Q (a) Positive edge-triggered Q (b) Negative edge-triggered FLIP-FLOPS La tabla de verdad del flip-flop tipo T se encuentran a continuación. Si observamos la tabla a podemos entender el funcionamiento de este dispositivo durante la transición de estado. Cuando la entrada al dispositivo es un 1 la salida (o estado siguiente después de la transición) es el complemento de la salida actual. Si la entrada es un 0, entonces se mantiene la salida actual. Entradas T 1 0 CLK Salidas Entradas Q Q Comentarios T Q Q 0 1 Cambio No Cambio 1 0 (a) Disparado por flanco positivo CLK Salidas Q Q Comentarios Q Q 0 1 Cambio No cambio (b) Disparado por flanco negativo FLIP-FLOPS Las entradas síncronas se transfieren durante el flanco de disparo de reloj (por ejemplo, la entrada D o J-K). La mayoría de los flip-flops tienen otras entradas que son asíncronas, lo cual quiere decir que ellas afectan a la salida independientemente del reloj. PRE Dos de tales entradas se etiquetan comúnmente como preset (PRE, inicialización) y clear (CLR, borrado). Estas entradas se activan usualmente en BAJA. Un flip-flop J-K con preset y clear activas en BAJO se muestra en la figura de la derecha. Q J CLK Q K CLR PRE FLIP-FLOPS Q J Determinar la salida Q para el flip-flop J-K, dadas las entradas que se muestran. CLK Q K Set Basculación Set Reset Basculación Latch CLR CLK J K PRE CLR Q Set Reset CARACTERÍSTICAS DE OPERACIÓN DE LOS FLIP-FLOPS El retardo de propagación se especifica como el tiempo requerido para que se produzca un cambio en la salida una vez que se ha aplicado un cambio en la entrada. Se mide entre el 50% del nivel de la señal de reloj hasta el 50% del nivel en la transición de salida. 50% point on triggering edge CLK CLK Q 50% point on LOW-toHIGH transition of Q tPLH 50% point 50% point on HIGH-toLOW transition of Q Q tPHL El retardo de propagación típico para el 74AHC de la familia (CMOS) es 4 ns. Para aplicaciones específicas existen componentes con retardos menores. CARACTERÍSTICAS DE OPERACIÓN DE LOS FLIP-FLOPS Otra especificación de retardo de propagación es el tiempo requerido por una entrada asincrónica que causa un cambio en la salida. De nuevo, se mide desde entre los 50% de los niveles. La familia 74AHC ha especificado retardo de tiempo inferiores a 5 ns. PRE 50% point 50% point Q tPHL CLR 50% point 50% point Q tPLH CARACTERÍSTICAS DE OPERACIÓN DE LOS FLIP-FLOPS Tiempo de establecimiento (set-up time) y tiempo de mantenimiento (hold time) son los tiempos requeridos antes y después de la transición de reloj en que los datos deben estar presentes para que sea una temporización de reloj confiable en el flip-flop. Set-up time es el mínimo tiempo para que los datos deben mantenerse presentes antes de que se haga presente el impulso de reloj. Hold time es el mínimo tiempo para que los datos deben mantenerse presentes después de que se haga presente el impulso de reloj. D CLK Set-up time, ts D CLK Hold time, tH CARACTERÍSTICAS DE OPERACIÓN DE LOS FLIP-FLOPS Otras especificaciones incluyen la máxima frecuencia de reloj, mínimo ancho de pulso para varias entradas, y disipación de potencia. La disipación de potencia es el producto del voltaje aplicado y la corriente promedio requerida. Una comparación útil entre familias lógicas es el producto velocidadpotencia que utiliza dos de las especificaciones vistas anteriormente: el retardo de propagación promedio y la disipación de potencia promedio. La unidad es la energía. ¿Cuál es el producto velocidad-potencia para el C.I. 74AHC74A? Usar los datos de la tabla 9-5 para determinar la respuesta. De la tabla 9-5, el retardo de propagación promedio es 4.6 ns. La potencia disipada en reposo es 1.1 mW. Por lo tanto, el producto velocidad-potencia es 5 pJ APLICACIONES DE LOS FLIP-FLOPS Las principales aplicaciones con flip-flops son para almacenamiento temporal de datos, divisores de frecuencia y contadores (los cuales se verán en la próxima unidad). Líneas de salida Q0 D C R Q1 D Típicamente, en las aplicaciones de almacenamiento de datos, un grupo de flipflops se conectan a líneas de datos en paralelo y señal de reloj. Los datos se almacenan hasta que ocurre un pulso de reloj. C R Q2 D Líneas de entrada de datos en paralelo C R Q3 D Reloj C R Borrado APLICACIONES DE LOS FLIP-FLOPS Para división de frecuencia, es fácil usar un flip-flop en modo de basculación (toogle) o encadenar una serie de flip-flops en modo basculación para seguir dividiendo por 2. HIGH Un flip-flop dividirá fin por 2, dos flip-flops dividirán fin por 4 (y así sucesivamente). Un beneficio adicional de la fin división de frecuencia es que la salida tiene un ciclo de trabajo exacto de 50% de la entrada. fin Formas de onda: fout HIGH QA J CLK K QB J CLK K fout MONOESTABLES Un multivibrador monostable es un dispositivo que tiene solamente un estado estable. Cuando se dispara, va a su estado inestable por un periodo de tiempo predeterminado, luego retorna a su estado estable. +V Para la mayoría de los monoestables, El periodo de tiempo en el estado inestable (tW) se determina por medio de un circuito RC. REXT CEXT CX Q RX/CX Disparo Q Disparo Q tW MONOESTABLES Un monoestable no-redisparable no responde a un disparo que ocurre durante un estado inestable. Por el contrario, los monoestables redisparables si responden a un disparo durante un estado inestable. Si el disparo ocurre durante el estado inestable, el estado se extiende por una cantidad igual al ancho del pulso. Monoestable redisparable: Disparado Redisparo Q tW MONOESTABLES Una aplicación para un monoestable re-disparable es un circuito detector de fallo de energía. Los disparos se derivan desde una fuente de energía ac que dispara el monoestable de forma continua. En el caso de un fallo de energía, el monoestable no se dispara y una alarma se inicia para indicar tal anomalía. Disparo faltante debido a un fallo de energía Disparos derivados desde fuente ac Redisparos Q Redisparos Indicación de fallo de energía tW tW tW EL TEMPORIZADOR 555 El temporizador 555 se puede configurar de varias maneras, incluyendo la posibilidad de configurarlo como monoestable. Un monoestable básico se muestra en la figura. El ancho de pulso se determina por las constantes R1C1 y es aproximadamente tW = 1.1R1C1. +VCC (4) (8) R1 (7) RESET VCC DISCH (6) El disparo es un pulso negativo. (2) C1 (3) THRES OUT TRIG CONT GND (1) (5) tW = 1.1R1C1 EL TEMPORIZADOR 555 Determinar el ancho de pulso para el circuito que se muestra en la figura. tW = 1.1R1C1 = 1.1(10 kW)(2.2 mF) = 24.2 ms +VCC +15 V (4) R1 10 kW (7) RESET (8) VCC DISCH (6) (2) C1 2.2 mF (3) THRES OUT TRIG CONT GND (1) (5) tW = 1.1R1C1 EL TEMPORIZADOR 555 El 555 se puede configurar también como un multivibrador aestable básico como se muestra en el siguiente circuito. En este circuito C1 carga a través de R1 y R2 y descarga a través de R2. La frecuencia de salida está dada por: +VCC f 1.44 R1 2R2 C1 (4) R1 La frecuencia y ciclo de trabajo se configuran por R2 estos componentes. C1 (7) (6) (2) (8) RESET DISCH VCC THRES OUT TRIG CONT GND (1) (3) (5) EL TEMPORIZADOR 555 Dadas las componentes, se puede leer la respuesta desde el gráfico. Alternativamente, se puede usar el gráfico para tomar los componentes de una frecuencia deseada. +VCC 100 10 (7) 1.0 1 kW W R2 0.1 (6) (2) 0.01 0.001 0.1 (8) RESET DISCH VCC THRES OUT kW 10 0k 10 W MW 1M 10 C1 (mF) (4) R1 C1 TRIG CONT GND (1) 1.0 10 100 f (Hz) 1.0k 10k 100k (3) (5) PALABRAS CLAVES DE LA UNIDAD Latch Un circuito digital biestable usado para almacenar un bit. Biestable Que tiene dos estados estables. Los Latches y flip-flops son biestables multivibradores. Reloj Un entrada de disparo de un flip-flop. flip-flop D Un tipo de biestable multivibrador en que la salida asume el estado de la entrada D en el flanco de disparo de un pulso de reloj. flip-flop J-K Un tipo de flip-flop que puede operar en los modos SET, RESET, nocambio, y basculación. PALABRAS CLAVES DE LA UNIDAD Retardo de El intervalo de tiempo requerido desde que una señal de propagación entrada ha sido aplicada y se observa el resultado de cambio en la salida. Tiempo de Intervalo de tiempo mínimo que los niveles lógicos deben establecimiento mantenerse constantes en las entradas antes de que llegue el flanco de disparo del impulso de reloj. Tiempo de Intervalo de tiempo mínimo que los niveles lógicos deben mantenimiento mantenerse constantes en las entradas después de que haya pasado el flanco de disparo del impulso de reloj. Temporizador Un circuito que se puede utilizar como un monoestables o como un oscilador. BIBLIOGRAFÍA Libro base: “Fundamentos de Sistemas Digitales”. Autor: Tomas L. Floyd. Libro complemento: “Principios de Diseño Digital”. Autor: Daniel D. Gaski.