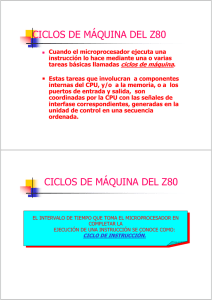

Un procesador de 8 bits: Z80-CPU

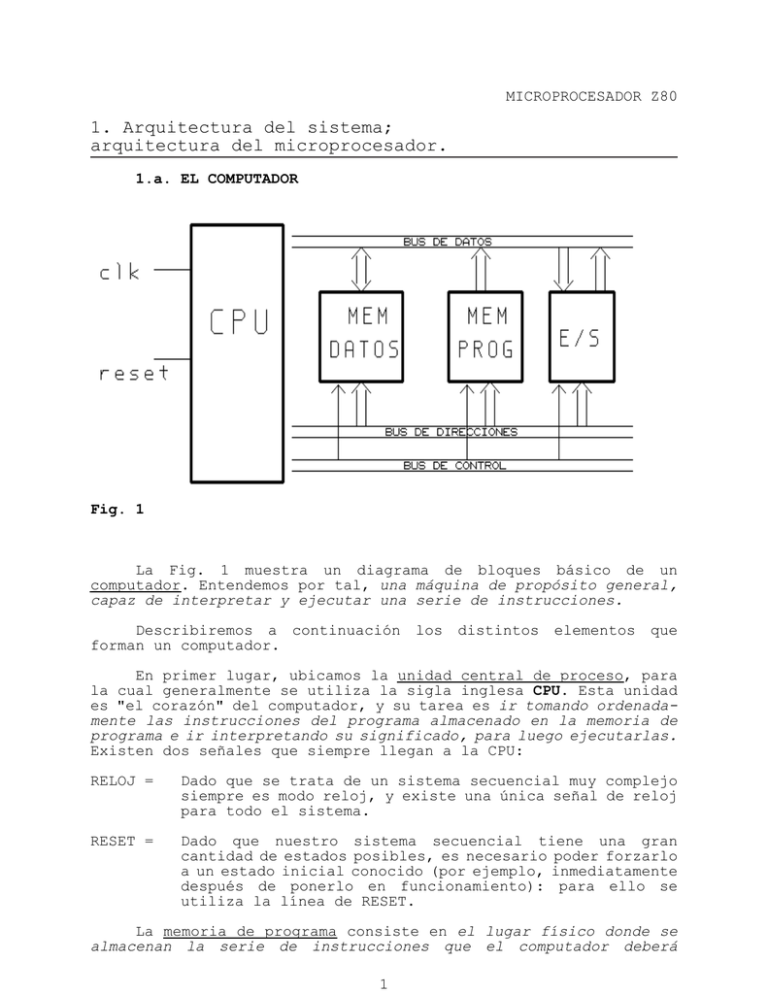

Anuncio