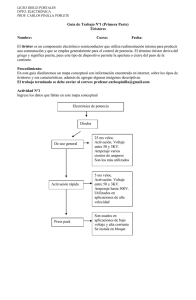

circuito de iluminación acoplado a un sistema reconocedor de voz

Anuncio