Examen Parcial IC

Anuncio

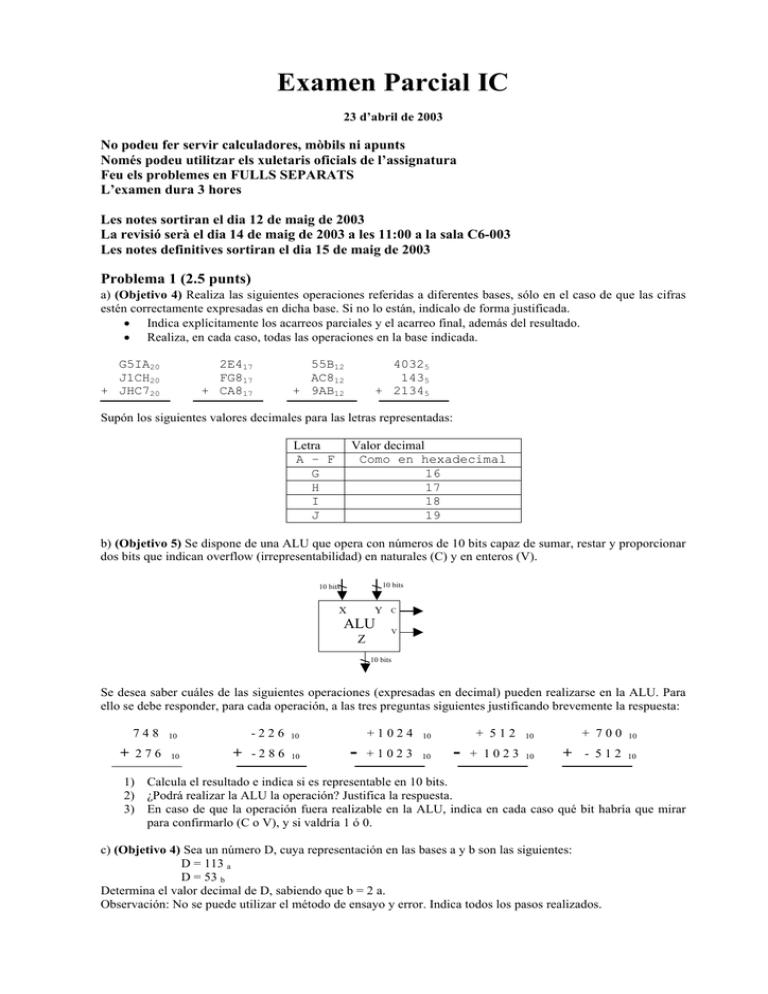

Examen Parcial IC 23 d’abril de 2003 No podeu fer servir calculadores, mòbils ni apunts Només podeu utilitzar els xuletaris oficials de l’assignatura Feu els problemes en FULLS SEPARATS L’examen dura 3 hores Les notes sortiran el dia 12 de maig de 2003 La revisió serà el dia 14 de maig de 2003 a les 11:00 a la sala C6-003 Les notes definitives sortiran el dia 15 de maig de 2003 Problema 1 (2.5 punts) a) (Objetivo 4) Realiza las siguientes operaciones referidas a diferentes bases, sólo en el caso de que las cifras estén correctamente expresadas en dicha base. Si no lo están, indícalo de forma justificada. • Indica explícitamente los acarreos parciales y el acarreo final, además del resultado. • Realiza, en cada caso, todas las operaciones en la base indicada. G5IA20 J1CH20 + JHC720 2E417 FG817 + CA817 55B12 AC812 + 9AB12 40325 1435 + 21345 Supón los siguientes valores decimales para las letras representadas: Letra A – F G H I J Valor decimal Como en hexadecimal 16 17 18 19 b) (Objetivo 5) Se dispone de una ALU que opera con números de 10 bits capaz de sumar, restar y proporcionar dos bits que indican overflow (irrepresentabilidad) en naturales (C) y en enteros (V). 10 bits 10 bits X Y ALU Z C V 10 bits Se desea saber cuáles de las siguientes operaciones (expresadas en decimal) pueden realizarse en la ALU. Para ello se debe responder, para cada operación, a las tres preguntas siguientes justificando brevemente la respuesta: 748 10 -226 10 + 276 10 + -286 10 - +1024 10 +1023 10 - + 512 10 + 700 10 + 1023 10 + - 512 10 1) Calcula el resultado e indica si es representable en 10 bits. 2) ¿Podrá realizar la ALU la operación? Justifica la respuesta. 3) En caso de que la operación fuera realizable en la ALU, indica en cada caso qué bit habría que mirar para confirmarlo (C o V), y si valdría 1 ó 0. c) (Objetivo 4) Sea un número D, cuya representación en las bases a y b son las siguientes: D = 113 a D = 53 b Determina el valor decimal de D, sabiendo que b = 2 a. Observación: No se puede utilizar el método de ensayo y error. Indica todos los pasos realizados. Problema 2 (4 punts) a) (Objectiu 6.3) Doneu l’expressió algebraica de la sortida d’un multiplexor 4 a 1 (per exemple, el que hi ha al xuletari). Donat el circuit de la figura: a b • • x • z • y • 0 1 f 2 3 + c d b) (Objectiu 6.2) Obteniu l’expressió algebraica de f(a,b,c,d) del circuit de la figura. Nota: No cal simplificar. Doneu l’expressió que surti directament d’analitzar el circuit anterior. c) (Objectiu 6.2, 6.4) Calculeu la forma canònica en suma de minterms a partir de la taula de veritat d’f(a,b,c,d). d) (Objectiu 6.4) D’acord amb la implementació interna del multiplexor que heu obtingut a l’apartat a): • Indiqueu el nombre de portes que es necessitarien en la implementació interna de f(a,b,c,d) amb un multiplexor 16 a 1. • Indiqueu també el nombre de portes utilitzades en el circuit de la figura (incloent les portes que hi ha dintre del multiplexor 4 a 1 de la figura) Nota: les portes lògiques poden tenir les entrades que calguin. e) (Objectiu 6.2) Sabem que per al circuit de la figura tenim els següents retards: NOR=15ns, AND=10ns, XOR=20ns, Multiplexor=25ns, i que els retards del circuit de l’apartat d) són: NOT=5ns, AND=15ns i OR=20ns. Quin circuit és el millor pel que fa a retard? Perquè? g) (Objectiu 6.2) Ompliu el cronograma del full adjunt tenint en compte els retards indicats a l’apartat e) per al circuit de la figura. Indiqueu sota cada transició l’instant de temps (en ns) en el que es produeix. Problema 3 (3.5 punts) Se dispone de un circuito de control de acceso basado en un código secreto de cuatro dígitos decimales (similar al de un cajero automático). La figura siguiente muestra el esquema de bloques del circuito. ok 0 1 2 3 4 5 6 7 8 9 ok C numero 4 4 Din 1 PE SL 2 BANCO DE Dout teclado + C 1 - ok 1 REGISTROS 4 SE clk 1 inicio SISTEMA LÓGICO SECUENCIAL S2 S1 clk S0 SISTEMA LÓGICO COMBINACIONAL 4 A 1 2 3 4 VISUALIZADOR El objetivo de este diseño es almacenar los 4 dígitos introducidos por el teclado en un banco de registros. El circuito dispone de los siguientes bloques: teclado, banco de registros, sistema lógico secuencial, sistema lógico combinacional y visualizador. La descripción del funcionamiento de cada bloque es la siguiente: Teclado: § Cuando se pulsa la tecla <ok>, el teclado proporciona en el bus de salida numero el último dígito pulsado por el usuario y se activa a 1 la señal de salida ok. Banco de registros: § Contiene cuatro registros de cuatro bits cada uno y los siguientes buses: entrada de datos (Din), salida de datos (Dout), dirección de lectura (SL), dirección de escritura (SE) y permiso de escritura (PE). La lógica combinacional que hay conectada a la entrada del permiso de escritura del banco de registro se encarga de que el registro adecuado se escriba únicamente cuando la señal ok vale 1 y no se ha finalizado la secuencia. Sistema Lógico Secuencial (SLS): § La señal inicio es una entrada asíncrona controlada por un sistema externo que sirve para inicializar el SLS. § El SLS (junto con el teclado) se encarga de gestionar la escritura de los cuatro dígitos que integran la secuencia a reconocer en el Banco de Registros, de forma que éstos queden memorizados en el orden introducido. Tras escribirlos, el sistema queda en espera hasta que un sistema externo vuelva a reiniciarlo. Sistema Lógico Combinacional (SLC): § A partir de la señal de entrada S, el SLC se encarga de generar adecuadamente la señal de activación A de 4 bits que enciende las luces del sistema visualizador. La señal S codifica en binario natural (de 0 a 4) el número de dígitos introducidos. No puede encenderse más de una luz simultáneamente. La posición de la luz encendida, de izquierda a derecha, indica el número de dígitos introducidos. Inicialmente, todas las luces están apagadas. Visualizador: § Es una agrupación de cuatro luces, cada una de ellas controlada por un bit distinto. Mientras el bit Ai vale uno, la luz i-ésima está encendida. Mientras vale cero, está apagada. El bit A3 controla la luz de la derecha. El bit A0 controla la luz de la izquierda. El funcionamiento general del circuito de control de acceso es el siguiente: § § § § § § El usuario introduce los dígitos de uno en uno, hasta completar un total de 4. Después de cada dígito debe pulsar la tecla <ok> (confirmar). (atención, su funcionamiento es distinto del de un cajero automático). Supóngase que el usuario nunca aprieta la tecla <ok> antes de introducir el dígito. Por tanto, siempre tiene lugar la secuencia <dígito>, <ok>, <dígito>, <ok>, .... no siendo posibles situaciones del tipo <ok>, <ok> consecutivamente. Después de pulsar la tecla <ok> se encenderá en el visualizador una luz que indique el número de dígitos introducidos hasta el momento. La luz de la izquierda indica que se ha introducido 1 dígito. La luz de la derecha indica que se han introducido los 4. Cada dígito introducido y confirmado se memorizará en el banco de registros en su posición correspondiente (el primer dígito en la posición 0, el último dígito en la posición 3). Si el usuario desea corregir la secuencia introducida, debe presionar la tecla corregir <C>. Si se aprieta varias veces la tecla <C>, el sistema cancela tantos dígitos introducidos como veces se haya apretado dicha tecla (siendo posible cancelar dígito a dígito hasta regresar al estado inicial). Si se sigue apretando la tecla <C> en el estado inicial, el sistema permanece en ese estado. Sin embargo, una vez introducido el cuarto dígito y apretada la tecla <ok>, ya no puede corregirse la secuencia hasta que llegue una señal de inicio desde el exterior y el reconocimiento de secuencia comience de nuevo. Las señales ok y C permanecen a 1 una vez han sido pulsadas las teclas correspondientes hasta que llega el siguiente flanco de reloj. El tiempo de ciclo del reloj del sistema es mucho menor que el tiempo de introducción de dígitos por parte del usuario. Si se aprietan simultáneamente las teclas <ok> y <C>, el sistema actúa como si sólo se hubiese pulsado <C>. Contesta a los siguientes apartados: a) (Objetivo 6.3) Usando un único bloque del chuletario del tamaño necesario, diseña el SLC para que cumpla la funcionalidad de activar la luz adecuada en función del número de dígitos que se hayan introducido hasta el momento. Indica claramente cómo se conectan las entradas y salidas del bloque a las señales del SLS y del visualizador. b) (Objetivo 6) Indica las entradas y salidas de cada uno de los estados del SLS según el modelo de Moore (leyenda del grafo) c) (Objetivo 6) Especifica el número de estados necesarios del SLS, la funcionalidad realizada en cada estado y la salida de cada uno de ellos. d) (Objetivo 6.5) Dibuja el diagrama de estados (grafo) del SLS según el modelo de Moore. Cognoms: ______________________________________________________________________ Nom: _______________________ DNI: ___________________ x y z f 100 200 300 400 500 t(ns)