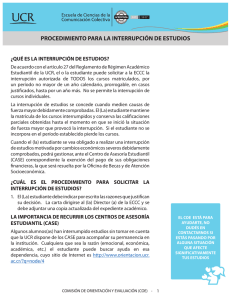

universidad tecnologica nacional

Anuncio