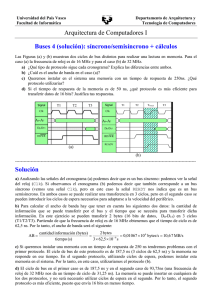

Diseño de una interfaz de memoria para atender a un bus de 4 vías.

Anuncio

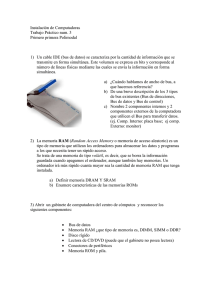

Buses y Periféricos. Curso 2008/2009 Práctica 1. Diseño. Diseño de una interfaz de memoria para atender a un bus de 4 vías. V0 V1 V2 V3 DM7:DM0 O7:O0 AM3:AM0 W A15:A2 W/R Tr T ¿? Sel BH3:BH0 Registros 8 bits Módulo Memoria Multiplexor Buffers Tri-Estado Unidad de control Demultiplexor Este esquema pretende ser una aproximación a una interfaz de memoria para atender a un bus demultiplexado de cuatro vías. Consideramos una vía a un sub bus de tamaño 1 byte. Nuestro bus puede acarrear datos de tamaño 1 bytes, 2 bytes y 4 bytes. Cuando lleva datos de 1 byte pueden fluir por cualquiera de las vías, siendo esto indicado por la señal BH correspondiente. (Si el byte va por la vía 3 la señal BH3 estará activa y las demás permanecerán inactivas). Cuando lleva datos de 2 bytes, estos pueden ir en dos vías consecutivas cualesquiera (V0 y V1, V1 y V2, V2 y V3 o V3 y V4) lo que estará pertinentemente indicado por las señales BH correspondientes. Observemos que las líneas de dirección son A15:A2. En efecto faltan A1 y A0. Esto significa que toda dirección que aparece en el bus es múltiplo de 4, como queriendo apuntar al primero de un bloque de 4 bytes. A continuación las señales BH indicarán por cuales de esos cuatro bytes se está interesado. Por ejemplo, supongamos que quiero acceder a la dirección 45h de memoria. Por el bus de direcciones saldría la dirección 44h como indicando que queremos acceder al bloque 1 Buses y Periféricos. Curso 2008/2009 Práctica 1. Diseño. de cuatro bytes que comienza en la dirección 44h y también vendría activada la dirección BH1, indicando que de esos cuatro bytes solo se desea el segundo. Bien, este es el lenguaje del bus. Pero el lenguaje de la memoria es distinto. El módulo de memoria responde ante direcciones de 4 bits, por lo tanto tenemos que hacer una traducción desde [A15:A2, BH3:BH0 ] a [ AM3:AM0]. Para ello lo primero es convertir la configuración BH3:BH0 en AM1,AM0: BH3:BH2:BH1:BH0 0:0:0:1 0:0:1:0 0:1:0:0 1:0:0:0 AM1:AM0 00 01 10 11 Las líneas AM3:AM2 son directamente A3:A2. Ahora bien, tenemos que tener en cuenta que puede haber más de una línea BH activa por lo cual debemos construir una unidad de control que nos permita realizar lecturas /escrituras consecutivas en la memoria a partir de los datos dispuestos. Ejemplo, en el bus de direcciones aparece la dirección 44h y en las líneas BH aparecen activas BH0 y BH1, estando la línea de W/R a 1. Esto significa que tendremos que hacer dos escrituras en la memoria, primero el byte que aparece en la Via 0 (V0) en la dirección 0000 (Los dos más significativos son A3:A2, y los dos menos significativos por estar BH0 activa) y depués el byte que aparece en V1 en la dirección 0001. El resto de las líneas de dirección del bus no pueden sernos indiferentes. El valor que tengan esas líneas indicará la dirección en memoria donde hemos ubicado nuestro módulo. (Ver la práctica del curso 2006/2007). No daremos por válida una dirección que venga por el bus si esas 12 líneas de dirección no tienen un valor predeterminado fijado por nosotros. Cuando aceptemos la dirección lo indicaremos con la señal Sel. Esta misma señal nos servirá para permitir o no cualquier acción en nuestro módulo. Será la señal de que nuestro módulo de memoria ha sido seleccionado. La transacción comienza cuando se activa la señal T, en este momento debe estar dispuesta la dirección a acceder en las líneas A15:A2, activadas las señales BH correspondientes e indicada la acción a realizar: lectura W/R=0, o escritura W/R=1. A partir de este momento, la unidad de control debe hacer lo siguiente: Lectura: 1. Se comparan las líneas A15:A4 con la dirección de ubicación de nuestro módulo. El resultado será la señal Sel. Si Sel queda inactiva no se realizará ninguna acción. 2. La unidad de control leerá tantos datos de la memoria como líneas activas haya en BH y los irá cargando en los registros de salida. 3. La unidad de control abrirá los buffers tri-estado y al mismo tiempo activará la señal Tr para indicar que los datos están dispuestos. Escritura 1. Se comparan las líneas A15:A4 con la dirección de ubicación de nuestro módulo. El resultado será la señal Sel. Si Sel queda inactiva no se realizará ninguna acción. 2. La unidad de control cargará los datos del bus en los registros de entrada. 2 Buses y Periféricos. Curso 2008/2009 Práctica 1. Diseño. 3. La unidad de control escribirá el contenido de los registros en la memoria según esté indicado por la línea BH correspondiente 4. La unidad de control activará la señal Tr para indicar que los datos han sido escritos. Este es un dispositivo síncrono. Es decir, necesita una señal de reloj que lo gobierne. Los datos se activarán al principio de una secuencia de periodos de reloj. El principio de esta secuencia lo marcará la señal T coincidiendo con un flanco de subida de la señal de reloj. El final lo marcará la señal Tr activa durante el último periodo de reloj necesario para completar la tarea. La señal Sel se activará en el periodo siguiente al que se active T si la dirección que hay en el bus se corresponde con la ubicación del módulo, si no permanecerá inactiva y no se realizará ninguna acción. El módulo de memoria que vamos a utilizar será un módulo primitivo proporcionado por el xilinx (ver descripción también en el guión de la práctica 2006/2007) Procedimiento El alumno debe diseñar este dispositivo siguiendo las directivas indicadas en este guión, pero aplicando sus propias habilidades, en particular en el diseño de la Unidad de Control. Se recomienda que invierta una parte de su tiempo en la planificación del mismo, comprendiendo qué es lo que se le solicita y meditando sobre diferentes soluciones antes de emprender el trabajo sobre la propia herramienta de diseño y 3 Buses y Periféricos. Curso 2008/2009 Práctica 1. Diseño. simulación. Este trabajo de planificación previa se considera muy importante en la memoria que el alumno ha de presentar como documentación del trabajo realizado. El diseño se hará, naturalmente sobre la herramienta xilinx, describiendo por medio de esquemáticos el diseño y demostrando su funcionalidad por medio de la simulación. Terminado el diseño y la simulacion exitosa, el alumno debe proporcionar un manual de descripción y uso del mismo (inserto en la propia memoria), en la que describirá detalladamente el funcionamiento de su dispositivo, el número de periodos de reloj que tarda en culminar su acción (tanto para lectura como para escritura) y la duración mínima del periodo de reloj en una unidad de tiemo genérica que llamaremos ut, teniendo en cuenta que todos los elementos procedente de las librerías de primitivas que ofrece el xilinx se considerarán con retardo de 1ut. Presentación. El alumno realizará el diseño y simulación del circuito planteado. Al finalizar la realización, se defenderá la práctica ante el profesor y se presentará una memoria del trabajo, en la cual se expondrá paso por paso el proceso de desarrollo, razonando y justificando cada decisión. Valoración Se valorará un estudio previo de la propuesta de diseño planteando y valorando las posibles soluciones. Se valorará en el diseño, supuesto su correcto funcionamiento según la descripción anterior, la originalidad de sus soluciones, la eficiencia de las mismas con respecto al uso de recursos y ahorro de retardos. Cualquier añadido que complete la propuesta sin perjudicar sus objetivos. Se valorará la modularidad y el orden en el diseño (que no de miedo mirarlo). En particular se espera encontrar una estructura canónica: Camino de datos – Unidad de Control Estando la unidad de control compuesta de tres elementos: Lógica de siguiente estado-Estado(Contador)-Lógica de salida Cada alumno deberá ser capaz de defender el trabajo realizado conociendo perfectamente cada detalle y justificación del mismo. 4