Tema 1.1 Tecnologías de diseño microelectrónico

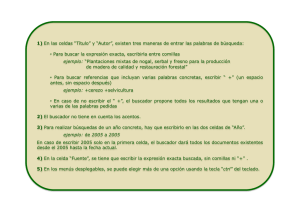

Anuncio

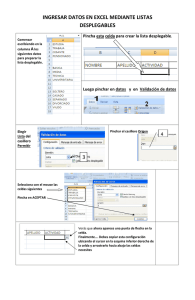

Diseño de Circuitos Integrados I (Plan 98 Ingeniero en Informática) Diseño de Circuitos Integrados (Plan 98 Ingeniero Técnico en Informática de Sistemas ) José Manuel Mendías Cuadros Hortensia Mecha López Dpto. Arquitectura de Computadores y Automática Universidad Complutense de Madrid 1 Datos profesor Despacho 003 Edif. Jardín Botánico tel: tel: +34 91 394 70 61, fax: +34 91 394 70 60 e-mail: [email protected] Página Web www.dacya.ucm.es/horten Tutorias: Tutorias: Miércoles y Jueves de 11:00 a 13:00 y de 15:00 a 16:00 2 Diseño de Circuitos Integrados Módulo I. Tecnología CMOS . Módulo II. Ingeniería de los Sistemas digitales 3 Módulo I Tecnología CMOS Tema 1. Tecnologías de diseño microelectrónico. Tema 2. Diseño digital CMOS. Tema 3. Diseño físico de circuitos CMOS. Tema 4. Diseño de elementos CMOS específicos. Tema 5. Cables. 4 Módulo II Ingeniería de Sistemas Digitales Tema 2.1 Introducción Tema 2.2 Alimentación Tema 2.3 Ruido Tema 2.4 Señalización. Tema 2.5 Temporización Tema 2.6 Sincronización Tema 2.7 Diseño Asíncrono 5 Bibliografía Bibliografía básica: W. J. Dally, J. W. Poulton, Poulton, "Digital Systems Engineering". Cambridge University Press. M. J. S. Smith “Aplication “Aplication--Specific Integrated Circuits” Ed. Addison Wesley Jan M. Rabaey, Rabaey, "Digital Integrated Circuits". Prentice Hall. W. Wolf , "Modern VLSI Design. A system approach". Prentice Hall. Hall. N. Weste, Weste, K. Eshraghian, Eshraghian, "Principles of CMOS VLSI Design: A Systems Perspective". Addison Wesley, Wesley, 1993. Bibliografía complementaria: Daniel D. Gajski, Gajski, "Principios de Diseño Digital". Prentice Hall, 1997 Giovanni De Micheli , "Synthesis and optimization of digital circuits". McGraw– McGraw–Hill Morant Martín, "Diseño y tecnología de circuitos integrados". AddisonAddisonWesley Iberoamericana C. Mead, L. Conway, "Introduction to VLSI Systems". Addison Wesley, Wesley, 1980. 6 Herramientas Diseño de circuitos – Microwin. Microwin. Simulación de circuitos – PSPICE. 7 Tema 1. Tecnologías de diseño microelectrónico Diseño de Circuitos Integrados I José Manuel Mendías Cuadros Hortensia Mecha López Dpto. Arquitectura de Computadores y Automática Universidad Complutense de Madrid 8 Módulo I Tecnología CMOS Tema 1. Tecnologías de diseño microelectrónico. Tema 2. Diseño digital CMOS. Tema 3. Diseño físico de circuitos CMOS. Tema 4. Diseño de elementos CMOS específicos. Tema 5. Cables. 9 Tema 1. Tecnologías de diseño microelectrónico – 1.1 Introducción – 1.2 Estilos de diseño microelectrónico Diseño full– full–custom. Diseño semi– semi–custom: gate– gate–arrays, standard cells, FPGAs, SOCs. – 1.3 Ciclo de producción de un circuito integrado Fabricación de un circuito integrado Niveles y dominios de descripción 10 Introducción La microelectrónica es la ciencia que estudia la integración de un gran número de dispositivos electrónicos sobre un único sustrato, y es es la base del desarrollo de los sistemas informáticos. Este proceso de integración se debe a la continua reducción de tamaño tamaño de los dispositivos, y ha dado lugar a diferentes familias tecnológicas: Años tecnología nº de disp/chip disp/chip circuitos 1947 invención del transistor ‘50 componentes discretos 1 transistor. inicio ’60 SSI (20 µm) 10 puertas, flipflip-flops. flops. med. med. ‘60 MSI 102~103 sumadores, contadores LSI (5 (5 µm) 103~104 microprocesadores 8 bits ‘80 VLSI VLSI / ULSI 2 µm 104~106 microprocesadores 16/32 bits ‘90 GLSI GLSI 0.5 µm 107 ~108 microprocesadores 64 bits ‘70 11 Introducción Mayor integración implica: – mayor nú número de dispositivos/chip. – menor nú número de componentes/sistema. – mayor velocidad de cá cálculo. – menor consumo. – mayor esfuerzo en diseñ diseño. – mayor esfuerzo en correcció corrección (menor posibilidad de reparació reparación). – mayor coste de manufactura que si se compensa con un mayor volumen de ventas, se traduce en un menor coste/unidad. 12 Introducción transistores por die (escala logarítmica) 64M 108 Memoria Microprocesador 107 64K 105 103 4M 1M 256K 106 104 16M 1K 4K 16K 80286 8080 Intel486™ Intel386™ Pentium® Pro Pentium® processor processor 8086 4004 ley de Moore (1964 - Fairchild), presidente de Intel: “el número de dispositivos/chip se duplica cada año” 102 101 1 ’70 ’75 ’80 ’85 ’90 ’95 ’00 13 Tema 1. Tecnologías de diseño microelectrónico – 1.1 Introducción – 1.2 Estilos de diseño microelectrónico Diseño full– full–custom. Diseño semi– semi–custom: gate– gate–arrays, standard cells, FPGAs, FPGAs, SOCs. SOCs. – 1.3 Ciclo de producción de un circuito integrado Fabricación de un circuito integrado Niveles y dominios de descripción 14 Estilos de diseño microelectrónico La viabilidad económica de un diseño microelectrónico depende de varios factores: – volumen de fabricación – número de circuitos correctos / número de circuitos fabricados (yield (yield)) – precio en mercado – rendimiento del circuito – tiempo de salida al mercado Para poder adaptar el diseño físico de un circuito a las diferentes necesidades del mercado, nacen los llamados estilos de diseño. Estos se clasifican en atención al grado de libertad que tiene el diseñador a la hora de decidir la topología física del circuito Estilos de diseño Full Custom Semi Custom basado en celdas celdas estándar macroceldas basado en arrays arrays predifundidos arrays precableados 15 Estilos de diseño microelectrónico Full custom El diseñador goza de completa libertad durante el diseño físico del circuito – – – – – – – no se utilizan elementos prediseñados ni prefabricados. no existen restricciones en el diseño de un bloque funcional. no existen restricciones en la ubicación de los bloques funcionales. funcionales. no existen restricciones en el trazado de las interconexiones. cualquier aspecto de un circuito puede optimizarse. se suele realizar jerárquicamente. fue muy popular en los primeros años, su uso disminuye día a día. día. Ventajas: Ventajas: – flexibilidad. – obtención de circuitos de alta calidad. 16 Estilos de diseño microelectrónico Full custom Desventajas: Desventajas: – no es automatizable. automatizable. – requiere un enorme esfuerzo y diseñadores con alta especialización. – tiempos largos de salida al mercado. – si no se siguen unas ciertas reglas, no hay seguridad de que el circuito funcione eléctricamente. – sólamente es rentable cuando los costes se amortizan con un gran volumen de producción (microprocesadores, memorias), con un tiempo de vida largo, o con un alto grado de reutilización (biblioteca de celdas). 17 Estilos de diseño microelectrónico layout de un flip-flop CMOS 4004 de Intel 18 Estilos de diseño microelectrónico Semi custom El diseñador realiza tiene ciertas restricciones durante diseño físico del circuito – sólo pueden usar una colección de bloques funcionales primitivos prediseñados o prefabricados. – existen restricciones en la ubicación de los bloques funcionales. funcionales. – existen restricciones en el trazado de las interconexiones. – sólo se pueden optimizar algunos aspectos del circuito. Ventajas: Ventajas: – es automatizable. automatizable. – el funcionamiento eléctrico del circuito está asegurado. – reduce el esfuerzo de diseño y requiere diseñadores menos especializados. – reduce el tiempo de salida al mercado. 19 Estilos de diseño microelectrónico Semi custom Desventajas: Desventajas: – se obtienen circuitos de rendimiento medio Semi Custom basado en celdas celdas estándar macroceldas basado en arrays arrays predifundidos arrays precableados 20 Estilos de diseño microelectrónico Celdas estándar (standard cells) ⌦Metodología de diseño: Todo diseño debe realizarse mediante la interconexión de un conjunto de bloques funcionales prediseñados denominados celdas. Las celdas (de entre 200 y 400 tipos diferentes) se agrupan en bibliotecas facilitadas por el fabricante y se actualizan cuando cambia la tecnología. Funcionalmente las celdas son simples (puerta lógicas, flip-flops). Geométricamente una celda es un rectángulo de altura fija y anchura variable que depende de la complejidad de funcionalidad implementada. Sus entradas y salidas están ubicadas en los extremos superior e inferior del rectángulo, y sus tomas de alimentación y tierra están ubicadas de manera que las líneas de distribución de alimentación y tierra se puedan trazar horizontalmente sobre ellas. 21 Estilos de diseño microelectrónico Las celdas deben ubicarse en filas de igual altura, dejando entre las filas un espacio libre de anchura variable denominado canal. Las interconexiones entre celdas de la misma fila o entre celdas de filas adyacentes (conexiones cercanas) se trazan en el canal. Las restantes interconexiones (interconexiones lejanas) se realizan a través de celdas de paso o en otros niveles de metalización. PWR GND CELDA 1 CELDA 2 CELDA 3 CELDA CELDA 4 5 CELDAS CANAL PWR GND CELDA 6 CELDA CELDA 7 8 CELDA 9 CELDAS CANAL CELDAS PWR GND CELDA 10 CELDA 11 CELDA 12 CELDA 13 CELDA 14 22 Estilos de diseño microelectrónico Celdas estándar (standard cells) ⌦Características: Requiere el diseño full custom de las celdas y su caracterización. Enlaza fácilmente con la fase previa de diseño lógico mediante un proceso conocido como proyección tecnológica. 23 Estilos de diseño microelectrónico Macro celdas (macro cells) Existen circuitos, llamados macroceldas, macroceldas, cuyas implementaciones físicas tienen una estructura regular, fácilmente escalable y con un rendimiento rendimiento óptimo: – Multiplicadores, sumadores, desplazadores, desplazadores, RAM, ROM, PLA ... Su diseño puede ser fácilmente automatizado mediante los generadores de macroceldas, macroceldas, que a partir de los parámetros característicos del módulo, generan generan su diseño físico. SRAM Data paths Video-encoder En un circuito es típico encontrar una mezcla de fullfull-custom, custom, celdas estándar y macroceldas SRAM Routing Channel Los datadata-paths suelen ser caminos muy regulares pues mantienen la misma estructura para los n bits. Por eso también suelen utilizarse generadores para su diseño Standard cells 24 Estilos de diseño microelectrónico Arrays Predifundidos Metodología de diseño: diseño: – Todo diseño debe realizarse mediante la interconexión de una colección colección de celdas idénticas. – Funcionalmente las celdas extremadamente simples (transistor, NAND NAND o NOR). – Las celdas ya están prefabricadas y dispuestas regularmente sobre sobre el silicio. – Durante la fase de metalización se decide el interconexionado e incluso la función de las celdas. Características: – Solamente la última fase de fabricación (metalización) es dependiente dependiente del diseño particular, por lo que las primeras fases son comunes y tienen un gran volumen de producción. – Siempre queda un porcentaje de celdas sin usar. 25 Estilos de diseño microelectrónico Arrays Predifundidos Gate array – Cada celda está formada por un pequeño número de transistores cuyo cuyo interconexionado local determina su función (este interconexionado local puede o no estar prefabricado). – Las celdas se disponen en filas dejando entre un espacio libre vertical vertical y/o horizontal de tamaño fijo llamado canal. – Las interconexiones entre celdas se trazan por el canal. Sea of gates – Cada celda es un único transistor. – Las celdas se disponen en filas sin dejar espacio libre entre ellas. ellas. – Las interconexiones se trazan sobre celdas sin utilidad, o usando usando las propias celdas como elemento de interconexión. 26 Estilos de diseño microelectrónico Gate Arrays Esquema de una celda básica Esquema del layout de un Gate array 27 Estilos de diseño microelectrónico 28 Estilos de diseño microelectrónico Arrays de celdas. Metalización a b c G G G n n n p n n p n p 29 Estilos de diseño microelectrónico Arrays de celdas. Metalización. Transistores en serie 0v a b c G G G n n p n n p n 5v n p 30 Estilos de diseño microelectrónico Arrays de celdas. Metalización. Transistores en paralelo 0v a G n n n p n p 5v c G b G n n p 31 Estilos de diseño microelectrónico polysilicon In 1 In 2 In 3 In4 4-input NOR Posibles configuraciones después de la metalización V DD y = x0 + x1 metal GND x0 y = x0 ⋅ x1 x1 posible contacto Out puerta NOR de 2 entradas 32 Estilos de diseño microelectrónico Posibles configuraciones después de la metalización y = x0 + x1 x0 Y x1 x0 y = x0 ⋅ x1 x1 puerta NOR de 2 entradas 33 Estilos de diseño microelectrónico PUERTA NAND x2 x0 x1 Y y = x0 ∗ x1 * x 2 x0 x1 x2 y = x0 + x1 + x2 34 Estilos de diseño microelectrónico Sea of Gates Random Logic Memory Subsystem esquema del layout de un Sea of Gates LSI Logic LEA300K (0.6 mm CMOS) 35 Estilos de diseño microelectrónico Arrays Precableados Circuitos prefabricados con funcionalidad programable: PLA, PROM, PAL, CPLD, FPGA PLA (Array (Array Lógico Programable) – Un array de celdas AND programable (colección de mintérminos programable) – Un array de puertas OR programable (se pueden reusar términos) PAL (Lógica de Array Programable) – Un array de celdas AND programable (colección de mintérminos programable) – Un array de puertas OR no programable PROM (Memoria Programable de sólo Lectura) – Un array de celdas AND no programable (están todos los mintérminos) mintérminos) – Un array de puertas OR programable 36 Estilos de diseño microelectrónico PLA PROM CPLD PAL 37 Estilos de diseño microelectrónico CPLD (Dispositivo de Lógica Programable Complejo) – Se basa en la idea de las PLA pero a gran escala y con lógica adicional adicional FPGA (Array (Array de puertas programable en laboratorio) – Un array de celdas regularmente dispuestas sobre el silicio cuya funcionalidad es programable, denominados CLBs. CLBs. – Una colección de celdas de entrada/salida dispuestas perimetralmente perimetralmente cuyas características son programables, denominados IOBs – Una colección de bloques de interconexión (PSM ), que bajo (PSM), programación permiten conectar CLBs e IOBs entre sí. – Características: Características: El diseño físico y la fabricación es independiente del diseño particular. particular. Diseños complejos pueden no caber en una FPGA. 38 Estilos de diseño microelectrónico FPGAs Xilinx XC4025 39 Estilos de diseño microelectrónico 40 Estilos de diseño microelectrónico CLB CLB matriz de conmutación PSM Canal de rutado horizontal punto de interconexión CLB CLB Canal de rutado vertical 41 Estilos de diseño microelectrónico Estructura de un CLB Estructura de una LUT 42 Estilos de diseño microelectrónico Metodología de diseño para FPGA: – Los diseños no se fabrican, sino que se realizan programando adecuadamente adecuadamente los CLBs, CLBs, IOBs y bloques de interconexión. – Cada bloque almacena su configuración (programa) en una SRAM, EPROM EPROM o en antifusibles. antifusibles. Dependiendo del método de almacenaje el diseño volcado sobre la FPGA será o no volátil. – Funcionalmente las celdas son complejas y su grado de complejidad complejidad se denomina granularidad: granularidad: Granularidad fina (FPGAs): FPGAs): cualquier función de conmutación de 4~6 variables y varios FFs. FFs. Granularidad gruesa (FIPSOCs, FIPSOCs, sistemas reconfigurables): reconfigurables): ALUs y varios registros. 43 Estilos de diseño microelectrónico Full-custom Basado en celdas Tamaño de celda Variable Altura Fija Fijo Fijo Tipo de celda Variable Variable Fijo Programable Emplazamiento Variable En Filas Fijo Fijo Interconexionado Variable Variable Variable Programable Muy Alta Fiabilidad eléctrica Arrays Predifundidos Arrays Precableados Media Alta Alta Densidad funcional Muy Alta Alta Alta Medio Rendimiento funcional Muy Alto Alto Alto Medio Flexibilidad en diseño físico Muy Alta Alta Media Ninguna Tiempo de diseño físico Muy Alto Medio Medio Ninguno Tiempo de fabricación Medio Medio Bajo Muy Bajo Coste baja producción Muy Alto Alto Alto Bajo Coste alta producción Bajo Bajo Bajo Muy Alto 44 Estilos de diseño microelectrónico Dentro del diseño VLSI existen múltiples procesos tecnológicos nacidos para hacer frente, junto a los estilos de diseño, a las diferentes necesidades de un producto: – velocidad, – consumo, – complejidad de diseño ⌦ En la actualidad las más comunes son: nMOS: velocidad media, consumo alto CMOS: velocidad media, consumo bajo BiCMOS: velocidad alta, consumo alto ECL: velocidad alta, consumo muy alto GaAs: velocidad muy alta, consumo alto, dificultad de integración 45 Tema 1. Tecnologías de diseño microelectrónico – 1.1 Introducción – 1.2 Estilos de diseño microelectrónico Diseño full– full–custom. Diseño semi– semi–custom:, standard cells, gate– gate–arrays, FPGAs, FPGAs, – 1.3 Ciclo de producción de un circuito integrado Fabricación de un circuito integrado Niveles y dominios de descripción 46 Ciclo de producción de un circuito integrado Conceptualización Fabricación prototipo Especificación Validación Refinamiento Testeo Diseño Validación Encapsulado Optimización Evaluación Fabricación masiva Encapsulado Testeo 47 Ciclo de producción de un circuito integrado Conceptualización: Conceptualización: a partir de un concepto, concreción de los requisitos funcionales y no funcionales del circuito que va a implementarlo. implementarlo. Especificación o modelado: modelado: formalización de los anteriores requisitos en una representación uniforme y procesable por máquina. Validación de modelos: modelos: comprobación de que se ha especificado correctamente el concepto. Refinamiento del modelo: modelo: mejora de la calidad de una especificación. Diseño o síntesis: síntesis: transformación de la especificación en una implementación. Optimización: Optimización: mejora de la calidad de una implementación. Validación de implementación: implementación: comprobación de que se ha sintetizado correctamente la especificación (de aspectos funcionales y no funcionales). 48 Ciclo de producción de un circuito integrado Fabricación: – preparación de la oblea (10 cm de diámetro). – deposición, implantación y difusión de materiales en la oblea según las máscaras resultado del proceso de síntesis física. Encapsulado: – – – – – cortado de la oblea en dados (dies). descartado de dados defectuosos por imperfecciones del substrato. encapsulado del dado en un soporte plástico o cerámico. soldado de los pads del dado con la patillas del chip. sellado del chip. Validación de la producción o testeo: comprobación que se ha fabricado correctamente la implementación (de aspectos funcionales y no funcionales). 49 Ciclo de producción de un circuito integrado Fabricación de un circuito integrado 50 Ciclo de producción de un circuito integrado Sección de un transistor 51 Ciclo de producción de un circuito integrado Sección de una interconexión 52 Ciclo de producción de un circuito integrado Vista al microscropio electrónico de una porción de circuito integrado Oblea fabricada 53 Tema 1. Tecnologías de diseño microelectrónico – 1.1 Introducción – 1.2 Estilos de diseño microelectrónico Diseño full– full–custom. Diseño semi– semi–custom: gate– gate–arrays, standard cells, FPGAs, FPGAs, SOCs. SOCs. – 1.3 Ciclo de producción de un circuito integrado Fabricación de un circuito integrado Niveles y dominios de descripción 54 Ciclo de producción de un circuito integrado Niveles y dominios de descripción dominio conductual dominio estructural ISAs, algoritmos transferencias entre registros expresiones de conmutación, FSMs funciones de transferencia, formas de onda Dominio conductual: conductual: un sistema es descrito por la función que realiza. Domino estructural: estructural: un sistema es descrito por la interconexión de los módulos que lo forman (netlist o esquemático). Domino físico: físico: un sistema es descrito por la ubicación espacial y propiedades de los elementos reales que lo constituyen. nivel circuital nivel lógico nivel RT nivel algorítmico nivel sistema CPUs, subsistemas ALU, MUX, registros puertas, flip-flops transistores póligonos, líneas máscaras celdas floorplan dominio físico 55 Ciclo de producción de un circuito integrado El nivel de detalle con que se realice cualquiera de las anteriores anteriores descripciones, se denomina nivel de abstracción: abstracción: – Nivel de circuito o de transistor: transistor: el tiempo es continuo, las variables son magnitudes físicas continuas, no existen por separado las nociones nociones alimentación y computación. – Nivel lógico o de puertas: puertas: el tiempo es continuo, las variables toman valores booleanos (0 ó 1), la alimentación se abstrae permaneciendo la noción de computación. – Nivel RT: que RT: el tiempo es discreto, las variables se agrupan en palabras que toman valores discretos. En la noción de computación se distinguen distinguen las nociones de control y procesamiento de datos. – Nivel algorítmico: algorítmico: el tiempo desaparece apareciendo la noción de dependencia, las variables se agrupan en estructuras abstractas, el control está estructurado. – Nivel sistema: sistema: desparecen los detalles de los cálculos concretos e interesan las relaciones abstractas entre entre subsistemas, aparecen nociones de sincronización y protocolo. 56 Ciclo de producción de un circuito integrado Asímismo cada nivel de abstracción tiene sus propias medidas de calidad: – Nivel de circuito o de transistor: transistor: tiempos de subida/bajada, pendientes de transición, área real. – Nivel lógico: lógico: tiempos de conmutación, incertidumbre, skew, skew, área equivalente. – Nivel RT: RT: tiempo de ciclo, margen, puertas equivalentes. – Nivel algorítmico: algorítmico: latencia, cadencia de datos, número de módulos. – Nivel sistema: sistema: ancho de banda, MFLOPS. 57 Ciclo de producción de un circuito integrado dominio conductual dominio estructural Síntesis Análisis Re fin am ien Ab to st r ac ci ó n Optimización Extracción Generación dominio físico 58 Ciclo de producción de un circuito integrado Las transiciones entre cada uno de los dominios y niveles de abstracción abstracción tienen los siguientes nombres: – Síntesis: Síntesis: todo proceso que genere una netlist a partir una descripción de su conducta (transición del dominio conductual al estructural). – Análisis: Análisis: todo proceso que permita obtener la conducta de una netlist (transición del dominio estructural al conductual). – Optimización: Optimización: todo proceso que modifique una descripción, sin cambiar de dominio ni de nivel de abstracción de manera que presente un rendimiento rendimiento distinto. – Generación: Generación: todo proceso que genere una estructura física a partir de una netlist (transición del dominio estructural al físico). – Extracción: Extracción: todo proceso que permita obtener la netlist de una estructura física (transición del dominio físico al estructural). – Refinamiento: Refinamiento: todo proceso que disminuya el nivel de abstracción de una descripción sin cambiar de dominio. – Abstracción: Abstracción: todo proceso que aumente el nivel de abstracción de una descripción sin cambiar de dominio. 59