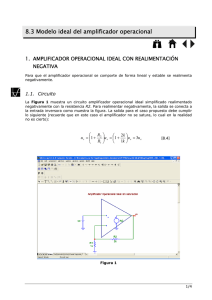

4de7.RMGcap.4

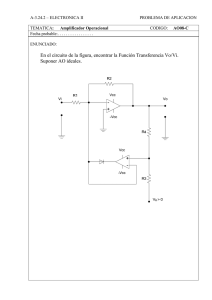

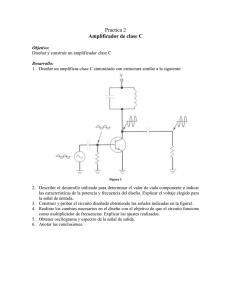

Anuncio