Tema 2 Algebra logica

Anuncio

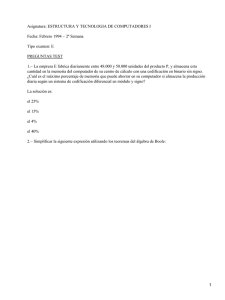

Escuelas Técnicas de Ingenieros Universidad de Vigo Departamento de Tecnología Electrónica Electrónica Digital: Álgebra de Boole ELECTRÓNICA DIGITAL TEMA 2 ÁLGEBRA LOGICA Enrique Mandado Pérez Escuelas Técnicas de Ingenieros Universidad de Vigo Departamento de Tecnología Electrónica Electrónica Digital: Álgebra de Boole OPERACIONES BÁSICAS DEL ÁLGEBRA LÓGICA b a O b a Y 0 0 0 0 0 0 0 1 1 0 1 0 1 0 1 1 0 0 1 1 1 1 1 1 a) Operación O O p e b) Operación Y a /a 0 1 1 0 Inversión 2 Escuelas Técnicas de Ingenieros Universidad de Vigo Departamento de Tecnología Electrónica Electrónica Digital: Álgebra de Boole ÁLGEBRA LÓGICA (DE BOOLE) OPERACIONES Suma lógica: Paralelo de contactos Producto lógico: Serie de contactos 3 1 6 Inversión : Contacto inverso 4 5 2 Relé 3 Escuelas Técnicas de Ingenieros Universidad de Vigo Departamento de Tecnología Electrónica Electrónica Digital: Álgebra de Boole ÁLGEBRA LÓGICA SP: DP: ST: DT: NO: NC: Single Pole Double Pole Single Through Double Through Normally Open Normally Close SPST - NO SPST - NC SPDT DPST - NO DPST - NC DPDT 4 Escuelas Técnicas de Ingenieros Universidad de Vigo Departamento de Tecnología Electrónica Electrónica Digital: Álgebra de Boole ÁLGEBRA LÓGICA POSTULADOS a b b a = a+b a b a·b b+a b = a b·a 0 a a 0+a 1 = a 1·a a a = a 5 Escuelas Técnicas de Ingenieros Universidad de Vigo Departamento de Tecnología Electrónica Electrónica Digital: Álgebra de Boole ÁLGEBRA LÓGICA TEOREMAS b a b c a c a a · (b + c) a b c = a+b·c a·b+a·c = a a b c (a + b) · (a + c) a 1 a a+a a = a a·a 1 0 = 0 6 Escuelas Técnicas de Ingenieros Universidad de Vigo Departamento de Tecnología Electrónica Electrónica Digital: Álgebra de Boole ÁLGEBRA LÓGICA TEOREMAS a 1 1 = a+1 a 0 a·0 1 0 = 0 7 Escuelas Técnicas de Ingenieros Universidad de Vigo Departamento de Tecnología Electrónica Electrónica Digital: Álgebra de Boole ÁLGEBRA LÓGICA TEOREMAS a a a = a+a a a a·a a a = a 8 Escuelas Técnicas de Ingenieros Universidad de Vigo Departamento de Tecnología Electrónica Electrónica Digital: Álgebra de Boole ÁLGEBRA LÓGICA TEOREMAS a a a b = a+a·b a a a a b a · (a + b) = a 9 Escuelas Técnicas de Ingenieros Universidad de Vigo Departamento de Tecnología Electrónica Electrónica Digital: Álgebra de Boole ÁLGEBRA LÓGICA TEOREMAS Teoremas de DeMorgan a + b + c + dK = a b c d K abc dK = a + b + c + d K 10 Escuelas Técnicas de Ingenieros Universidad de Vigo Departamento de Tecnología Electrónica Electrónica Digital: Álgebra de Boole PUERTAS LÓGICAS (LOGIC GATES) Implementan funciones básicas Función Y (AND) Función O (OR) Inversión Función NO-Y (NAND) Función NO-O (NOR) Función O-exclusiva (Exclusive OR) 11 Escuelas Técnicas de Ingenieros Universidad de Vigo Departamento de Tecnología Electrónica Electrónica Digital: Álgebra de Boole PUERTAS LÓGICAS Y y O Símbolos lógicos Símbolos IEEE a f = ab b a f=a+b b Función Y SENSORES DE MEDIDA DE SÍMBOLOS IEC Función O Símbolos normalizados IEC a a & f = ab b Función Y ≥1 f=a+b b Función O 12 Escuelas Técnicas de Ingenieros Universidad de Vigo Departamento de Tecnología Electrónica Electrónica Digital: Álgebra de Boole PUERTAS LÓGICAS (LOGIC GATES) LÓGICA POSITIVA El 1 se asigna a la tensión más positiva y el 0 a la más negativa LÓGICA NEGATIVA El O se asigna a la tensión más positiva y el 1 a la más negativa 13 Escuelas Técnicas de Ingenieros Universidad de Vigo Departamento de Tecnología Electrónica Electrónica Digital: Álgebra de Boole PUERTAS LÓGICAS Y y O a +VCC b 0 c Puerta O en lógica positiva eY en lógica negativa S = a+b+c (Lógica positiva) R 0V a +VCC b 0 Puerta Y en lógica positiva y O en lógica negativa c S = a·b·c (Lógica positiva) R +Vcc 14 Escuelas Técnicas de Ingenieros Universidad de Vigo Departamento de Tecnología Electrónica Electrónica Digital: Álgebra de Boole PUERTAS LÓGICAS Y y O Circuito lógico realizado con puertas lógicas Y y O +VCC +VCC PUERTA Y1 R1 PUERTA Y2 R1 a +VCC PUERTA O b 0 c S1 S2 R2 0V 15 Escuelas Técnicas de Ingenieros Universidad de Vigo Departamento de Tecnología Electrónica Electrónica Digital: Álgebra de Boole PUERTA INVERSORA Inversión con un relé 1 a a Función inversión 3 1 6 4 5 2 Relé 16 Escuelas Técnicas de Ingenieros Universidad de Vigo Departamento de Tecnología Electrónica Electrónica Digital: Álgebra de Boole PUERTA INVERSORA Transistor NPN en conmutación +VCC IC R2 R1 R3 S E C I Bn = cte B R1 +VCC 0 I B2 R2 I B1 A 0V I B0 = 0 VCE 17 Escuelas Técnicas de Ingenieros Universidad de Vigo Departamento de Tecnología Electrónica Electrónica Digital: Álgebra de Boole PUERTA INVERSORA +VCC +VCC R3 S E t to R1 IC +VCC I CS 90% 0 R2 10% 0V t ts tr t1 tb ta t2 18 Escuelas Técnicas de Ingenieros Universidad de Vigo Departamento de Tecnología Electrónica Electrónica Digital: Álgebra de Boole PUERTAS LÓGICAS NAND y NOR Símbolos lógicos no normalizados (IEEE) a a f=ab=a+b b f=a+b=ab b a f=a+b=ab b Función NO-Y (NAND) f=ab=a+b b Función NO-O (NOR) 19 Escuelas Técnicas de Ingenieros Universidad de Vigo Departamento de Tecnología Electrónica Electrónica Digital: Álgebra de Boole PUERTAS LÓGICAS NAND y NOR Símbolos lógicos normalizados (IEC) Símbolos lógicos normalizados a & a f=ab=a+b b a ≥1 f=a+b=ab b Función NO-Y (NAND) ≥1 f=a+b=ab b a & f=ab=a+b b Función NO-O (NOR) 20 Escuelas Técnicas de Ingenieros Universidad de Vigo Departamento de Tecnología Electrónica Electrónica Digital: Álgebra de Boole PUERTAS LÓGICAS NAND y NOR Puerta Lógica NO-O con diodos y relé en lógica positiva a +VCC b 0 c 0V 21 Escuelas Técnicas de Ingenieros Universidad de Vigo Departamento de Tecnología Electrónica Electrónica Digital: Álgebra de Boole ÁLGEBRA DE BOOLE Relés estáticos (Static relays) -VCC +VCC R R a RC a R R b 0 -VCC RC b S=a+b+c R +VCC c 0 S=a+b+c R c RE RE 0V 0V +VBB Germanio Silicio 22 Escuelas Técnicas de Ingenieros Universidad de Vigo Departamento de Tecnología Electrónica Electrónica Digital: Álgebra de Boole ÁLGEBRA DE BOOLE Relé estático Circuito bloque de la familia NORBIT (Cortesía de Philips). 23 Escuelas Técnicas de Ingenieros Universidad de Vigo Departamento de Tecnología Electrónica Electrónica Digital: Álgebra de Boole Mapa conceptual de los circuitos integrados Circuitos Integrados Digitales Monolíticos (CIDM) Según la realización física Según el semiconductor utilizado CIDM Silicio Según la forma en que se realiza el diseño de los sistemas electrónicos digitales Según el número de dispositivos CIDM Arseniuro de Galio SSI Según el tipo de dispositivo CIDM Bipolar CIDM MOS Especificados por el usuario Según la función del circuito Según la metodología Totalmente a Medida MSI CIDM BICMOS Fija PMOS ULSI DTL NMOS TTL CMOS Según el campo de aplicación GLSI General Específica HTL Según la función ECL Semimedida LSI VLSI RTL Normalizados Función Única Programable Celdas Normalizadas Según la arquitectura Matrices de Puertas Arquitectura Fija Según el tipo de sistemas Arquitectura Configurable Según la distribución de recursos Concentrados (PLDs) 2 IL Multifuncional Combinacionales Distribuidos (FPGAs) Según la capacidad de expansión Secuenciales Expansibles No Expansibles 24 Escuelas Técnicas de Ingenieros Universidad de Vigo Departamento de Tecnología Electrónica Electrónica Digital: Álgebra de Boole ÁLGEBRA DE BOOLE Primer circuito integrado digital monolítico (1965) Tecnología RTL (Resistor Transistor logic) Identificador del pin 1 +VCC RC S=a+b+c R R a R b c Encapsulado (Package) 25 Escuelas Técnicas de Ingenieros Universidad de Vigo Departamento de Tecnología Electrónica Electrónica Digital: Álgebra de Boole ÁLGEBRA DE BOOLE Tecnología DTL (Diode Transistor logic) (1967) +VCC R1 R3 D1 a +VCC D2 b 0 D4 D5 S = a·b·c T D3 c R2 Nudo 26 Escuelas Técnicas de Ingenieros Universidad de Vigo Departamento de Tecnología Electrónica Electrónica Digital: Álgebra de Boole ÁLGEBRA DE BOOLE Tecnología TTL (Transistor Transistor logic) (1970) +VCC +VCC R1 4k R2 1k6 R4 130 R1 T3 R3 D1 a +VCC +VCC a b c D1 T2 D2 b 0 T1 D4 D5 S = a·b·c T D3 c R2 0 T4 S = abc Nudo R3 1k 27 Escuelas Técnicas de Ingenieros Universidad de Vigo Departamento de Tecnología Electrónica Electrónica Digital: Álgebra de Boole IMPLEMENTACIÓN DE LAS FUNCIONES Y y O CON NAND y NOR Símbolos Símbolos lógicos no normalizados lógicos IEEE a a ab ab b b a a+b b a a+b b 28 Escuelas Técnicas de Ingenieros Universidad de Vigo Departamento de Tecnología Electrónica Electrónica Digital: Álgebra de Boole IMPLEMENTACIÓN DE LAS FUNCIONES Y y O CON NAND y NOR Símbolos lógicos normalizados (IEC) 1 a & a ≥1 1 ab ab b 1 b 1 1 a a & & a+b a+b 1 b 1 b 29 Escuelas Técnicas de Ingenieros Universidad de Vigo Departamento de Tecnología Electrónica Electrónica Digital: Álgebra de Boole FUNCIÓN O-EXCLUSIVA Función O-exclusiva Símbolo lógico IEEE a fo = a ⊕ b b Símbolo lógico normalizado a b =1 b a fe 0 0 1 0 1 0 1 0 0 1 1 1 fo = a ⊕ b Tabla de verdad 30 Escuelas Técnicas de Ingenieros Universidad de Vigo Departamento de Tecnología Electrónica Electrónica Digital: Álgebra de Boole FUNCIONES LÓGICAS Expresiones canónicas de Suma de productos (Sum of products) y producto de sumas (Product of sums) 2n −1 2n −1 n f (a, b, c,K) = ∑ f (i )i = ∏ [ f (2 − 1 − i ) + i ] i =0 i =0 31 f = abc + abc + a bc + a bc + abc Escuelas Técnicas de Ingenieros Universidad de Vigo Departamento de Tecnología Electrónica Electrónica Digital: Álgebra de Boole TABLA DE VERDAD DE UNA FUNCIÓN LÓGICA Ejemplo de función lógica cba f 0000 0 f = abc + abc + a bc + a bc + abc f = abc + abc + a bc + a bc + abc 1001 1 2010 0 3011 1 4100 1 f = abc + abc + a bc + a bc + abc 5101 0 f = ∑ (1,3,4,6,7) 3 6110 1 7111 1 32 Escuelas Técnicas de Ingenieros Universidad de Vigo Departamento de Tecnología Electrónica Electrónica Digital: Álgebra de Boole EXPRESIONES CANÓNICAS DE UNA FUNCIÓN LÓGICA Ejemplo f = ∑ (0,3,7) 3 Pi = S2n −1−i f = ∑ (1,2,4,5,6) 3 a b c = P2 = a + b + c = S 5 f = ∏ (1,2,3,5,6) 3 33 Escuelas Técnicas de Ingenieros Universidad de Vigo Departamento de Tecnología Electrónica Electrónica Digital: Álgebra de Boole PUERTAS LÓGICAS Tipos de puertas de acuerdo con el circuito de salida: Salida normal. Salida triestado. Salida de colector o drenador abierto. Salida de emisor o surtidor abierto. Salida con carga pasiva en el colector o drenador. Salida con carga pasiva en el emisor o surtidor . 34 Escuelas Técnicas de Ingenieros Universidad de Vigo Departamento de Tecnología Electrónica Electrónica Digital: Álgebra de Boole CIRCUITO DE SALIDA DE LAS PUERTAS LÓGICAS +VC Tipo de bloque funcional BLOQUE FUNCIONAL COMBINACIONAL DEA CIRCUITO Variables de entrada Variable de salida normal DIGITAL Variables de entrada Variable de salida normal COMBINACIONAL DEA SALIDA NORMAL La poseen la mayoría de los bloques funcionales para acoplarse entre sí y con las diversas puertas lógicas. Suele recibir el nombre de salida con carga activa (Active pull-up or push-pull output). Está formada por dos dispositivos electrónicos activos conectados en serie entre los dos polos de la fuente de alimentación. 35 Escuelas Técnicas de Ingenieros Universidad de Vigo Departamento de Tecnología Electrónica Electrónica Digital: Álgebra de Boole CIRCUITO DE SALIDA DE LAS PUERTAS LÓGICAS Tecnología TTL (Transistor Transistor lógic) (1970) +VCC R1 4k R2 1k6 R4 130 T3 +VCC a b c D1 T2 T1 0 T4 S = abc R3 1k 36 Escuelas Técnicas de Ingenieros Universidad de Vigo Departamento de Tecnología Electrónica Electrónica Digital: Álgebra de Boole CIRCUITO DE SALIDA DE LAS PUERTAS LÓGICAS Tipo de bloque funcional +VC BLOQUE FUNCIONAL COMBINACIONAL DEA CIRCUITO Variables de entrada Variable de salida de tres estados DIGITAL COMBINACIONAL Variables de entrada ∇ DEA Variable de desinhibición (Enable) Variable de desinhibición (Enable) Variable de salida de tres estados EN SALIDA DE TRES ESTADOS La etapa de salida de tres estados (Three state output) se caracteriza porque el bloque funcional posee una entrada de control (Enable) que, cuando está en un determinado nivel, hace que no conduzcan los dos dispositivos electrónicos activos. Este tipo de salida se identifica mediante un triángulo isósceles. 37 Escuelas Técnicas de Ingenieros Universidad de Vigo Departamento de Tecnología Electrónica Electrónica Digital: Álgebra de Boole CIRCUITO DE SALIDA DE LAS PUERTAS LÓGICAS +VCC R1 R2 R3 T3 T4 +VCC a b D1 T2 T1 R4 0 S = ab Puerta TTL de tres estados T5 +VCC R6 R5 R7 Entrada G (EN) de T6 Inhibición T7 T8 R8 38 Escuelas Técnicas de Ingenieros Universidad de Vigo Departamento de Tecnología Electrónica Electrónica Digital: Álgebra de Boole CIRCUITO DE SALIDA DE LAS PUERTAS LÓGICAS Tipo de bloque funcional BLOQUE FUNCIONAL COMBINACIONAL Variable de salida de colector o drenador abierto CIRCUITO Variables de entrada DIGITAL COMBINACIONAL DEA Variables de entrada Variable de salida de colector o drenador abierto SALIDA DE COLECTOR O DRENADOR ABIERTO La etapa de salida de colector o drenador abierto (Open collector or open drain) posee un único dispositivo electrónico activo que tiene un terminal unido al polo negativo de la alimentación y el otro al aire. Se identifica mediante un rombo que posee un segmento horizontal en el vértice inferior. 39 Escuelas Técnicas de Ingenieros Universidad de Vigo Departamento de Tecnología Electrónica Electrónica Digital: Álgebra de Boole CIRCUITO DE SALIDA DE LAS PUERTAS LÓGICAS SALIDA DE COLECTOR O DRENADOR ABIERTO +VCC R1 +VCC a b R2 T2 T1 0 T3 S R2 Puerta lógica TTL de colector abierto 40 Escuelas Técnicas de Ingenieros Universidad de Vigo Departamento de Tecnología Electrónica Electrónica Digital: Álgebra de Boole CIRCUITO DE SALIDA DE LAS PUERTAS LÓGICAS Ejemplo: Decodificador +VCC 0V DECODIFICADOR BIN/DEC EXCITADOR BIN/DEC BIN/DEC 0 Q0 0 1 1 Q0 Q1 1 2 Q1 1 3 2 2 4 3 Número en BCD natural 4 2 4 5 4 5 6 4 6 7 7 8 8 8 9 Q9 Q9 8 9 41 Escuelas Técnicas de Ingenieros Universidad de Vigo Departamento de Tecnología Electrónica Electrónica Digital: Álgebra de Boole CIRCUITO DE SALIDA DE LAS PUERTAS LÓGICAS +VC Tipo de bloque funcional BLOQUE FUNCIONAL COMBINACIONAL R CIRCUITO Variables de entrada DIGITAL COMBINACIONAL DEA Variable de salida con carga pasiva en el colector o en el drenador Variables de entrada Variable de salida con carga pasiva en el colector o en el drenador SALIDA CON CARGA PASIVA EN EL COLECTOR O DRENADOR La etapa de salida con carga pasiva en el colector o en el drenador posee único dispositivo electrónico activo que tiene un terminal unido al polo negativo de la alimentación y el otro a una resistencia (Pull-up resistor) conectada al polo positivo de la alimentación Este tipo de salida se identifica mediante un rombo que posee un segmento horizontal en el vértice inferior y otro en la diagonal horizontal. 42 Escuelas Técnicas de Ingenieros Universidad de Vigo Departamento de Tecnología Electrónica Electrónica Digital: Álgebra de Boole CIRCUITO DE SALIDA DE LAS PUERTAS LÓGICAS EJEMPLO DE SALIDA CON CARGA PASIVA EN EL COLECTOR O DRENADOR Tecnología DTL (Diode Transistor lógic) (1967) +VCC R1 R3 D1 a +VCC D2 b 0 D4 D5 S = a·b·c T D3 c R2 Nudo 43 Escuelas Técnicas de Ingenieros Universidad de Vigo Departamento de Tecnología Electrónica Electrónica Digital: Álgebra de Boole CIRCUITO DE SALIDA DE LAS PUERTAS LÓGICAS +VCC 0V DECODIFICADOR BCD/DEC EXCITADOR R BIN/DEC 0 1 BIN/DEC 1 0 1 1 2 R 2 3 2 4 3 4 2 5 4 4 5 6 4 6 7 8 7 8 8 R 8 9 Q0 Q1 Q2 Q3 Q4 Q5 Q6 Q7 Q8 Q9 9 44 Escuelas Técnicas de Ingenieros Universidad de Vigo Departamento de Tecnología Electrónica Electrónica Digital: Álgebra de Boole CIRCUITO DE SALIDA DE LAS PUERTAS LÓGICAS +VC Tipo de bloque funcional BLOQUE FUNCIONAL COMBINACIONAL CIRCUITO Variables de entrada DIGITAL COMBINACIONAL Variables de entrada DEA Variable de salida de emisor o surtidor abierto Variable de salida de emisor o surtidor abierto SALIDA DE EMISOR O SURTIDOR ABIERTO La etapa de salida de emisor o surtidor abierto (Open emitter or open source) posee un único dispositivo electrónico activo que tiene un terminal unido al polo positivo de la alimentación y el otro al aire. Este tipo de salida se identifica mediante un rombo que posee un segmento horizontal en el vértice superior. 45 Escuelas Técnicas de Ingenieros Universidad de Vigo Departamento de Tecnología Electrónica Electrónica Digital: Álgebra de Boole CIRCUITO DE SALIDA DE LAS PUERTAS LÓGICAS +VC Tipo de bloque funcional BLOQUE FUNCIONAL COMBINACIONAL CIRCUITO Variables de entrada DIGITAL DEA COMBINACIONAL R Variable de salida con carga pasiva en el emisor o en el surtidor Variables de entrada Variable de salida con carga pasiva en el emisor o en el surtidor SALIDA CON CARGA PASIVA EN EL EMISOR O SURTIDOR La etapa de salida con carga pasiva en el emisor o surtidor posee un único dispositivo electrónico activo que tiene un terminal unido al polo positivo de la alimentación y el otro a una resistencia (Pull-down resistor) conectada al polo negativo de la alimentación. Este tipo de salida se identifica mediante un rombo que posee un segmento horizontal en el vértice superior y otro en la diagonal horizontal. 46